## Intel<sup>®</sup> Firmware Support Package for 3rd Generation Intel<sup>®</sup> Core<sup>™</sup> Processors with Mobile Intel<sup>®</sup> HM76/QM77 Express Chipsets

**Integration Guide**

February 2014

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2014, Intel Corporation. All rights reserved.

## **Contents**

| 1 | Introdu<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | Purpose .<br>Intelligen<br>Intended<br>Related D<br>Conventio | 6<br>t Systems and Embedded Ecosystem Overview                                                                                                         |

|---|---------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | FSP Ov<br>2.1<br>2.2                              | Design Pł                                                     | nilosophy                                                                                                                                              |

| 3 | FSP Int<br>3.1                                    |                                                               | 9 ons Used in this Document                                                                                                                            |

| 4 | Boot Fl                                           | low                                                           |                                                                                                                                                        |

| 5 | FSP Bir<br>5.1                                    | FSP Head<br>5.1.1                                             | at                                                                                                                                                     |

| 6 | FSP In                                            | terface (FS                                                   | эр Арі)14                                                                                                                                              |

|   | 6.1<br>6.2<br>6.3<br>6.4                          | Entry-Poi<br>Exit Conv<br>TempRan<br>6.4.1<br>6.4.2           | nt Calling Assumptions14nt Calling Convention14ention15InitEntry15Prototype16Parameters16Related Definitions166.4.3.1Return Values6.4.3.2Sample Code17 |

|   | 6.5                                               | FspInitEn<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4                 | Description19try19Prototype19Parameters20Related Definitions20Return Values22Sample Code22Enabling Fast Boot24Description27                            |

| 7          | FSP O                             | Dutput                                                                                       |    |

|------------|-----------------------------------|----------------------------------------------------------------------------------------------|----|

|            | 7.1                               | Boot Loader Temporary Memory Data HOB                                                        |    |

|            | 7.2                               | Non-Volatile Storage HOB                                                                     |    |

|            | 7.3                               | HOB Sample Code                                                                              |    |

|            |                                   | <ul><li>7.3.1 Hob Infrastructure Sample Code</li><li>7.3.2 Hob Parsing Sample Code</li></ul> |    |

|            |                                   | <ul><li>7.3.2 Hob Parsing Sample Code</li><li>7.3.3 GUID HOB Sample Code</li></ul>           |    |

| 8          | FSP C                             | Configuration Firmware File                                                                  |    |

| 9          | Tools.                            |                                                                                              |    |

| 10         | Other                             | Host Boot Loader Concerns                                                                    |    |

|            | 10.1                              | Power Management                                                                             |    |

|            | 10.2                              | Bus Enumeration                                                                              |    |

|            | 10.3                              | Security                                                                                     |    |

|            | 10.4                              | 64-bit Long Mode                                                                             |    |

|            | 10.5                              | Pre-OS Graphics                                                                              |    |

| Appendix A | – HOB Parsing Sample Code3        |                                                                                              | 35 |

| Appendix B | - Sample Code to Find FSP Header5 |                                                                                              | 51 |

| Appendix C | – Data                            | a Structure for Memory Down                                                                  |    |

|            | C.1                               | Sample Code                                                                                  | 57 |

## **Revision History**

| Date          | Revision | Description             |  |

|---------------|----------|-------------------------|--|

| February 2014 | 1.0      | Initial public release. |  |

§

## 1.1 Purpose

The purpose of this document is to describe the steps required to integrate the FSP into a boot loader solution.

## 1.2 Intelligent Systems and Embedded Ecosystem Overview

Contrasting the PC ecosystem where hardware and software architecture are following a set of industry standards, the Intelligent Systems (embedded) ecosystem often does not adhere to the same industry standards. Design engineers for Intelligent Systems and Embedded Systems frequently combine components from different vendors with a set of very distinct functions in mind.

The criteria for picking the right boot loader are often based on boot speed and code size. The boot loader also frequently has close ties with the OS from a functionality perspective. To give freedom to customers to choose the best boot loader for their applications, Intel provides the Firmware Support Package (FSP) to satisfy the needs of design engineers.

## 1.3 Intended Audience

This document is targeted at all platform and system developers who need to consume FSP binaries in their boot loader solutions. This includes, but is not limited to: system BIOS developer, boot loader developer, system integrators, as well as end users.

## 1.4 Related Documents

- Platform Initialization (PI) Specification located at <u>http://www.uefi.org/specifications/</u>.

- Intel<sup>®</sup> Firmware Support Package: Introduction Guide available at <u>www.intel.com/fsp</u>

- Binary Configuration Tool for Intel<sup>®</sup> Firmware Support Package available at <u>www.intel.com/fsp</u>

## 1.5 Conventions

To illustrate some of the points better, the document will use code snippets. The code snippets follow **the GNU C Compiler** and **GNU Assembler** syntax.

## 1.6 Acronyms and Terminology

| BSP     | Boot Strap Processor                                     |

|---------|----------------------------------------------------------|

| BWG     | BIOS Writer's Guide                                      |

| CRB     | Customer Reference Board                                 |

| FSP     | Firmware Support Package                                 |

| FSP API | Firmware Support Package Interface                       |

| FWG     | Firmware Writer's Guide                                  |

| IVI     | In Vehicle Infotainment                                  |

| NBSP    | Node BSP                                                 |

| RSM     | Resume to OS from SMM                                    |

| SBSP    | System BSP                                               |

| SMI     | System Management Interrupt                              |

| SMM     | System Management Mode                                   |

| TSEG    | Memory Reserved at the Top of Memory to be used as SMRAM |

## 2 FSP Overview

## 2.1 Design Philosophy

Intel recognizes that it holds the key programming information that is crucial for initializing Intel silicon. After Intel provides the key information, most experienced firmware engineers can make the rest of the system work by studying specifications, porting guides, and reference code.

## 2.2 Technical Overview

The Intel<sup>®</sup> Firmware Support Package (FSP) provides chipset and processor initialization in a format that can easily be incorporated into many existing boot loaders.

The FSP will perform all the necessary initialization steps as documented in the BWG including initialization of the CPU, memory controller, chipset and certain bus interfaces, if necessary.

FSP is not a stand-alone boot loader; therefore it needs to be integrated into a host boot loader to carry out other boot loader functions, such as: initializing non-Intel components, conducting bus enumeration, and discovering devices in the system and all industry standard initialization.

# 3 FSP Integration

The FSP binary can be integrated easily into many different boot loaders, such as Coreboot, etc. and also into embedded OS directly.

Below are some required steps for the integration:

Customizing

The static FSP configuration parameters are part of the FSP binary and can be customized by external tools that will be provided by Intel.

Rebasing

The FSP is not Position Independent Code (PIC) and the whole FSP has to be rebased if it is placed at a location which is different from the preferred address specified during building the FSP.

• Placing

Once the FSP binary is ready for integration, the boot loader build process needs to be modified to place this FSP binary at the specific rebasing location identified above.

• Interfacing

The boot loader needs to add code to setup the operating environment for the FSP, call the FSP with the correct parameters and parse the FSP output to retrieve the necessary information returned by the FSP.

### 3.1 Assumptions Used in this Document

Because the 3rd Generation Intel<sup>®</sup> Core<sup>™</sup> Processors with Mobile Intel<sup>®</sup> HM76/QM77 Express Chipsets FSP is built with a preferred base address of 0xFFF80000, the FSP binary is assumed to be placed at the same address as part of the boot loader build.

# 4 **Boot Flow**

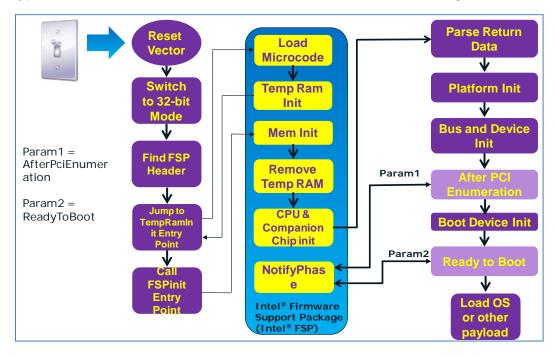

The figure below shows the boot flow from the reset vector to the OS handoff for a typical boot loader. The APIs are described in more detail in the following sections.

## 5 **FSP Binary Format**

The FSP is distributed in binary format. The FSP binary contains an FSP specific **FSP\_INFORMATION\_HEADER** structure, the initialization code/data needed by the Intel Silicon supported by the FSP and a configuration region that allows the boot loader developer to customize some of the settings through a tool provided by Intel.

## 5.1 **FSP Header**

The FSP header conveys the information required by the boot loader to interface with the FSP binary such as providing the addresses for the entry points, configuration region address, etc.

| Byte<br>Offset | Size<br>in<br>Bytes | Field           | Description                                                                                                                                                                                                                                                                                                                                         |

|----------------|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | 4                   | Signature       | 'FSPH'. Signature for the FSP Information Header.                                                                                                                                                                                                                                                                                                   |

| 4              | 4                   | HeaderLength    | Length of the header                                                                                                                                                                                                                                                                                                                                |

| 8              | 3                   | Reserved        | Reserved                                                                                                                                                                                                                                                                                                                                            |

| 11             | 1                   | HeaderRevision  | Revision of the header.                                                                                                                                                                                                                                                                                                                             |

| 12             | 4                   | ImageRevision   | Revision of the FSP Binary.<br>The ImageRevision can be decoded as follows<br>07 - Minor Version<br>815 - Major Version<br>1631 - Reserved                                                                                                                                                                                                          |

| 16             | 8                   | Image Id        | 8-byte signature string that will help match the FSP Binary to a supported hardware configuration.                                                                                                                                                                                                                                                  |

| 24             | 4                   | ImageSize       | Size of the entire FSP Binary.                                                                                                                                                                                                                                                                                                                      |

| 28             | 4                   | ImageBase       | FSP binary preferred base address. If the FSP binary will be located at the address different from the preferred address, the rebasing tool is required to relocate the base before the FSP binary integration.<br>For the 3rd Generation Intel <sup>®</sup> Core <sup>™</sup> Processors with Mobile Intel <sup>®</sup> HM76/QM77 Express Chipsets |

|                |                     |                 | FSP, the default ImageBase is oxFFF80000.                                                                                                                                                                                                                                                                                                           |

| 32             | 4                   | ImageAttribute  | Attributes of the FSP binary. This field is not currently used.                                                                                                                                                                                                                                                                                     |

| 36             | 4                   | CfgRegionOffset | Offset of the configuration region. This offset is relative to the FSP binary base address.                                                                                                                                                                                                                                                         |

| 40             | 4                   | CfgRegionSize   | Size of the configuration region.                                                                                                                                                                                                                                                                                                                   |

| Byte<br>Offset | Size<br>in<br>Bytes | Field                  | Description                                                                                 |

|----------------|---------------------|------------------------|---------------------------------------------------------------------------------------------|

| 44             | 4                   | ApiEntryNum            | Number of API Entries this FSP supports. The current design supports 3 APIs as given below. |

| 48             | 4                   | TempRamInitEntryOffset | The offset for the API to setup a temporary stack till the memory is initialized.           |

| 52             | 4                   | FspInitEntryOffset     | The offset for the API to initialize the CPU and the Chipset (SOC).                         |

| 56             | 4                   | NotifyPhaseEntryOffset | The offset for the API to inform the FSP about the different stages in the boot process.    |

| 60             | 4                   | Reserved               | Reserved                                                                                    |

### 5.1.1 Finding the FSP Header

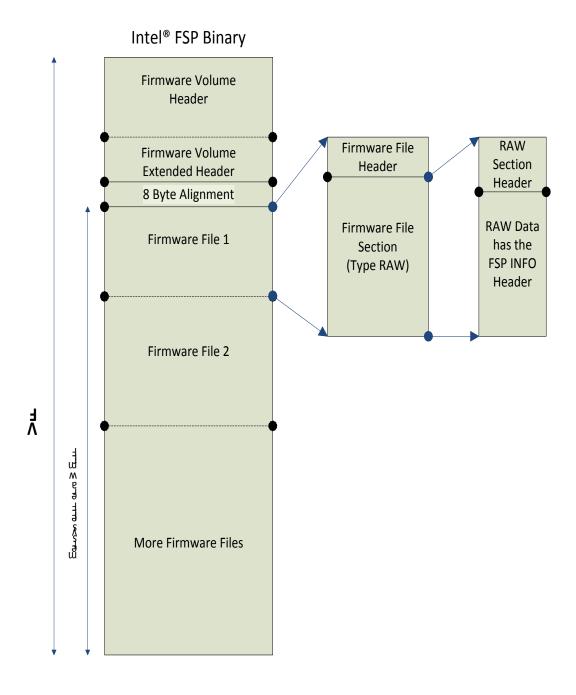

The FSP binary follows the UEFI Platform Initialization Firmware Volume Specification format. The Firmware Volume (FV) format is described in the *Platform Initialization* (*PI) specification - Volume 3: Shared Architectural Elements* specification and can be downloaded from <a href="http://www.uefi.org/specifications/">http://www.uefi.org/specifications/</a>

FV is a way to organize/structure binary components and enables a standardized way to parse the binary and handle the individual binary components that make up the FV.

The FSP\_INFORMATION\_HEADER is a firmware file and is placed as the **first** firmware file within the firmware volume. All firmware files will have a GUID that can be used to identify the files, including the FSP Header file. The FSP header firmware file GUID is defined as **912740BE-2284-4734-B971-84B027353F0C**.

The boot loader can find the offset of the FSP header within the FSP binary by the following steps described below:

- Use EFI\_FIRMWARE\_VOLUME\_HEADER to parse the FSP FV header and skip the standard and extended FV header.

- The EFI\_FFS\_FILE\_HEADER with the FSP\_FFS\_INFORMATION\_FILE\_GUID is located at the 8-byte aligned offset following the FV header.

- The EFI\_RAW\_SECTION header follows the FFS File Header.

- Immediately following the EFI\_RAW\_SECTION header is the raw data. The format of this data is defined in the FSP\_INFORMATION\_HEADER structure.

- Please refer to Appendix B for a sample code snippet which does the above steps in a stackless environment.

#### 5.1.2 FSP Header Offset

To simplify the integration of the FSP binary with a boot loader, the offset of the FSP header will be provided with the FSP binary documentation. In this case, the boot loader may choose to skip the generic algorithm to find the FSP header as described above, but instead use the hardcoded value for the FSP header offset. This approach is easier to implement from the boot loader side.

For the 3rd Generation Intel<sup>®</sup> Core<sup>™</sup> Processors with Mobile Intel<sup>®</sup> HM76/QM77 Express Chipsets FSP, the FSP header is placed at an offset of **0x94**. So, for example, if the FSP binary is placed at **0xFFF80000** after the final build, the FSP header can be located at **0xFFF80094**. This implies that

- 1. The offset of the TempRamInitEntry can be found at **0xFFF800C4**

- 2. The offset of the FspInitEntry can be found at **0xFFF800C8**

- 3. The offset of the NotifyPhaseEntry can be found at **0xFFF800CC**

# 6 FSP Interface (FSP API)

## 6.1 Entry-Point Calling Assumptions

There are some requirements regarding the operating environment for FSP execution. It is the responsibility of the boot loader to set up this operating environment before calling the FSP API. These conditions have to be met before calling any entry point or the behavior is not determined. These conditions include:

- System is in flat 32-bit mode.

- Both the code and data selectors should have full 4GB access range.

- Interrupts should be turned off.

- The FSP API should be called only by the System BSP, unless otherwise noted.

Other requirements needed by individual FSP API will be covered in their respective sections.

## 6.2 Entry-Point Calling Convention

All FSP APIs defined in the FSP information header are 32-bit only. The FSP API interface is similar to the default C \_cdecl convention. Like the default C \_cdecl convention, with the FSP API interface:

- All parameters are pushed onto the stack in a right-to-left order before the API is called.

- The calling function needs to clean the stack up after the API returns.

- The return value is returned in the EAX register. All the other registers are preserved.

There are, however, a couple of notable exceptions with the FSP API interface convention. Please refer to individual API descriptions for any special notes and these exceptions.

## 6.3 Exit Convention

- The TempRamInit API will preserve all general purpose registers except EAX, ECX, and EDX. Because this FSP API is executing in a stackless environment, the floating point registers may be used by the FSP to save/return other general purpose registers to the boot loader.

- The FspInit and the FspNotify interfaces will preserve all the general purpose registers except "eax". The return status will be passed back through the eax register.

- The FSP reserves some memory for its internal use and the memory region that is used by the FSP will be passed back though a HOB. The boot loader is expected to not to use this memory except to parse the HOB output. The boot loader is also expected to mark this memory as reserved when constructing the memory map information to be passed to the OS.

## 6.4 TempRamInitEntry

This FSP API is called soon after coming out of reset and before memory and stack are available. This FSP API will load the microcode update, enable code caching for the region specified by the boot loader and also setup a temporary stack to be used till main memory is initialized.

A hardcoded stack can be setup with the following values and the "esp" register initialized to point to this hardcoded stack.

- 1. The return address where the FSP will return control after setting up a temporary stack

- 2. A pointer to the input parameter structure

However, since stack is in ROM and not writeable, this FSP API cannot be called using the "call" instruction, but needs to be jumped to. This API should be called only once after the system comes out of the reset, and it must be called before any other FSP APIs. The system needs to go through a reset cycle before this API can be called again. Otherwise, unexpected results may occur.

6.4.1 Prototype

typedef

FSP\_STATUS

(FSPAPI \*FSP\_TEMP\_RAM\_INIT) (

IN FSP\_TEMP\_RAM\_INIT\_PARAMS \*TempRamInitParamPtr

);

#### 6.4.2 Parameters

#### TempRaminitParamPtr

Address pointer to the FSP\_TEMP\_RAM\_INIT\_PARAMS structure. The structure definition is provided below under Related Definitions. The structure has a pointer to the base of a code region and the size of it. The FSP enables code caching for this region. Enabling code caching for this region should not take more than one MTRR pair. The structure also has a pointer to a microcode region and its size. The microcode region may have multiple microcodes packed together one after the other and the FSP will try to load all the microcodes that it finds in the region that are compatible with the silicon it is supporting.

This microcode region will be remembered by FSP so that it can be used to load microcode for all APs later on during the FspInit API call.

#### 6.4.3 Related Definitions

#### typedef struct {

| UINT32 | <i>MicrocodeRegionBase,</i> |

|--------|-----------------------------|

| UINT32 | MicrocodeRegionLength,      |

| UINT32 | CodeRegionBase,             |

| UINT32 | CodeRegionLength            |

|        |                             |

} FSP\_TEMP\_RAM\_INIT\_PARAMS;

#### 6.4.3.1 Return Values

If this function is successful, the FSP initializes the ECX and EDX registers to point to a temporary but writeable memory range available to the boot loader and returns with FSP\_SUCCESS in register EAX. Register ECX points to the start of this temporary memory range and EDX points to the end of the range. Boot loader is free to use the whole range described. Typically the boot loader can reload the ESP register to point to the end of this returned range so that it can be used as a standard stack.

*Note:* This returned range is just a sub-region of the whole temporary memory initialized by the processor. FSP maintains and consumes the remaining temporary memory. It is important for the boot loader not to access the temporary memory beyond the returned boundary.

| FSP_SUCCESS           | Temp RAM was initialized successfully. ESP register will be initialized as described below. |

|-----------------------|---------------------------------------------------------------------------------------------|

| FSP_INVALID_PARAMETER | Input parameters are invalid.                                                               |

| FSP_NOT_FOUND         | No valid microcode was found in the microcode region.                                       |

| FSP_UNSUPPORTED       | The FSP calling conditions were not met.                                                    |

#### 6.4.3.2 Sample Code

```

.global basic_init

basic_init:

.

•

•

#

# Parse the FV to find the FSP INFO Header

#

lea

findFspHeaderStack, %esp

find_fsp_info_header

jmp

findFspHeaderDone:

# save fsp header address in

mov

%eax, %ebp

ebp

0x30(%ebp), %eax

# TempRamInit offset entry in

mov

the header

add

0xlc(%ebp), %eax

# add the FSP base to get the

API address

lea

tempRamInitStack, %esp

# initialize to a rom stack

#

# call FSP PEI to setup temporary Stack

#

jmp

*%eax

temp_RamInit_done:

addl $4, %esp

$0, %eax

cmp

continue

iΖ

```

```

#

# TempRamInit failed, dead loop

#

jmp

.

continue:

#

# Save FSP_INFO_HEADER in ebx

#

mov

%ebp, %ebx

#

# setup bootloader stack

# ecx: stack base

# edx: stack top

#

lea

-4(%edx), %esp

#

# call C based function to initialize meomry and chipset. Pass

# the FSP INFO Header address as a parameter

#

%ebx

push

call

early_init

#

# should never return here

#

jmp .

.align 4

findFspHeaderStack:

.long findFspHeaderDone

tempRamInitParams:

# Microcode base address

.long _ucode_base

.long _ucode_size

# Microcode size

.long 0xfff80000

# Code Region Base

.long 0x00040000

# Code Region Length

tempRamInitStack:

# return address

.long temp_RamInit_done

.long tempRamInitParams

# pointer to parameters

```

Note: early\_init(FSP\_INFO\_HEADER \*fsp\_info) is described in section 6.5.5.

#### 6.4.4 Description

The entry to this function is in a stackless/memoryless environment. After the boot loader completes its initial steps, it finds the address of the FSP INFO HEADER and then from the header finds the offset of the TempRamInit function. It then converts the offset to an absolute address by adding the base of the FSP binary and calls the TempRamInit function.

This temporary memory is intended to be primarily used by the boot loader as a stack. After this stack is available, the boot loader can switch to using C functions. This temporary stack should be used to do only the minimal initialization that needs to be done before memory can be initialized by the next call into the FSP.

The FSP initializes the ECX and EDX registers to point to a temporary but writeable memory range. Register ECX points to the start of this temporary memory range and EDX points to the end of the range. The size of the temporary stack for the platform can be calculated by taking the range between EDX and ECX.

## 6.5 FspInitEntry

This FSP API is called after TempRamInitEntry. This FSP API initializes the memory, the CPU and the chipset to enable normal operation of these devices. This FSP API accepts a pointer to a data structure that will be platform dependent and defined for each FSP binary. This will be documented with each FSP release.

The boot loader provides a continuation function as a parameter when calling FspInit. After FspInit completes its execution, it will not return to the boot loader from where it was called, but instead will return control to the boot loader by calling the continuation function.

#### 6.5.1 Prototype

```

typedef

FSP_STATUS

(FSPAPI *FSP_FSP_INIT) (

INOUT FSP_INIT_PARAMS *F;

)

```

\*FspInitParamPtr);

#### 6.5.2 Parameters

FspInitParamPtr

Address pointer to the FSP\_INIT\_PARAMS structure

## 6.5.3 Related Definitions

| typedef struct {              |            |                   |

|-------------------------------|------------|-------------------|

| VOID                          | *NvsBuffer | Ptr;              |

| VOID                          | *RtBufferF | Ptr;              |

| CONTINU                       | ATION_PROC | ContinuationFunc; |

| <pre>} FSP_INIT_PARAMS;</pre> |            |                   |

| NvsBufferPtr     | Pointer to the non-volatile storage data buffer.                |

|------------------|-----------------------------------------------------------------|

| RtBufferPtr      | Pointer to the runtime data buffer.                             |

| ContinuationFunc | Pointer to a continuation function provided by the boot loader. |

typedef VOID (\* CONTINUATION\_PROC)(

IN FSP\_STATUS Status,

IN VOID \*HobListPtr

);

| Status       | Status of the FSP Init API.                                        |

|--------------|--------------------------------------------------------------------|

| HobBufferPtr | Pointer to the HOB data structure defined in the PI specification. |

The FSP\_INIT\_RT\_BUFFER for the 3rd Generation Intel<sup>®</sup> Core<sup>™</sup> Processors with Mobile Intel<sup>®</sup> HM76/QM77 Express Chipsets FSP is defined as below.

```

typedef struct {

UINT32

*StackTop;

UINT32

BootMode;

} FSP_INIT_RT_COMMON_BUFFER;

typedef struct {

const MEM CONFIG

*MemoryConfig;

} FSP_INIT_RT_PLATFORM_BUFFER;

typedef struct {

UINT8

HTEnable;

UINT8

TurboEnable;

UINT8

MemoryDownEnable;

UINT8

FastBootEnable;

} PLATFORM_CONFIG;

typedef struct {

const

PLATFORM_CONFIG

*PlatformConfig;

} FSP_INIT_RT_CONFIG_BUFFER;

typedef struct {

FSP_INIT_RT_COMMON_BUFFER

Common;

FSP_INIT_RT_CONFIG_BUFFER

PlatformConfiguration;

FSP_INIT_RT_PLATFORM_BUFFER RtPlatform;

} FSP_INIT_RT_BUFFER;

```

MEM\_CONFIG is the data structure for Memory Down. Refer Appendix C for its structure definitions.

#### 6.5.4 Return Values

| FSP_SUCCESS           | FSP execution environment was initialized successfully. |

|-----------------------|---------------------------------------------------------|

| FSP_INVALID_PARAMETER | Input parameters are invalid.                           |

| FSP_UNSUPPORTED       | The FSP calling conditions were not meet.               |

| FSP_DEVICE_ERROR      | FSP initialization failed                               |

#### 6.5.5 Sample Code

{

.

.

typedef VOID (\* CONTINUATION\_PROC)(EFI\_STATUS Status, VOID

\*HobListPtr);

const PLATFORM\_CONFIG CpuConfigData = {0x01, 0x00, 0x00, 0x00};

typedef struct {

void \*NvsBufferPtr;

void \*RtBufferPtr;

CONTINUATION\_PROC ContinuationFunc;

} FSP\_INIT\_PARAMS;

#define FSPAPI \_\_attribute\_\_((cdecl))

```

typedef FSP_STATUS (FSPAPI *FSP_FSP_INIT) (FSP_INIT_PARAMS

*FspInitParamPtr);

```

#define BOOTLOADER\_STACKTOP 0x98000 // Porting required

void early\_init (FSP\_INFORMATION\_HEADER \*fsp\_info)

| uint32_t                    | FspInitEntry;  |

|-----------------------------|----------------|

| FSP_FSP_INIT                | FspInitApi;    |

| volatile FSP_INIT_PARAMS    | FspInitParams; |

| volatile FSP_INIT_RT_BUFFER | FspRtBuffer;   |

}

{

```

memset((void*)&FspRtBuffer, 0, sizeof(FSP_INIT_RT_BUFFER));

FspRtBuffer.Common.StackTop = BOOTLOADER_STACKTOP;

FspRtBuffer.RtPlatform.MemoryConfig =NULL;

FspRtBuffer.PlatformConfiguration.PlatformConfig =

&CpuConfigData;

FspInitParams.NvsBufferPtr = 0;

FspInitParams.RtBufferPtr = (FSP_INIT_RT_BUFFER *)&FspRtBuffer;

FspInitParams.ContinuationFunc =

(CONTINUATION_PROC)ContinuationFunc;

FspInitApi = (FSP_FSP_INIT)(fsp_info->ImageBase + fsp_info

->FspInitEntry);

FspInitApi(&FspInitParams);

/* Should never return. Control will continue from

ContinuationFunc */

while (1);

void ContinuationFunc (EFI STATUS Status, VOID *HobListPtr)

/* Check status for -1, indicating that we need to do a reset */

if (Status == 0xFFFFFFFF)

{

/* Trigger the reset */

outb(0x0cf9, 0x06);

/* Should never return */

while (1);

}

```

```

/* Update global variables */

FspHobListPtr = HobListPtr;

/* Get the pointer to the FSP header the same way as in

basic_init */

asm ("call find_fsp_info_header; movl %%eax, %0" : "=r"

(fsp_info_header) :);

/* Continue the boot */

advancedInit ();

/* Should never return */

while (1);

}

```

#### 6.5.6 Enabling Fast Boot

The shaded lines in the sample code below highlight the things that need to be changed to enable fast boot in the bootloader. First, the FastBootEnable field needs to be set to TRUE in the PLATFORM\_CONFIG structure:

```

// Platform Configuration

const PLATFORM_CONFIG PlatformConfig = {

TRUE, // Hyperthreading

FALSE, // Turbo Mode

FALSE, // Memory Down

TRUE, // Fast Boot

};

```

The boot loader should implement code to save and read back the HOB data to/from non-volatile storage. The sample code below shows an example implementation for passing the HOB data back to the FSP thru the NvsBufferPtr pointer. For the first boot, the data buffer that this pointer points to should contain either all zeroes or all 0xFFs so that the FSP can recognize it as being uninitialized. For subsequent boots, the data buffer that this pointer points to should contain valid memory training data that was generated by the FSP during the first boot and was saved by boot loader to the data buffer in non-volatile storage.

```

void early_init (FSP_INFO_HEADER *fsp_info)

ł

FSP_FSP_INIT

FspInitEntry;

```

```

FSP_INIT_PARAMS

FspInitParams;

FSP_INIT_RT_BUFFER

FspRtBuffer;

*NvsBufferPtr;

VOID

```

... // Some init code.

```

// Get pointer to saved NVSTORAGE HOB data

NvsBufferPtr = ... // Platform-specific

memset((void*)&FspRtBuffer, 0, sizeof(FSP_INIT_RT_BUFFER));

FspRtBuffer.Common.StackTop = &_stack_top;

FspRtBuffer.PlatformConfiguration.PlatformConfig =

&PlatformConfig;

FspRtBuffer.Platform.MemoryConfig = NULL;

FspInitParams.NvsBufferPtr = NvsBufferPtr;

FspInitParams.RtBufferPtr = (FSP_INIT_RT_BUFFER *)&FspRtBuffer;

FspInitParams.ContinuationFunc =

(CONTINUATION PROC)ContinuationFunc;

FspInitEntry = (FSP_FSP_INIT)(fsp_info->ImageBase + fsp_info-

>FspInitEntry);

FspInitEntry(&FspInitParams);

/* Should never return. Control will continue from

ContinuationFunc */

while (1);

}

After FspInitEntry is done, control is returned to the boot

loader via the ContinuationFunc function, which is passed a

pointer to the HOB list. The boot loader should save this pointer

for use later.

volatile void *FspHobListPtr;

void ContinuationFunc (EFI STATUS Status, VOID *HobListPtr)

{

. . .

/* Update global variables */

```

```

FspHobListPtr = HobListPtr;

```

```

/* Continue the boot */

advancedInit ();

/* Should never return */

while (1);

```

. . .

}

One of the HOBs in the HOB list contains the Non-Volatile Storage data, which includes the memory training data required for fast boot. It's the data from this HOB that must be saved into non-volatile storage to be used in subsequent boots. This data is extracted from the HOB list with the following function, which depends upon values and functions that are defined in fsphob.h and are implemented fsphob.c, both of which are included with the files that are packaged with the FSP.

```

#include "fsphob.h"

```

```

void GetFspHobDataForNVStorage(

VOID

**ppHobData,

*pHobDataSize

uint16_t

)

{

EFI GUID

Guid =

FSP NON VOLATILE STORAGE HOB GUID;

uint8 t

*Hob;

EFI_HOB_GENERIC_HEADER *HobHdr;

Hob = GetFirstGuidHob(&Guid);

if (!Hob) {

*ppHobData = NULL;

*pHobDataSize = 0;

} else {

*ppHobData = (VOID *)GET_GUID_HOB_DATA(Hob);

HobHdr = (EFI_HOB_GENERIC_HEADER *)Hob;

*pHobDataSize = GET_GUID_HOB_DATA_SIZE(HobHdr);

}

}

```

This function is called from the boot loader after everything else is successfully initialized, right before calling FspNotifyPhase(EnumInitPhaseReadyToBoot), and the HOB data is saved to non-volatile storage. Sample code below shows that this function is called inside advancedInit.

```

void advancedInit()

{

VOID *HobData;

uint16_t HobDataSize;

...

/* NVS data to save */

GetFspHobDataForNVStorage(&HobData, &HobDataSize);

/* Check result */

if ((HobData != NULL) && (HobDataSize > 0))

{

/* Check if data will fit in available NV storage */

if (HobDataSize <= NVRAM_SIZE) // Platform-specific

{

/*

}

}

```

```

/* Save NVSTORAGE HOB data

... // Platform-specific

}

}

/* Notify FSP for ReadyToBoot */

FspNotifyPhase(EnumInitPhaseReadyToBoot);

...

}

```

#### 6.5.7 Description

One of the data that will be part of the FSP\_INIT\_PARAMS. RtBufferPtr will be the "StackTop". This will pass the address of the StackTop where the boot loader wants to establish the stack once memory is initialized and available for use. ContinuationFunc is a function entry point that will be jumped to at the end of the FspInit() execution to transfer control back to the boot loader. Please note the FspInit API will initialize the permanent memory and switch the stack from temporary to permanent memory as specified by StackTop. Sometimes switching stack in a function can cause some unexpected execution results because the compiler is not aware of the stack change during runtime and the precompiled code may still refer to the old stack for data and pointers. A stack switch will then require assembly code to patch up the data for the new stack location, which may lead to compatibility issues. To avoid such possible compatibility issues introduced by different compilers and ease the integration of FSP with a boot loader, the API will use the "ContinuationFunction" parameter to continue the boot loader execution flow rather than return as a normal C function. Although this API will be called as a normal C function, it will never return to one.

The FSP will need to get some parameters from the boot loader when it's initializing the silicon. These parameters are passed from the boot loader to the FSP through the RtBuffer structure pointer.

The FSP may need to initialize memory under special circumstances, such as during an S3 resume and fast boot mode. This set of parameters will be returned by the FSP to the boot loader during a normal boot. The boot loader is expected to store these parameters in a non-volatile memory, comparable to SPI flash, and return a pointer to this structure (through NvsBufferPtr) when it is requesting the FSP to initialize the silicon under these special circumstances.

During execution the FSP will build a series of data structures containing information useful to the boot loader, such as information on system memory.

This API should be called only once after the TempRamInit API.

# 7 FSP Output

The FSP builds a series of data structures called the Hand-Off-Blocks (HOBs) as it progresses through initializing the silicon. These data structures conform to the HOB format as described in the *Platform Initialization (PI) specification - Volume 3: Shared Architectural Elements* specification and can be downloaded from <a href="http://www.uefi.org/specifications/">http://www.uefi.org/specifications/</a>

The user of the FSP binary is strongly encouraged to go through the specification mentioned above to understand the HOB design details and create a simple infrastructure to parse the HOBs, because the same infrastructure can be reused with different FSP across different platforms

It's left to the boot loader developer to decide on how to consume the information passed through the HOBs produced by the FSP. For example, even the specification mentioned above describes about 9 different HOBs; most of this information may not be relevant to a particular boot loader. For example, a boot loader design may be interested only in knowing the amount of memory populated and may not care about any other information.

The section below describes the GUID HOBs that are produced by the FSP. GUID HOB structures are non-architectural in the sense that the structure of the HOB needs is not defined in the HOB specifications. So the GUID and the data structure are documented below to enable the boot loader to consume these HOB data.

Please refer to the specification for details about the HOBs described in the *Platform Initialization (PI) specification - Volume 3: Shared Architectural Elements* specification.

## 7.1 Boot Loader Temporary Memory Data HOB

As described in the FspInit API, the system memory is initialized and the whole temporary memory is destroyed during this API call. However, the sub region of the temporary memory returned in the TempRamInit API may still contain boot loader-specific data, which might be useful for boot loader even after the FspInit call. So before destroying the temporary memory, all contents in this sub region is migrated to the permanent memory. FSP builds a boot loader temporary memory data HOB, which the boot loader can to access the data saved in the temporary memory after FspInit API if necessary. If the boot loader does not care about the previous data, this HOB can be simply ignored.

This HOB follows the EFI\_HOB\_GUID\_TYPE format with the name GUID defined as below:

#define FSP\_BOOTLOADER\_TEMPORARY\_MEMORY\_HOB\_GUID \

```

{ 0xbbcff46c, 0xc8d3, 0x4113, { 0x89, 0x85, 0xb9, 0xd4, 0xf3,

0xb3, 0xf6, 0x4e } ;

```

## 7.2 Non-Volatile Storage HOB

The NVS buffer that is used by FSP to initialize the silicon during S3 resume, fast boot mode, etc., is passed through a GUID HOB with a GUID HOB defined as below. The boot loader is expected to save the data in a non-volatile storage memory area and initialize the FspInit parameter properly when requesting special initialization sequences such as S3 resume, fast boot mode, etc.

This HOB follows the EFI\_HOB\_GUID\_TYPE format with the name GUID defined as below:

#define FSP\_NON\_VOLATILE\_STORAGE\_HOB\_GUID \

{ 0x721acf02, 0x4d77, 0x4c2a, { 0xb3, 0xdc, 0x27, 0xb, 0x7b, 0xa9, 0xe4, 0xb0 } ;;

### 7.3 HOB Sample Code

An example function using the HOB infrastructure and getting the memory information is provided below.

#### 7.3.1 Hob Infrastructure Sample Code

Please refer to the Appendix - A for sample code.

#### 7.3.2 Hob Parsing Sample Code

```

void

GetMemorySize (

UINT32

*LowMemoryLength,

void

*HobBufferPtr

)

{

EFI PEI HOB POINTERS

Hob;

*LowMemoryLength = 0x100000;

11

// Get the HOB list for processing

11

Hob.Raw = HobBufferPtr;

11

// Collect memory ranges

11

while (!END OF HOB LIST (Hob)) {

if (Hob.Header->HobType == EFI_HOB_TYPE_RESOURCE_DESCRIPTOR)

{

if (Hob.ResourceDescriptor->ResourceType ==

EFI_RESOURCE_SYSTEM_MEMORY) {

```

FSP Output

```

11

\ensuremath{{/}} Need memory above 1MB to be collected here

11

if (Hob.ResourceDescriptor->PhysicalStart >= 0x100000 &&

Hob.ResourceDescriptor->PhysicalStart <

(EFI_PHYSICAL_ADDRESS) 0x10000000) {

*LowMemoryLength += (UINT32) (Hob.ResourceDescriptor-

>ResourceLength);

}

}

}

Hob.Raw = GET_NEXT_HOB (Hob);

}

return;

}

void boot_loader_rom_stage_fn ()

{

.

.

.

/* call FSP PEI to setup MRC and other CS init */

.

.

.

/* Get the memory size by parsing the HOB returned from the FSP

* /

GetMemorySize (&LowMemoryLength, FspInitParams.HobBufferPtr);

•

.

.

}

```

### 7.3.3 GUID HOB Sample Code

```

void *

GetGuidHobData (

CONST EFI_GUID *Guid

)

{

VOID *GuidHob;

GuidHob = GetFirstGuidHob (Guid);

if (GuidHob == NULL) {

return NULL;

}

return (void *)GET_GUID_HOB_DATA (GuidHob);

}

```

# 8 FSP Configuration Firmware File

The FSP binary contains a configurable data region which will be used by the FSP during the initialization. Typically this is the default parameters used by the PEIMs in the FSP. The parameters can be statically customized using a separate tool as explained in the tools section. The tool will use a Binary Setting File (BSF) to understand the layout of the configuration region within the FSP.

## 9 Tools

A Binary Configuration Tool (BCT) will be provided with the FSP binary that can used on the FSP binary to allow a user to modify certain well defined configuration values in the FSP binary. The BCT will typically provide a graphical user interface (GUI). The Binary Configuration Tool (BCT) will be provided with separate documentation that explains the usage of the tool.

Other Host Boot Loader Concerns

# 10 Other Host Boot Loader Concerns

### 10.1 Power Management

Intel<sup>®</sup> FSP does not provide power management functions besides making power management features available to the host boot loader. ACPI is an independent component of the boot loader, and it will not be included in Intel<sup>®</sup> FSP.

### 10.2 Bus Enumeration

Intel<sup>®</sup> FSP will initialize the CPU and the companion chips to a state that all bus topology can be discovered by the host boot loader.

### 10.3 Security

Intel<sup>®</sup> FSP does not provide security features besides making security features available to the host boot loader.

## 10.4 64-bit Long Mode

Intel<sup>®</sup> FSP operates in 32-bit mode; it is the responsibility of the host boot loader to transition to 64-bit Long Mode if desired.

### 10.5 Pre-OS Graphics

Intel<sup>®</sup> FSP does not include graphics initialization function. For pre-OS graphics initialization solutions, please contact your Intel representative.

## Appendix A – HOB Parsing Sample Code

The sample code provided here was derived from the EDK2 source available for download at

http://sourceforge.net/apps/mediawiki/tianocore/index.php?title=EDK2

```

111

/// 8-byte unsigned value.

111

typedef unsigned long long UINT64;

111

/// 8-byte signed value.

111

typedef long long

INT64;

111

/// 4-byte unsigned value.

111

typedef unsigned int

UINT32;

111

/// 4-byte signed value.

111

typedef int

INT32;

111

/// 2-byte unsigned value.

111

typedef unsigned short

UINT16;

111

/// 2-byte Character. Unless otherwise specified all strings are

///\ stored in the UTF-16 encoding format as defined by Unicode

/// 2.1 and ISO/IEC 10646 standards.

111

typedef unsigned short

CHAR16;

111

/// 2-byte signed value.

111

typedef short

INT16;

111

/// Logical Boolean. 1-byte value containing 0 for FALSE or a 1

/// for TRUE. Other values are undefined.

111

typedef unsigned char

BOOLEAN;

111

/// 1-byte unsigned value.

111

```

```

typedef unsigned char

UINT8;

111

/// 1-byte Character

111

CHAR8;

typedef char

111

/// 1-byte signed value

111

typedef char

INT8;

typedef void

VOID;

typedef UINT64

EFI_PHYSICAL_ADDRESS;

typedef struct {

UINT32 Data1;

UINT16 Data2;

UINT16 Data3;

UINT8 Data4[8];

} EFI_GUID;

#define CONST const

#define STATIC static

#define TRUE ((BOOLEAN)(1==1))

#define FALSE ((BOOLEAN)(0==1))

static inline void DebugDeadLoop(void) {

for (;;);

}

#define FSPAPI __attribute__((cdecl))

#define EFIAPI __attribute__((cdecl))

#define _ASSERT(Expression) DebugDeadLoop()

#define ASSERT(Expression)

\backslash

do {

/

if (!(Expression)) {

/

_ASSERT (Expression);

\

}

} while (FALSE)

typedef UINT32 FSP_STATUS;

typedef UINT32 EFI_STATUS;

11

// HobType of EFI_HOB_GENERIC_HEADER.

11

#define EFI HOB TYPE MEMORY ALLOCATION 0x0002

#define EFI_HOB_TYPE_RESOURCE_DESCRIPTOR 0x0003

#define EFI_HOB_TYPE_GUID_EXTENSION

0x0004

```

```

#define EFI HOB TYPE UNUSED

0xFFFE

#define EFI_HOB_TYPE_END_OF_HOB_LIST

0xFFFF

111

/// Describes the format and size of the data inside the HOB.

/// All HOBs must contain this generic HOB header.

111

typedef struct {

111

/// Identifies the HOB data structure type.

111

UINT16

HobType;

111

/// The length in bytes of the HOB.

111

UINT16

HobLength;

111

/// This field must always be set to zero.

111

UINT32

Reserved;

} EFI_HOB_GENERIC_HEADER;

111

/// Enumeration of memory types introduced in UEFI.

///

typedef enum {

111

/// Not used.

111

EfiReservedMemoryType,

111

/// The code portions of a loaded application.

/// (Note that UEFI OS loaders are UEFI applications.)

111

EfiLoaderCode,

111

/// The data portions of a loaded application and the default

/// data allocation type used by an application to allocate

/// pool memory.

111

EfiLoaderData,

111

/// The code portions of a loaded Boot Services Driver.

111

EfiBootServicesCode,

111

/// The data portions of a loaded Boot Serves Driver, and the

/// default data allocation type used by a Boot Services Driver

/// to allocate pool memory.

111

EfiBootServicesData,

111

/// The code portions of a loaded Runtime Services Driver.

```

```

111

EfiRuntimeServicesCode,

111

/// The data portions of a loaded Runtime Services Driver and

/// the default data allocation type used by a Runtime Services

/// Driver to allocate pool memory.

111

EfiRuntimeServicesData,

111

/// Free (unallocated) memory.

111

EfiConventionalMemory,

111

/// Memory in which errors have been detected.

111

EfiUnusableMemory,

111

/// Memory that holds the ACPI tables.

111

EfiACPIReclaimMemory,

111

/// Address space reserved for use by the firmware.

111

EfiACPIMemoryNVS,

111

/// Used by system firmware to request that a memory-mapped IO

/// region be mapped by the OS to a virtual address so it can

/// be accessed by EFI runtime services.

111

EfiMemoryMappedIO,

111

/// System memory-mapped IO region that is used to translate

/// memory cycles to IO cycles by the processor.

111

EfiMemoryMappedIOPortSpace,

111

/// Address space reserved by the firmware for code that is

/// part of the processor.

111

EfiPalCode,

EfiMaxMemoryType

} EFI_MEMORY_TYPE;

111

/// EFI_HOB_MEMORY_ALLOCATION_HEADER describes the

/// various attributes of the logical memory allocation. The type

/// field will be used for subsequent inclusion in the UEFI

/// memory map.

111

```

```

typedef struct {

111

/// A GUID that defines the memory allocation region's type and

/// purpose, as well as other fields within the memory

/// allocation HOB. This GUID is used to define the additional

/// data within the HOB that may be present for the memory

/// allocation HOB. Type EFI_GUID is defined in

/// InstallProtocolInterface() in the UEFI 2.0 specification.

111

EFI GUID

Name;

111

/// The base address of memory allocated by this HOB. Type

/// EFI_PHYSICAL_ADDRESS is defined in AllocatePages() in the

/// UEFI 2.0specification.

111

EFI_PHYSICAL_ADDRESS MemoryBaseAddress;

111

/// The length in bytes of memory allocated by this HOB.

111

UINT64

MemoryLength;

111

/// Defines the type of memory allocated by this HOB. The

/// memory type definition follows the EFI_MEMORY_TYPE

/// definition. Type EFI MEMORY TYPE is defined in

/// AllocatePages() in the UEFI 2.0 specification.

111

EFI MEMORY TYPE

MemoryType;

111

/// Padding for Itanium processor family

111

UINT8

Reserved[4];

} EFI_HOB_MEMORY_ALLOCATION_HEADER;

111

/// Describes all memory ranges used during the HOB producer

/// phase that exist outside the HOB list. This HOB type

/// describes how memory is used, not the physical attributes of

/// memory.

111

typedef struct {

111

/// The HOB generic header. Header. HobType =

EFI_HOB_TYPE_MEMORY_ALLOCATION.

111

EFI HOB GENERIC HEADER

Header;

111

/// An instance of the EFI_HOB_MEMORY_ALLOCATION_HEADER that

/// describes the various attributes of the logical memory

/// allocation.

```

```

111

EFI_HOB_MEMORY_ALLOCATION_HEADER AllocDescriptor;

11

// Additional data pertaining to the "Name" Guid memory

// may go here.

11

} EFI_HOB_MEMORY_ALLOCATION;

111

/// The resource type.

111

typedef UINT32 EFI RESOURCE TYPE;

11

// Value of ResourceType in EFI_HOB_RESOURCE_DESCRIPTOR.

11

#define EFI_RESOURCE_SYSTEM_MEMORY

0x00000000

#define EFI_RESOURCE_MEMORY_MAPPED_IO

0x0000001

#define EFI_RESOURCE_IO

0x0000002

#define EFI_RESOURCE_FIRMWARE_DEVICE

0x0000003

#define EFI RESOURCE MEMORY MAPPED IO PORT 0x0000004

#define EFI_RESOURCE_MEMORY_RESERVED

0x0000005

#define EFI_RESOURCE_IO_RESERVED

0x0000006

#define EFI_RESOURCE_MAX_MEMORY_TYPE

0 \times 00000007

111

/// A type of recount attribute type.

111

typedef UINT32 EFI RESOURCE ATTRIBUTE TYPE;

11

// These types can be ORed together as needed.

11

// The first three enumerations describe settings

11

#define EFI_RESOURCE_ATTRIBUTE_PRESENT

0x0000001

#define EFI_RESOURCE_ATTRIBUTE_INITIALIZED

0x0000002

#define EFI RESOURCE ATTRIBUTE TESTED

0x0000004

11

// The rest of the settings describe capabilities

11

#define EFI_RESOURCE_ATTRIBUTE_SINGLE_BIT_ECC

0x0000008

#define EFI_RESOURCE_ATTRIBUTE_MULTIPLE_BIT_ECC

0x0000010

#define EFI RESOURCE ATTRIBUTE ECC RESERVED 1

0x0000020

#define EFI RESOURCE ATTRIBUTE ECC RESERVED 2

0x0000040

#define EFI_RESOURCE_ATTRIBUTE_READ_PROTECTED

0x0000080

#define EFI_RESOURCE_ATTRIBUTE_WRITE_PROTECTED

0x0000100

```

```

#define EFI_RESOURCE_ATTRIBUTE_EXECUTION_PROTECTED

0x00000200

#define EFI_RESOURCE_ATTRIBUTE_UNCACHEABLE

0x00000400

#define EFI_RESOURCE_ATTRIBUTE_WRITE_COMBINEABLE

0x00000800

#define EFI_RESOURCE_ATTRIBUTE_WRITE_THROUGH_CACHEABLE

0x00001000

#define EFI RESOURCE ATTRIBUTE WRITE BACK CACHEABLE

0x00002000

#define EFI RESOURCE ATTRIBUTE 16 BIT IO

0x00004000

#define EFI_RESOURCE_ATTRIBUTE_32_BIT_IO

0x00008000

#define EFI_RESOURCE_ATTRIBUTE_64_BIT_IO

0x00010000

#define EFI_RESOURCE_ATTRIBUTE_UNCACHED_EXPORTED

0x00020000

111

/// Describes the resource properties of all fixed,

/// nonrelocatable resource ranges found on the processor

/// host bus during the HOB producer phase.

111

typedef struct {

111

/// The HOB generic header. Header.HobType =

/// EFI HOB TYPE RESOURCE DESCRIPTOR.

111

EFI HOB GENERIC HEADER

Header;

111

/// A GUID representing the owner of the resource. This GUID is

///\ used by HOB consumer phase components to correlate device

/// ownership of a resource.

111

EFI_GUID

Owner;

111

/// The resource type enumeration as defined by

/// EFI_RESOURCE_TYPE.

111

EFI_RESOURCE_TYPE

ResourceType;

111

/// Resource attributes as defined by

/// EFI_RESOURCE_ATTRIBUTE_TYPE.

111

EFI RESOURCE ATTRIBUTE TYPE ResourceAttribute;

111

/// The physical start address of the resource region.

111

EFI_PHYSICAL_ADDRESS PhysicalStart;

111

/// The number of bytes of the resource region.

111

```

```

UINT64

ResourceLength;

} EFI_HOB_RESOURCE_DESCRIPTOR;

111

/// Allows writers of executable content in the HOB producer

/// phase to maintain and manage HOBs with specific GUID.

111

typedef struct {

111

/// The HOB generic header. Header.HobType =

/// EFI HOB TYPE GUID EXTENSION.

111

EFI_HOB_GENERIC_HEADER

Header;

111

/// A GUID that defines the contents of this HOB.

111

EFI_GUID

Name;

11

// Guid specific data goes here

11

} EFI_HOB_GUID_TYPE;

111

/// Union of all the possible HOB Types.

111

typedef union {

EFI HOB GENERIC HEADER

*Header;

EFI HOB MEMORY ALLOCATION

*MemoryAllocation;

EFI_HOB_RESOURCE_DESCRIPTOR

*ResourceDescriptor;

EFI_HOB_GUID_TYPE

*Guid;

UINT8

*Raw;

} EFI_PEI_HOB_POINTERS;

/**

Returns the type of a HOB.

This macro returns the HobType field from the HOB header for

the HOB specified by HobStart.

@param HobStart A pointer to a HOB.

@return HobType.

**/

#define GET_HOB_TYPE(HobStart) \

((*(EFI_HOB_GENERIC_HEADER **)&(HobStart))->HobType)

/**

Returns the length, in bytes, of a HOB.

This macro returns the HobLength field from the HOB header for

the HOB specified by HobStart.

```

```

@param HobStart A pointer to a HOB.

@return HobLength.

**/

#define GET_HOB_LENGTH(HobStart) \

((*(EFI_HOB_GENERIC_HEADER **)&(HobStart))->HobLength)

/ * *

Returns a pointer to the next HOB in the HOB list.

This macro returns a pointer to HOB that follows the

HOB specified by HobStart in the HOB List.

@param HobStart A pointer to a HOB.

@return A pointer to the next HOB in the HOB list.

**/

#define GET_NEXT_HOB(HobStart) \

(VOID *)(*(UINT8 **)&(HobStart) + GET_HOB_LENGTH (HobStart))

/**

Determines if a HOB is the last HOB in the HOB list.

This macro determine if the HOB specified by HobStart is the

last HOB in the HOB list. If HobStart is last HOB in the HOB

list, then TRUE is returned. Otherwise, FALSE is returned.

@param HobStart

A pointer to a HOB.

@retval TRUE

The HOB specified by HobStart is the last

HOB in the HOB list.

The HOB specified by HobStart is not the

@retval FALSE

last HOB in the HOB list.

**/

#define END_OF_HOB_LIST(HobStart) (GET_HOB_TYPE (HobStart) ==

(UINT16)EFI_HOB_TYPE_END_OF_HOB_LIST)

/**

Returns a pointer to data buffer from a HOB of type

EFI_HOB_TYPE_GUID_EXTENSION.

This macro returns a pointer to the data buffer in a HOB

specified by HobStart.

HobStart is assumed to be a HOB of type

EFI_HOB_TYPE_GUID_EXTENSION.

@param GuidHob

A pointer to a HOB.

```

```

@return A pointer to the data buffer in a HOB.

**/

#define GET_GUID_HOB_DATA(HobStart) \

(VOID *)(*(UINT8 **)&(HobStart) + sizeof (EFI_HOB_GUID_TYPE))

/**

Returns the size of the data buffer from a HOB of type

EFI HOB TYPE GUID EXTENSION.

This macro returns the size, in bytes, of the data buffer in a

HOB specified by HobStart.

HobStart is assumed to be a HOB of type

EFI_HOB_TYPE_GUID_EXTENSION.

GuidHob

A pointer to a HOB.

@param

@return The size of the data buffer.

**/

#define GET_GUID_HOB_DATA_SIZE(HobStart) \

(UINT16)(GET_HOB_LENGTH (HobStart) - sizeof

(EFI_HOB_GUID_TYPE))

/**

Returns the pointer to the HOB list.

This function returns the pointer to first HOB in the list.

If the pointer to the HOB list is NULL, then ASSERT().

@return The pointer to the HOB list.

**/

VOID *

EFIAPI

GetHobList (

VOID

);

/**

Returns the next instance of a HOB type from the starting HOB.

This function searches the first instance of a HOB type from

the starting HOB pointer.

If there does not exist such HOB type from the starting HOB

pointer, it will return NULL.

In contrast with macro GET_NEXT_HOB(), this function does not

skip the starting HOB pointer unconditionally: it returns

HobStart back if HobStart itself meets the requirement;

caller is required to use GET_NEXT_HOB() if it wishes to skip

current HobStart.

If HobStart is NULL, then ASSERT().

```

```

The HOB type to return.

@param Type

@param HobStart

The starting HOB pointer to search from.

@return The next instance of a HOB type from the starting HOB.

**/

VOID *

EFIAPI

GetNextHob (

UINT16

Type,

CONST VOID

*HobStart

);

/**

Returns the first instance of a HOB type among the whole HOB

list.

This function searches the first instance of a HOB type among

the whole HOB list.

If there does not exist such HOB type in the HOB list, it will

return NULL.

If the pointer to the HOB list is NULL, then ASSERT().

The HOB type to return.

@param Type

@return The next instance of a HOB type from the starting HOB.

**/

VOID *

EFIAPI

GetFirstHob (

UINT16

Type

);

/**

Returns the next instance of the matched GUID HOB from the

starting HOB.

This function searches the first instance of a HOB from the

starting HOB pointer.

Such HOB should satisfy two conditions:

its HOB type is EFI_HOB_TYPE_GUID_EXTENSION and its GUID Name

equals to the input Guid.

If there does not exist such HOB from the starting HOB pointer,

it will return NULL.

Caller is required to apply GET_GUID_HOB_DATA () and

GET_GUID_HOB_DATA_SIZE ()

to extract the data section and its size info respectively.

In contrast with macro GET_NEXT_HOB(), this function does not

skip the starting HOB pointer unconditionally: it returns

HobStart back if HobStart itself meets the requirement;

```

```

caller is required to use GET_NEXT_HOB() if it wishes to skip

current HobStart.

If Guid is NULL, then ASSERT().

If HobStart is NULL, then ASSERT().

@param Guid

The GUID to match with in the HOB list.

@param HobStart

A pointer to a Guid.

@return The next instance of the matched GUID HOB from the

starting HOB.

**/

VOID *

EFIAPI

GetNextGuidHob (

CONST EFI_GUID

*Guid,

CONST VOID

*HobStart

);

/**

Returns the first instance of the matched GUID HOB among the

whole HOB list.

This function searches the first instance of a HOB among the

whole HOB list.

Such HOB should satisfy two conditions:

its HOB type is EFI_HOB_TYPE_GUID_EXTENSION and its GUID Name

equals the input Guid.

If there does not exist such HOB from the starting HOB pointer,

it will return NULL.

Caller is required to apply GET_GUID_HOB_DATA () and

GET_GUID_HOB_DATA_SIZE ()

to extract the data section and its size info respectively.

If the pointer to the HOB list is NULL, then ASSERT().

If Guid is NULL, then ASSERT().

The GUID to match with in the HOB list.

@param Guid

@return The first instance of the matched GUID HOB among the

whole HOB list.

**/

VOID *

EFTAPT

GetFirstGuidHob (

CONST EFI GUID

*Guid

);

11

```

```

// Pointer to the HOB should be initialized with the output of

FSP INIT PARAMS

11

extern volatile void *FspHobListPtr;

/**

Reads a 64-bit value from memory that may be unaligned.

This function returns the 64-bit value pointed to by Buffer.

The function guarantees that the read operation does not

produce an alignment fault.

If the Buffer is NULL, then ASSERT().

@param Buffer Pointer to a 64-bit value that may be

unaligned.

@return The 64-bit value read from Buffer.

**/

UINT64

EFIAPI

ReadUnaligned64 (

CONST UINT64

*Buffer

)

ł

ASSERT (Buffer != NULL);

return *Buffer;

}

/**

Compares two GUIDs.

This function compares Guid1 to Guid2. If the GUIDs are

identical then TRUE is returned.

If there are any bit differences in the two GUIDs, then FALSE

is returned.

If Guid1 is NULL, then ASSERT().

If Guid2 is NULL, then ASSERT().

@param Guid1

A pointer to a 128 bit GUID.

@param Guid2

A pointer to a 128 bit GUID.

@retval TRUE

Guid1 and Guid2 are identical.

Guid1 and Guid2 are not identical.

@retval FALSE

**/

BOOLEAN

EFIAPI

CompareGuid (

CONST EFI_GUID *Guid1,

```

FSP for 3rd Gen Intel<sup>®</sup> Core™ Processors with Mobile Intel<sup>®</sup> HM76/QM77 Express Chipsets Integration Guide

```

CONST EFI_GUID *Guid2

)

{

UINT64 LowPartOfGuid1;

UINT64 LowPartOfGuid2;

UINT64 HighPartOfGuid1;

UINT64 HighPartOfGuid2;

LowPartOfGuid1 = ReadUnaligned64 ((CONST UINT64*) Guid1);

LowPartOfGuid2 = ReadUnaligned64 ((CONST UINT64*) Guid2);

HighPartOfGuid1 = ReadUnaligned64 ((CONST UINT64*) Guid1 + 1);

HighPartOfGuid2 = ReadUnaligned64 ((CONST UINT64*) Guid2 + 1);

return (BOOLEAN) (LowPartOfGuid1 == LowPartOfGuid2 &&

HighPartOfGuid1 == HighPartOfGuid2);

}

/**

Returns the pointer to the HOB list.

**/

VOID *

EFIAPI

GetHobList (

VOID

)

{

ASSERT (FspHobListPtr != NULL);

return ((VOID *)FspHobListPtr);

}

/**

Returns the next instance of a HOB type from the starting HOB.

**/

VOID *

EFIAPI

GetNextHob (

UINT16

Type,

CONST VOID

*HobStart

)

{

EFI_PEI_HOB_POINTERS Hob;

ASSERT (HobStart != NULL);

Hob.Raw = (UINT8 *) HobStart;

11

// Parse the HOB list until end of list or matching type is

found.

11

```

```

while (!END_OF_HOB_LIST (Hob)) {

if (Hob.Header->HobType == Type) {

return Hob.Raw;

}

Hob.Raw = GET_NEXT_HOB (Hob);

}

return NULL;

}

/**

Returns the first instance of a HOB type among the whole HOB

list.

**/

VOID *

EFIAPI

GetFirstHob (

UINT16

Type

)

{

VOID

*HobList;

HobList = GetHobList ();

return GetNextHob (Type, HobList);

}

/**

Returns the next instance of the matched GUID HOB from the

starting HOB.

**/

VOID *

EFIAPI

GetNextGuidHob (

*Guid,

CONST EFI_GUID

*HobStart

CONST VOID

)

{

EFI_PEI_HOB_POINTERS GuidHob;

GuidHob.Raw = (UINT8 *) HobStart;

while ((GuidHob.Raw = GetNextHob (EFI_HOB_TYPE_GUID_EXTENSION,

GuidHob.Raw)) != NULL) {

if (CompareGuid (Guid, &GuidHob.Guid->Name)) {

break;

}

GuidHob.Raw = GET_NEXT_HOB (GuidHob);

}

return GuidHob.Raw;

}

/**

Returns the first instance of the matched GUID HOB among the

whole HOB list.

**/

```

Other Host Boot Loader Concerns

```

VOID *

EFIAPI

GetFirstGuidHob (

CONST EFI_GUID *Guid

)

{

VOID *HobList;

HobList = GetHobList ();

return GetNextGuidHob (Guid, HobList);

}

```

## Appendix B – Sample Code to Find FSP Header

The sample code provided below parses the FSP binary and finds the address of the FSP Header within it.

As the FV parsing has to be done before stack is available, a mix of assembly language code and C code is used. The C code is used to parse the data structures and find the FSP INFO Header. However, since the compiler will add prolog or epilog code to the C function, inline assembly is used to bypass those portions of the C code.

The sample code provided here uses header files derived from the EDK2 source available for download at

```

http://sourceforge.net/apps/mediawiki/tianocore/index.php?title=EDK2

```

```

#include "PiFirmwareVolume.h"

#include "PiFirmwareFile.h"

void __attribute__((optimize("00"))) find_fsp_header ()

{

volatile register UINT8 *ptr asm ("eax");

__asm___volatile__ (

".global find_fsp_info_header \n\t"

"find_fsp_info_header:\n\t"

);

11

// Start at the FSP / FV Header base

11

ptr = (UINT8 *)0xFFF80000;

11

// Validate FV signature _FVH

11

if (((EFI_FIRMWARE_VOLUME_HEADER *)ptr)-> Signature !=

0x4856465F) {

ptr = 0;

goto NotFound;

}

11

// Add the Ext Header size to the Ext Header base to go to

// the end of FV header

11

ptr += ((EFI FIRMWARE VOLUME HEADER *)ptr)->ExtHeaderOffset;

ptr += ((EFI FIRMWARE VOLUME EXT HEADER *)ptr)-

>ExtHeaderSize;

```

```

11

// Align the pointer to 8 bytes and it will point to FFS

// header

11

ptr = (UINT8 *)(((UINTN)ptr + 7) & 0xFFFFFF8);

11

// Now ptr is pointing to thr FFS Header. Verify if the GUID

// matches the FSP INFORMATION HEADER GUID

11

if ((((UINT32 *)&(((EFI_FFS_FILE_HEADER *)ptr)->Name))[0] !=

0x912740BE) || (((UINT32 *)&(((EFI_FFS_FILE_HEADER *)ptr)-

>Name))[1] != 0x47342284)

|| (((UINT32

*)&(((EFI_FFS_FILE_HEADER *)ptr)->Name))[2] != 0xB08471B9)

(((UINT32 *)&(((EFI_FFS_FILE_HEADER *)ptr)->Name))[3] !=

0x0C3F3527)) {

ptr = 0;

goto NotFound;

}

11

// Add the FFS Header size to the base to find the Raw

// section Header

11

ptr += sizeof(EFI_FFS_FILE_HEADER);

if (((EFI RAW SECTION *)ptr)->Type != EFI SECTION RAW) {

ptr = 0;

goto NotFound;

}

11

// Add the Raw Header size to the base to find the FSP INFO

// Header

11

ptr += sizeof(EFI_RAW_SECTION);

NotFound:

__asm___volatile__ ("ret");

}

```

Now, call this function using a temporary ROM stack containing the return address and bypass the prolog or epilog code of the C function like below.

```

lea findFspHeaderStack, %esp

jmp find_fsp_entry

findFspHeaderStack:

.align 4

.long findFspHeaderDone

findFspHeaderDone:

```

A pictorial representation of the data structures that we parse in the above code is given below.

## Appendix C – Data Structure for Memory Down

#define NUM\_IVB\_MEM\_CLK\_FREQUENCIES 13

The data structures provided below are defined for Memory Down and need to be passed to FSP when the Memory Down feature is enabled:

```

typedef struct {