Jing Chen Seongsoo Hong (Eds.)

# Real-Time and Embedded Computing Systems and Applications

9th International Conference, RTCSA 2003 Tainan City, Taiwan, ROC, February 2003 Revised Papers

# Lecture Notes in Computer Science

2968

Edited by G. Goos, J. Hartmanis, and J. van Leeuwen

# **Springer** *Berlin*

Berlin Heidelberg New York Hong Kong London Milan Paris Tokyo

# Real-Time and Embedded Computing Systems and Applications

9th International Conference, RTCSA 2003 Tainan City, Taiwan, ROC, February 18-20, 2003 Revised Papers eBook ISBN: 3-540-24686-X Print ISBN: 3-540-21974-9

©2005 Springer Science + Business Media, Inc.

Print ©2004 Springer-Verlag Berlin Heidelberg

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Springer's eBookstore at: http://ebooks.springerlink.com and the Springer Global Website Online at: http://www.springeronline.com

#### **Preface**

This volume contains the 37 papers presented at the 9th International Conference on Real-Time and Embedded Computing Systems and Applications (RT-CSA 2003). RTCSA is an international conference organized for scientists and researchers from both academia and industry to hold intensive discussions on advancing technologies topics on real-time systems, embedded systems, ubiquitous/pervasive computing, and related topics. RTCSA 2003 was held at the Department of Electrical Engineering of National Cheng Kung University in Taiwan. Paper submissions were well distributed over the various aspects of real-time computing and embedded system technologies. There were more than 100 participants from all over the world.

The papers, including 28 regular papers and 9 short papers are grouped into the categories of scheduling, networking and communication, embedded systems, pervasive/ubiquitous computing, systems and architectures, resource management, file systems and databases, performance analysis, and tools and development. The grouping is basically in accordance with the conference program. Earlier versions of these papers were published in the conference proceedings. However, some papers in this volume have been modified or improved by the authors, in various aspects, based on comments and feedback received at the conference. It is our sincere hope that researchers and developers will benefit from these papers.

We would like to thank all the authors of the papers for their contribution. We thank the members of the program committee and the reviewers for their excellent work in evaluating the submissions. We are also very grateful to all the members of the organizing committees for their help, guidance and support. There are many other people who worked hard to make RTCSA 2003 a success. Without their efforts, the conference and this volume would not have been possible, and we would like to express our sincere gratitude to them. In addition, we would like to thank the National Science Council (NSC), the Ministry of Education (MOE), and the Institute of Information Science (IIS) of Academia Sinica of Taiwan, the Republic of China (ROC) for their generous financial support. We would also like to acknowledge the co-sponsorship by the Information Processing Society of Japan (IPSJ) and the Korea Information Science Society (KISS).

Last, but not least, we would like to thank Dr. Farn Wang who helped initiate contact with the editorial board of LNCS to publish this volume. We also appreciate the great work and the patience of the editors at Springer-Verlag. We are truly grateful.

#### **History and Future of RTCSA**

The International Conference on Real-Time and Embedded Computing Systems and Applications (RTCSA) aims to be a forum on the trends as well as innovations in the growing areas of real-time and embedded systems, and to bring together researchers and developers from academia and industry for advancing the technology of real-time computing systems, embedded systems and their applications. The conference assumes the following goals:

- to investigate advances in real-time and embedded systems;

- to promote interactions among real-time systems, embedded systems and their applications;

- to evaluate the maturity and directions of real-time and embedded system technology;

- to bridge research and practising experience in the communities of real-time and embedded systems.

RTCSA started from 1994 with the International Workshop on Real-Time Computing Systems and Applications held in Korea. It evolved into the International Conference on Real-Time Computing Systems and Applications in 1998. As embedded systems is becoming one of the most vital areas of research and development in computer science and engineering, RTCSA changed into the International Conference on Real-Time and Embedded Computing Systems and Applications in 2003. In addition to embedded systems, RTCSA has expanded its scope to cover topics on pervasive and ubiquitous computing, home computing, and sensor networks. The proceedings of RTCSA from 1995 to 2000 are available from IEEE. A brief history of RTCSA is listed below. The next RTCSA is currently being organized and will take place in Sweden.

#### International Workshop on Real-Time 1994 to 1997: **Computing Systems and Applications** RTCSA 1994 Seoul, Korea RTCSA 1995 Tokyo, Japan RTCSA 1996 Seoul, Korea **RTCSA 1997** Taipei, Taiwan 1998 to 2002: **International Conference on Real-Time Computing Systems and Applications** Hiroshima, Japan **RTCSA 1998** RTCSA 1999 Hong Kong, China Cheju Island, Korea **RTCSA 2000** Tokyo, Japan **RTCSA 2002** From 2003: **International Conference on Real-Time** and Embedded Computing Systems and **Applications**

Tainan, Taiwan

**RTCSA 2003**

## **Organization of RTCSA 2003**

The 9th International Conference on Real-Time and Embedded Computing Systems and Applications (RTCSA 2003) was organized, in cooperation with the Information Processing Society of Japan (IPSJ) and the Korea Information Science Society (KISS), by the Department of Electrical Engineering, National Cheng Kung University in Taiwan, Republic of China (ROC).

#### **Honorary Chair**

Chiang Kao President of National Cheng Kung University

#### **General Co-chairs**

Ruei-Chuan Chang National Chiao Tung University (Taiwan)

Tatsuo Nakajima Waseda University (Japan)

#### **Steering Committee**

Tei-Wei Kuo National Taiwan University (Taiwan)

Insup Lee University of Pennsylvania (USA)

Jane Liu Microsoft (USA)

Seung-Kyu Park Ajou University (Korea)

Heonshik Shin Seoul National University (Korea)

Kang Shin University of Michigan at Ann Arbor (USA)

Sang H. Son University of Virginia (USA)

Kenji Toda ITRI., AIST (Japan) Hideyuki Tokuda Keio University (Japan)

## **Advisory Committee**

Alan Burns

Jan-Ming Ho

Aloysius K. Mok

Heonshik Shin

John A. Stankovic

Hideyuki Tokuda

University of York (UK)

IIS, Academia Sinica (Taiwan)

University of Texas, Austin (USA)

Seoul National University (Korea)

University of Virginia (USA)

Keio University (Japan)

Jhing-Fa Wang National Cheng Kung University (Taiwan)

#### **Publicity Co-chairs**

Lucia Lo Bello University of Catania (Italy)

Victor C.S. Lee City University of Hong Kong (Hong Kong)

Daeyoung Kim Information and Communications University (Korea)

Sang H. Son University of Virginia (USA) Kazunori Takashio Keio University (Japan)

#### **Program Co-chairs**

Jing Chen National Cheng Kung University (Taiwan)

Seongsoo Hong Seoul National University (Korea)

#### **Program Committee**

Giorgio C. Buttazzo University of Pavia (Italy) Jörgen Hansson Linkoping University (Sweden)

Pao-Ann Hsiung

Chin-Wen Hsueh

National Chung Cheng University (Taiwan)

National Chung Cheng University (Taiwan)

Dong-In Kang ISI East, USC (USA)

Daeyoung Kim Information and Communications University (Korea)

Moon Hae Kim Konkuk University (Korea)

Tae-Hyung Kim Hanyang University (Korea)

Young-kuk Kim Chungnam National University (Korea)

Lucia Lo Bello University of Catania (Italy)

Kam-Yiu Lam City University of Hong Kong (Hong Kong)

Chang-Gun Lee Ohio State University (USA)

Victor C.S. Lee City University of Hong Kong (Hong Kong)

Yann-Hang Lee Arizona State University (USA)

Kwei-Jay Lin University of California, Irvine (USA)

Sang Lyul Min Seoul National University (Korea)

Tatsuo Nakajima Waseda University (Japan) Yukikazu Nakamoto NEC, Japan (Japan)

Joseph Ng Hong Kong Baptist University (Hong Kong)

Nimal Nissanke South Bank University (UK)

Raj Rajkumar Carnegie Mellon University (USA)

Krithi Ramamritham India Institute of Technology, Bombay (India) Ichiro Satoh National Institute of Informatics (Japan)

Lui Sha University of Illinois at Urbana-Champaign (USA)

Wei-Kuan Shih

LihChyun Shu

National Tsing Hua University (Taiwan)

National Cheng Kung University (Taiwan)

Sang H. Son University of Virginia (USA)

Hiroaki Takada Toyohashi University of Technology (Japan)

Yoshito Tobe Tokyo Denki University (Japan)

Hans Toetenel Delft University of Technology (Netherlands)

Farn Wang National Taiwan University (Taiwan)

Andy Wellings University of York (UK)

Wang Yi Uppsala University (Sweden)

#### Reviewers

Lucia Lo BelloJörgen HanssonChih-Wen HsuehGiorgio C. ButtazzoSeongsoo HongDong-In KangJing ChenPao-Ann HsiungDaeyoung Kim

Lih-Chyun Shu Moon Hae Kim Tatsuo Nakajima Sang H. Son Tae-Hyung Kim Yukikazu Nakamoto Young-Kuk Kim Nimal Nissanke Hiroaki Takada Yoshito Tobe Kam-Yiu Lam Joseph Ng Chang-Gun Lee Raj Rajkumar Farn Wang Victor C.S. Lee Krithi Ramamritham Andy Wellings Ichiro Satoh Wang Yi Yann-Hang Lee Kwei-Jay Lin Lui Sha Wei-Kuan Shih Sang Lyul Min

### **Sponsoring Institutions**

National Science Council (NSC), Taiwan, ROC Ministry of Education (MOE), Taiwan, ROC Institute of Information Science (IIS) of Academia Sinica, Taiwan, ROC Information Processing Society of Japan (IPSJ), Japan Korea Information Science Society (KISS), Korea

# **Table of Contents**

# **Scheduling**

| Aperiodic Servers                                                                                                                                 | 1   |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| On the Composition of Real-Time Schedulers                                                                                                        | 18  |

| An Approximation Algorithm for Broadcast Scheduling in Heterogeneous Clusters                                                                     | 38  |

| Scheduling Jobs with Multiple Feasible Intervals                                                                                                  | 53  |

| Deterministic and Statistical Deadline Guarantees for a Mixed Set of Periodic and Aperiodic Tasks                                                 | 72  |

| Real-Time Disk Scheduling with On-Disk Cache Conscious                                                                                            | 88  |

| Probabilistic Analysis of Multi-processor Scheduling of Tasks with Uncertain Parameters                                                           | 103 |

| Real-Time Virtual Machines for Avionics Software Porting and Development                                                                          | 123 |

| Algorithms for Managing QoS for Real-Time Data Services Using Imprecise Computation                                                               | 136 |

| Networking and Communication                                                                                                                      |     |

| On Soft Real-Time Guarantees on Ethernet                                                                                                          | 158 |

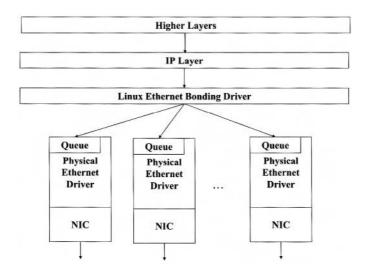

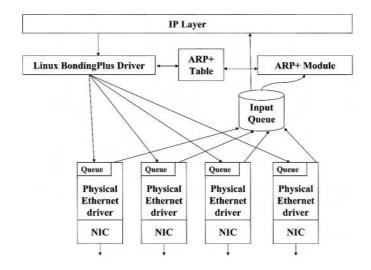

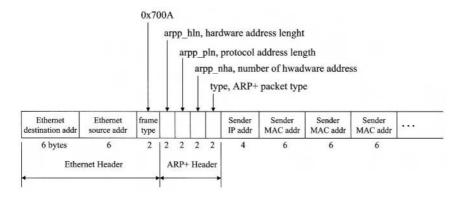

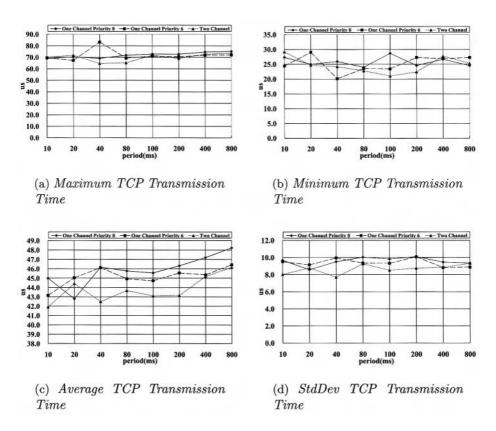

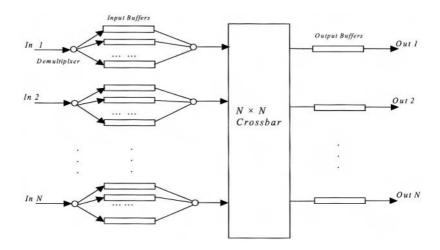

| BondingPlus: Real-Time Message Channel in Linux Ethernet Environment Using Regular Switching Hub  Hsin-hung Lin, Chih-wen Hsueh, Guo-Chiuan Huang | 176 |

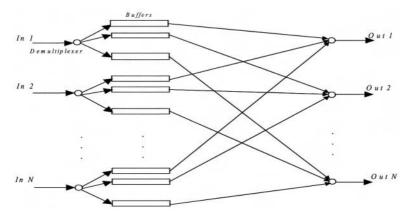

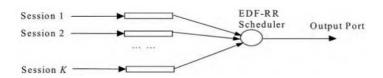

| An Efficient Switch Design for Scheduling Real-Time  Multicast Traffic  Deming Liu, Yann-Hang Lee           | 194 |

|-------------------------------------------------------------------------------------------------------------|-----|

| <b>Embedded Systems/Environments</b>                                                                        |     |

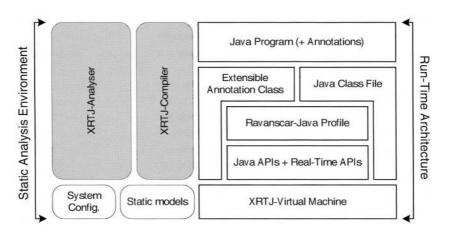

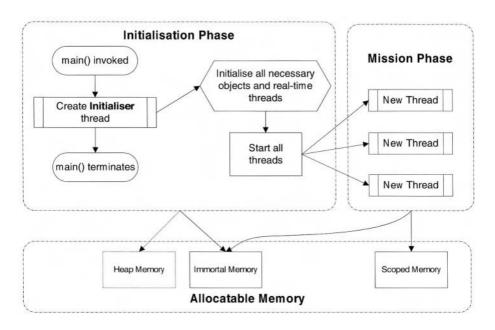

| XRTJ: An Extensible Distributed High-Integrity Real-Time Java Environment                                   | 208 |

| Quasi-Dynamic Scheduling for the Synthesis of Real-Time Embedded Software with Local and Global Deadlines   | 229 |

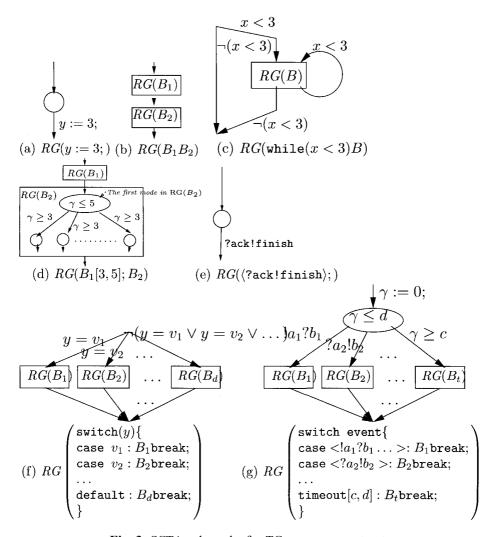

| Framework-Based Development of Embedded Real-Time Systems Hui-Ming Su and Jing Chen  Hui-Ming Su, Jing Chen | 244 |

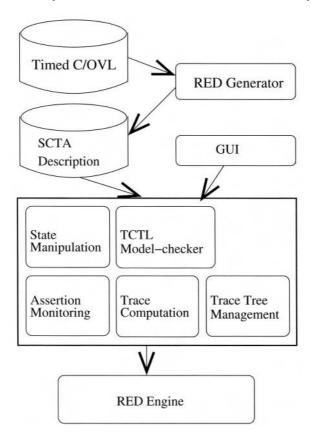

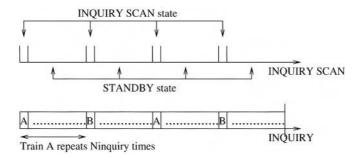

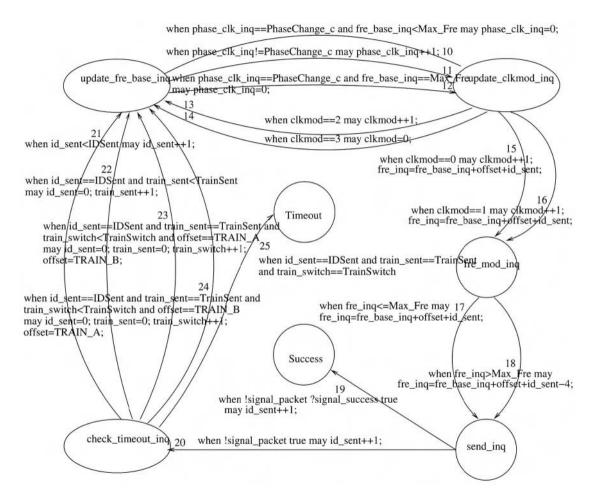

| OVL Assertion-Checking of Embedded Software with  Dense-Time Semantics                                      | 254 |

| Pervasive/Ubiquitous Computing                                                                              |     |

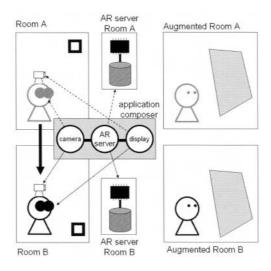

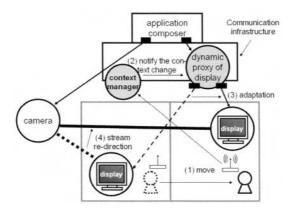

| System Support for Distributed Augmented Reality in Ubiquitous Computing Environments                       | 279 |

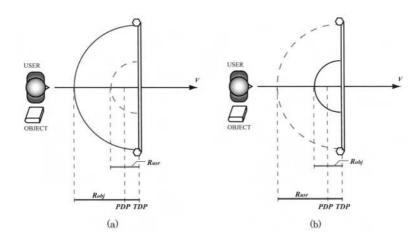

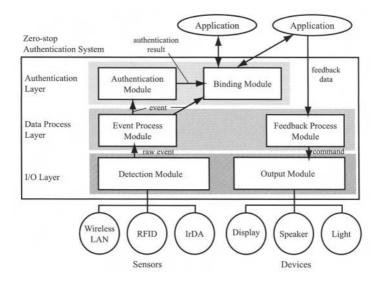

| Zero-Stop Authentication: Sensor-Based Real-Time Authentication System                                      | 296 |

| An Interface-Based Naming System for Ubiquitous Internet Applications                                       | 312 |

| Systems and Architectures                                                                                   |     |

| Schedulability Analysis in EDF Scheduler with Cache Memories                                                | 328 |

| Impact of Operating System on Real-Time Main-Memory Database System's Performance                           | 342 |

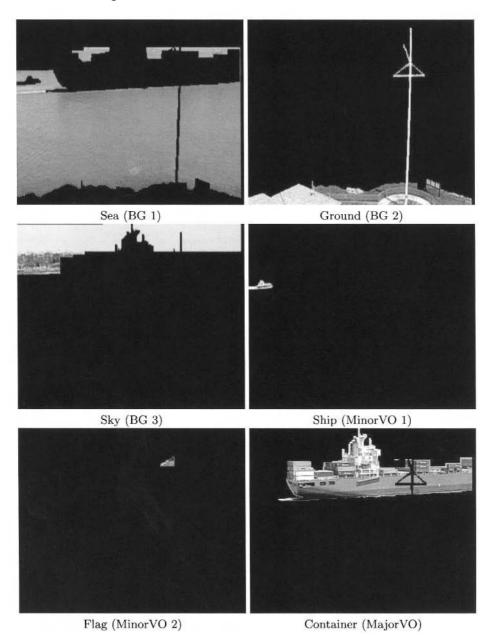

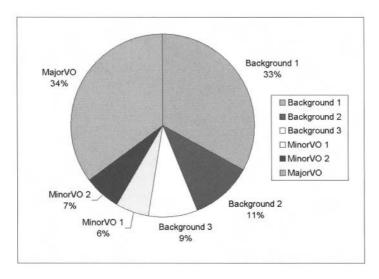

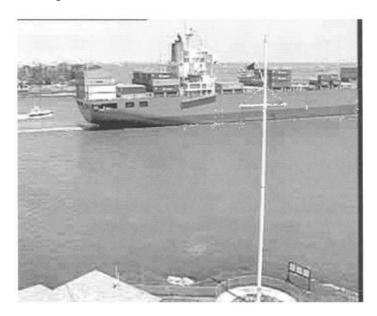

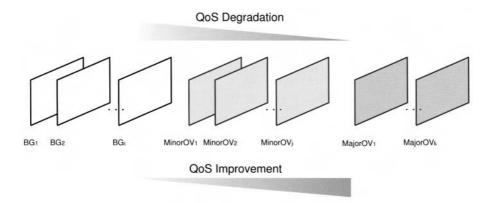

| The Design of a QoS-Aware MPEG-4 Video System                                                               | 351 |

| Resource Management                                                                                                                                     |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Constrained Energy Allocation for Mixed Hard and Soft Real-Time Tasks                                                                                   | 371 |

| An Energy-Efficient Route Maintenance Scheme for Ad Hoc Networking Systems                                                                              | 389 |

| Resource Reservation and Enforcement for Framebuffer-Based Devices Chung-You Wei, Jen-Wei Hsieh, Tei-Wei Kuo, I-Hsiang Lee, Yian-Nien Wu, Mei-Chin Tsai | 398 |

| File Systems and Databases                                                                                                                              |     |

| An Efficient B-Tree Layer for Flash-Memory Storage Systems                                                                                              | 409 |

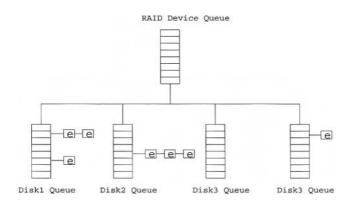

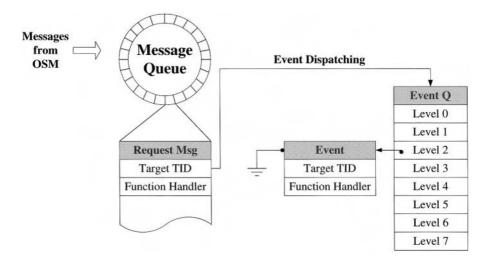

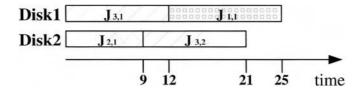

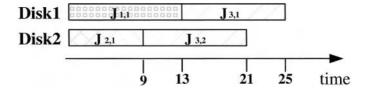

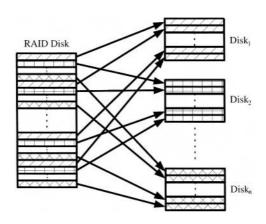

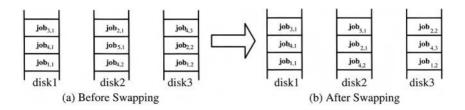

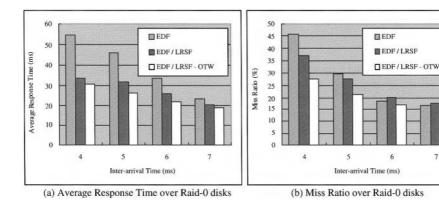

| Multi-disk Scheduling for High-Performance RAID-0 Devices                                                                                               | 431 |

| Database Pointers: A Predictable Way of Manipulating Hot Data in Hard Real-Time Systems                                                                 | 454 |

| Performance Analysis                                                                                                                                    |     |

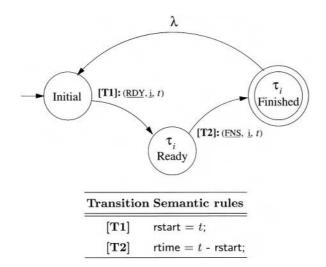

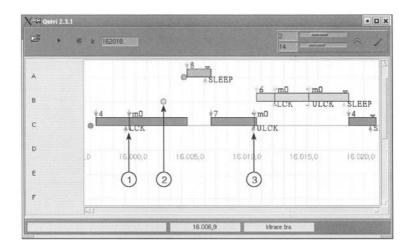

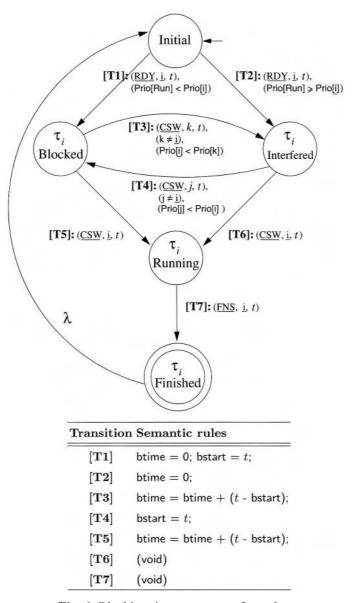

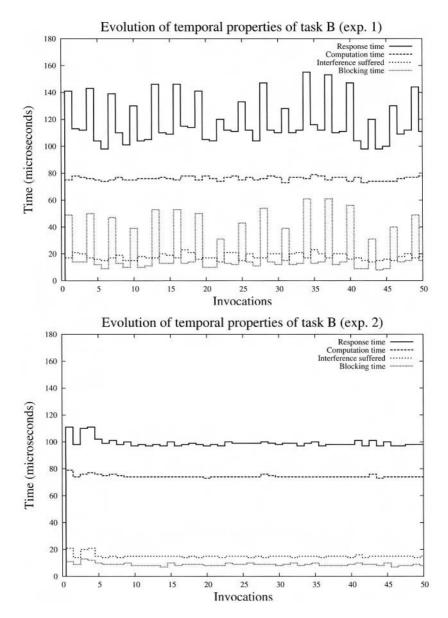

| Extracting Temporal Properties from Real-Time Systems by Automatic Tracing Analysis                                                                     | 466 |

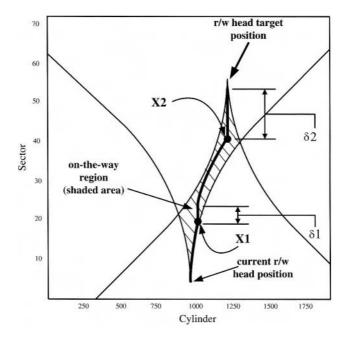

| Rigorous Modeling of Disk Performance for Real-Time Applications Sangsoo Park, Heonshik Shin                                                            | 486 |

| Bounding the Execution Times of DMA I/O Tasks on Hard-Real-Time Embedded Systems                                                                        | 499 |

| Tools and Development                                                                                                                                   |     |

| Introducing Temporal Analyzability Late in the Lifecycle of Complex Real-Time Systems                                                                   | 513 |

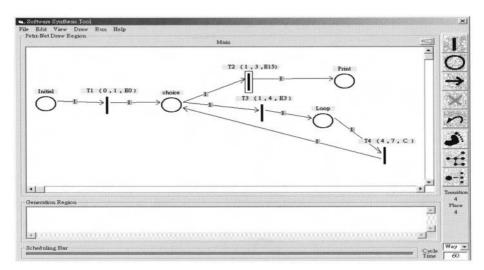

| RESS: Real-Time Embedded Software Synthesis and Prototyping Methodology                                                                                 | 529 |

#### XIV Table of Contents

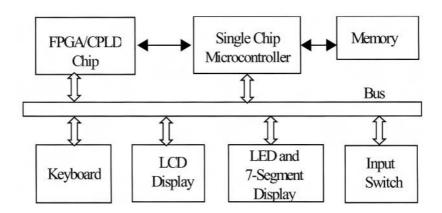

| Software Platform for Embedded Software Development                                                | 545 |

|----------------------------------------------------------------------------------------------------|-----|

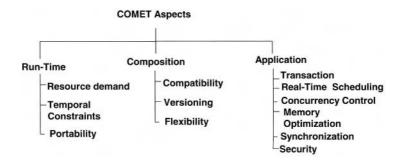

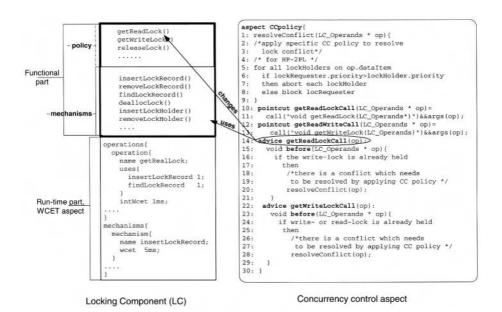

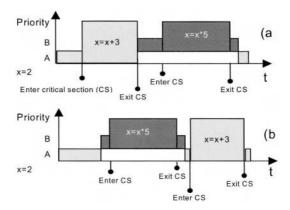

| Towards Aspectual Component-Based Development of Real-Time Systems                                 | 558 |

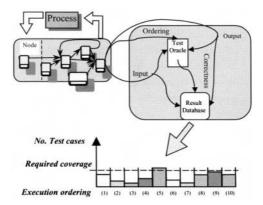

| Testing of Multi-Tasking Real-Time Systems with Critical Sections  Anders Pettersson, Henrik Thane | 578 |

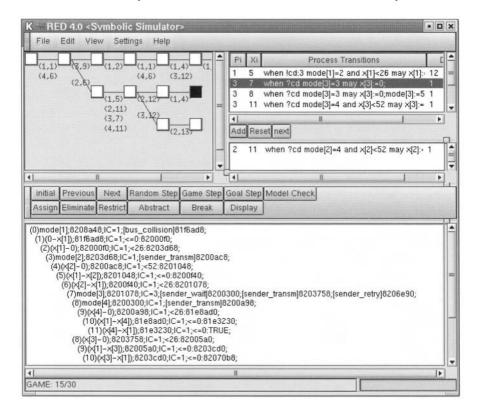

| Symbolic Simulation of Real-Time Concurrent Systems  Farn Wang, Geng-Dian Huang, Fang Yu           | 595 |

| Author Index                                                                                       | 619 |

# Scheduling-Aware Real-Time Garbage Collection Using Dual Aperiodic Servers

Taehyoun Kim<sup>1</sup> and Heonshik Shin<sup>2</sup>

<sup>1</sup> SOC Division, GCT Research, Inc.,

Seoul 150-877, Korea

thkim@gctsemi.com

School of Electrical Engineering and Computer Science, Seoul National University,

Seoul 151-742, Korea

shinhs@gnu.ac.kr

**Abstract.** Garbage collection has not been widely used in embedded real-time applications since traditional real-time garbage collection algorithm can hardly bound its worst-case responsiveness. To overcome this limitation, we have proposed a scheduling-integrated real-time garbage collection algorithm based on the single aperiodic server in our previous work. This paper introduces a new scheduling-aware real-time garbage collection which employs two aperiodic servers for garbage collection work. Our study aims at achieving similar performance compared with the single server approach whilst relaxing the limitation of the single server approach. In our scheme, garbage collection requests are scheduled using the preset CPU bandwidth of aperiodic server such as the sporadic server and the deferrable server. In the dual server scheme, most garbage collection work is serviced by the secondary server at low priority level. The effectiveness of our approach is verified by analytic results and extensive simulation based on the trace-driven data. Performance analysis demonstrates that the dual server scheme shows similar performance compared with the single server approach while it allows flexible system design.

#### 1 Introduction

As modern programs require more functionality and complex data structures, there is a growing need for dynamic memory management on heap to efficiently utilize the memory by recycling unused heap memory space. In doing so, dynamic memory may be managed explicitly by the programmer through the invocation of "malloc/free" procedures which is often error-prone and cumbersome.

For this reason, the system may be responsible for the dynamic memory reclamation to achieve better productivity, robustness, and program integrity. Central to this automatic memory reclamation is the garbage collection (GC) process. The garbage collector identifies the data items that will never be used again and then recycles their space for reuse at the system level.

In spite of its advantages, GC has not been widely used in embedded real-time applications. This is partly because GC may cause the response time of application to be unpredictable. To guarantee timely execution of a real-time application, all the

components of the application must be *predictable*. A certain software component is *predictable* means that its worst-case behavior is bounded and known *a priori*.

This is because garbage collectors should also run in *real-time* mode for predictable execution of real-time applications. Thus, the requirements for real-time garbage collector are summarized and extended as follows [1]; First, a real-time garbage collector often interleaves its execution with the execution of an application in order to avoid intolerable pauses incurred by the stop-and-go reclamation. Second, a real-time collector must have mutators <sup>1</sup> report on any changes that they have made to the liveness of heap objects to preserve the consistency of a heap. Third, garbage collector must not interfere with the schedulability of hard real-time mutators. For this purpose, we need to keep the basic memory operations short and bounded. So is the synchronization overhead between garbage collector and mutators. Lastly, real-time systems with garbage collection must meet the deadlines of hard real-time mutators while preventing the application from running out of memory.

Considering the properties that are needed for real-time garbage collector, this paper presents a new scheduling-aware real-time garbage collection algorithm. We have already proposed a scheduling-aware real-time GC scheme based on the single server approach in [1]. Our GC scheme aims at guaranteeing the schedulability of hard real-time tasks while minimizing the system memory requirement. In the single server approach, an aperiodic server services GC requests at the highest priority level. It has been proved that, in terms of memory requirement, our approach shows the best performance compared with other aperiodic scheduling policies without missing hard deadlines [1].

However, the single server approach has a drawback. In terms of rate monotonic (RM) scheduling, the server must have the shortest period in order to be assigned for the highest priority. Usually, the safe server capacity for the shortest period may not be large enough to service a small part of GC work. For this reason, the single server approach may be sometimes impractical. To overcome this limitation, we propose a new scheduling-aware real-time GC scheme based on dual aperiodic servers. In the dual server approach, GC requests are serviced in two steps. The primary server atomically processes the initial steps such as flipping and memory initialization at the highest priority level. The secondary server scans and evacuates live objects. The effectiveness of the new approach is verified by simulation studies.

The rest of this paper is organized as follows. Sect. 2 presents a system model and formulates the problem addressed in this paper. The real-time GC technique based on the dual aperiodic servers is introduced in Sect. 3. Performance evaluation for the proposed schemes is presented in Sect. 4. This section proves the effectiveness of our algorithm by estimating various memory-related performance metrics. Sect. 5 concludes the paper.

#### 2 Problem Statement

We now consider a real-time system with a set of n periodic priority-ordered mutator tasks,  $\mathcal{M} = \{\mathcal{M}_1, \ldots, \mathcal{M}_n\}$  where  $\mathcal{M}_n$  is the lowest-priority task and all the tasks follow rate monotonic scheduling [2]. The task model in this paper includes an additional

<sup>&</sup>lt;sup>1</sup> Because tasks may *mutate* the reachability of heap data structure during the GC cycle, this paper uses the term "mutator" for the tasks that manipulate dynamically-allocated heap.

| 7 | ah | de | 1 | N | വ | 21 | ic | m | c |

|---|----|----|---|---|---|----|----|---|---|

|   |    |    |   |   |   |    |    |   |   |

| Symbol                             | Description                                                                                      |  |  |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| $\mathcal{M}_i, \mathcal{M}_{i,j}$ | Periodic mutator task $i$ and its $j^{th}$ instance                                              |  |  |  |  |  |

| $C_i, T_i, D_i, R_i$               | Worst-case execution time, period, deadline, and response time of $\mathcal{M}_i$                |  |  |  |  |  |

| $A_i$                              | Maximum amount of memory allocated by $\mathcal{M}_i$ during $T_i$                               |  |  |  |  |  |

| $\mathcal{G}_k$                    | $k^{th}$ garbage collection request                                                              |  |  |  |  |  |

| $C_{GC}, R_{GC}$                   | Worst-case execution time of and response time of $\mathcal{G}$                                  |  |  |  |  |  |

| $L_k, L_k^*$                       | Amount of live memory processed by $G_k$ and its maximum value                                   |  |  |  |  |  |

| $M_{resv}$                         | Memory reservation for hard real-time tasks                                                      |  |  |  |  |  |

| M                                  | System Memory requirement                                                                        |  |  |  |  |  |

| $T_{s1}, T_{s2}$                   | Periods of the primary server and the secondary server                                           |  |  |  |  |  |

| $C_{s1}, C_{s2}$                   | Capacities of the primary server and the secondary server                                        |  |  |  |  |  |

| $S_i(k), F_i(k)$                   | Start/Completion time of the $k^{th}$ instance of $\mathcal{M}_i$                                |  |  |  |  |  |

| $\delta_i(t)$                      | Idle time at priority level $i$ at time $t$                                                      |  |  |  |  |  |

| $I_i(w)$                           | Interference of tasks with higher priority than that of $\mathcal{M}_i$ during the time interval |  |  |  |  |  |

|                                    | [0, w)                                                                                           |  |  |  |  |  |

property, memory allocation requirement of  $\mathcal{M}_i$ .  $\mathcal{M}_i$  is characterized by a tuple  $\mathcal{M}_i = (C_i, T_i, D_i, A_i)$  (see Table 1 for notations). Our discussion will be based on the following assumptions:

- Assumption 1: There are no aperiodic mutator tasks.

- Assumption 2: The context switching and task scheduling overhead are negligibly small.

- Assumption 3: There are no precedence relations among  $\mathcal{M}_i$ s. The precedence constraint placed by many real-time systems can be easily removed by partitioning tasks into sub-tasks or properly assigning the priorities of tasks.

- Assumption 4: Any task can be instantly preempted by a higher priority task, *i.e.*, there is no blocking factor.

- Assumption 5:  $C_i$ ,  $T_i$ ,  $D_i$ , and  $A_i$  are known a priori.

Although estimation of  $A_i$  is generally an application-specific problem,  $A_i$  can be specified by the programmer or can be given by a pre-runtime trace-driven analysis [3]. The target system is designed to adopt dynamic memory allocation with no virtual memory. In this paper, we consider a real-time copying collector proposed in [3], [4] for its simplicity and real-time property. This paper treats each GC request as a separate aperiodic task  $\{\mathcal{G}_k(t_s^k, t_e^k), k \geq 1\}$  where  $t_s^k$  and  $t_e^k$  denote the release time and completion time of the  $k^{th}$  GC request  $\mathcal{G}_k$ , respectively.

In our memory model, the cumulative memory consumption  $m_c(\mathcal{M}_i, k, t)$  by a mutator task, defined for the interval  $[t_s^k, t_s^{k+1})$ , is a monotonic increasing function. Although the memory consumption function for each mutator can be various types of functions, we can easily derive the upper bound of memory consumption of  $\mathcal{M}_i$  during t time units from the worst-case memory requirement of  $\mathcal{M}_i$ , which amounts to a product of  $A_i$  and the worst-case invocation number of  $\mathcal{M}_i$  during t time units. Then,

the cumulative memory consumption by all the mutator tasks at t' ( $t_s^k \le t' < t_s^{k+1}$ ) is bounded by the following equation.

$$m_c(k, t') \triangleq \sum_{i=1}^n m_c(\mathcal{M}_i, k, t') \leq \sum_{i=1}^n \left\{ \left( \left\lceil \frac{t'}{T_i} \right\rceil - \left\lfloor \frac{t_s^k}{T_i} \right\rfloor \right) A_i \right\}$$

(1)

On the contrary, the amount of available memory depends on the reclamation rate of the garbage collector. For the copying collector, half of the total memory is reclaimed entirely at flip time. Actually, the amount of heap memory reproduced by  $\mathcal{G}_k$  depends on M and the size of live objects  $L_k$ , and is bounded by  $(\frac{M}{2} - L_k)$ .

We now consider the property of real-time GC request  $\mathcal{G}_k$ . First,  $\mathcal{G}_k$  is an aperiodic request because its release time is not known *a priori*. It is released when the cumulative memory consumption exceeds the amount of free (recycled) memory. Second,  $\mathcal{G}_k$  is a hard real-time request. The  $k^{th}$  GC request  $\mathcal{G}_k(t_s^k, t_e^k)$  must be completed before  $\mathcal{G}_{k+1}(t_s^{k+1}, t_e^{k+1})$  is released. In other words, the condition  $t_e^k < t_s^{k+1}$  should always hold. Suppose that available memory becomes less than a certain threshold while previous GC request has not been completed yet. In this case, the heap memory is fully occupied by the evacuated objects and newly allocated objects. Thus, neither the garbage collector nor mutators can continue to execute any longer.

On the other hand, the system may also break down if there is no CPU bandwidth left for GC at  $t_s^{k+1}$  even though the condition  $t_e^k < t_s^{k+1}$  holds. To solve this problem, we propose that the system should reserve a certain amount of memory spaces in order to prevent system break-down due to memory shortage. We also define a reservation interval, denoted by  $\mathcal{R}_{\mathcal{G}}$ , to bound the memory reservation. The reservation interval represents the worst-case time interval  $[t_s^k, t_\gamma)$ , where  $t_\gamma (\geq t_e^k)$  is the earliest time instant at which the CPU bandwidth for GC becomes available. Hence, the amount of memory reservation  $M_{resv}$  can be computed by the product of  $\mathcal{R}_{\mathcal{G}}$  and the memory requirement of all the mutator tasks during  $\mathcal{R}_{\mathcal{G}}$ . There should also be memory spaces in which currently live objects are copied. As a result, for the copying collector addressed in this paper, the system memory requirement is given by:

$$M = 2(M_{resv} + L_k^*) = 2(\sum_{i=1}^n \left\lceil \frac{\mathcal{R}_{\mathcal{G}}}{T_i} \right\rceil A_i + L_k^*)$$

(2)

where  $M_{resv}$  and  $L_k^*$  denote the worst-case memory reservation and the worst-case live memory, respectively. The reservation interval  $\mathcal{R}_{\mathcal{G}}$  is derived from the worst-case GC response time  $R_{GC}$  and the GC scheduling policy.

#### 3 Dual Server Approach

#### 3.1 Background

We have presented a scheduling-aware garbage collection scheme using single aperiodic server in [1], [3]. In the single server approach, GC work is serviced by an aperiodic server with a preset CPU bandwidth at the highest priority. The aperiodic server preserves its bandwidth waiting for the arrival of aperiodic GC requests. Once a GC request arrives in

the meantime, the server performs GC as long as the server capacity permits; if it cannot finish within one server period, it will resume execution when the consumed execution time for the server is replenished. By assigning the highest priority, the garbage collector can start immediately on arriving  $\mathcal{G}_k$  preempting the mutator task running.

However, the single server approach has a drawback. Under the aperiodic server scheme, the server capacity tends to be very small at the highest priority. Although the server capacity may be large enough to perform the initial parts of GC procedure such as flipping and memory initialization, it may not be large enough to perform single copying operation of a large memory block. Guaranteeing the atomicity of such operation may yield another unpredictable delay such as synchronization overhead. For this reason, this approach may be sometimes impractical.

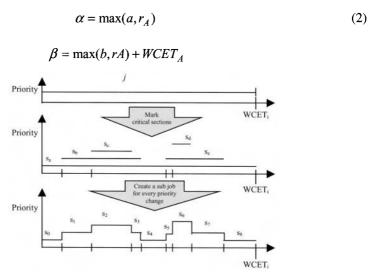

#### 3.2 Scheduling Algorithm

In this section, we present a new scheduling-aware real-time GC scheme based on dual aperiodic servers. In the dual server approach, GC is performed in two steps. The primary server performs flip operation and atomic memory initialization at the highest priority. The secondary server incrementally traverses and evacuates live objects. The major issue of dual server approach is to decide the priority of the secondary server and its safe capacity. We mean maximum server capacity which can guarantee the schedulability of given task set by *safe* capacity. The dual server approach can be applied to the sporadic server (SS) and the deferrable server (DS).

The first step is to find the safe capacity of the secondary server. This procedure is applied to each priority level of periodic tasks in given task set for simplicity. In doing so, we assume that the priority of the secondary server is assigned according to the RM policy. There is always a task of which period is identical to the period of the secondary server because we compute the capacity of the secondary server for the periods of periodic tasks. In this case, the priority of secondary server is always higher than that of such a task.

The maximum idle time at priority level i, denoted by  $\delta(D_i)$ , is set to the initial value of the capacity. For each possible capacity of the secondary server  $C_{s2} \in [1, \delta(D_i)]$ , we can find the maximum capacity at priority level i which can guarantee the schedulability of given task set using binary search. As a result, we have n alternatives for the parameters of the secondary server. The selection of the parameter is dependent on the primary consideration of system designer. In general, the primary goal is to achieve maximum server utilization. However, our goal is to minimize the memory requirement as long as there exists a feasible schedule for hard real-time mutators.

As mentioned in Sect. 2, the system memory requirement is derived from  $M_{resv}$  and  $L_k^*$ . The worst-case memory reservation is derived from  $R_{GC}$  under the scheduling policy used. Hence, we need a new algorithm to find  $R_{GC}$  under the dual server approach to derive the memory requirement.

For this purpose, we use the schedulability analysis which is originally presented by Bernat [5]. Let the pair of parameters (period, capacity) =  $(T_s, C_s)$  of the primary server and the secondary server be  $(T_{s1}, C_{s1})$  and  $(T_{s2}, C_{s2})$ , respectively. Then, we assign  $T_{s1} = T_1$  and  $C_{s1} = \sigma$  such that  $\sigma$  is the smallest time required for flipping and atomic

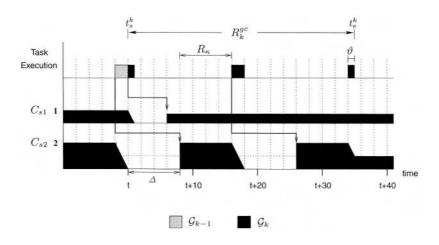

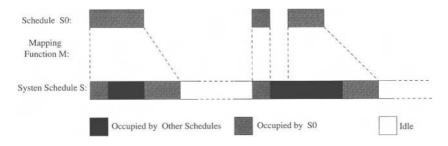

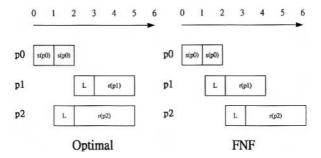

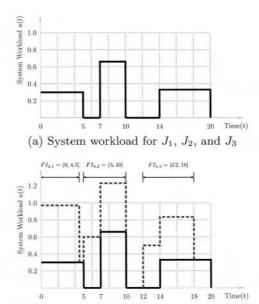

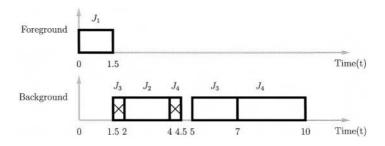

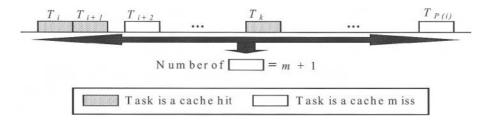

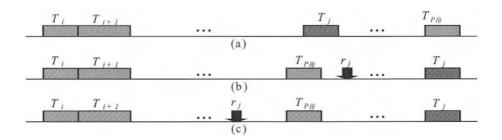

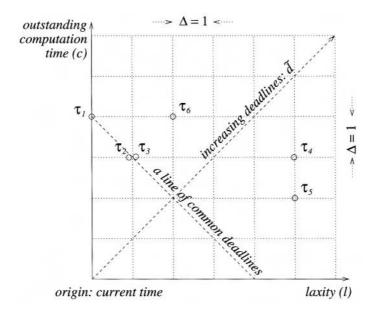

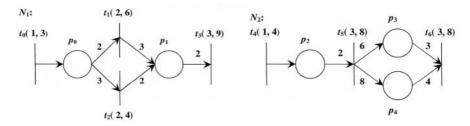

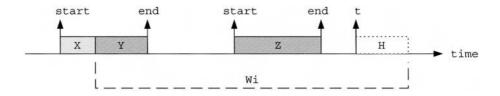

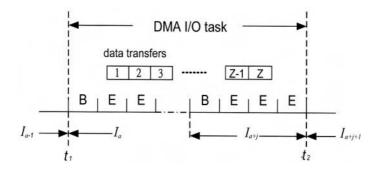

Fig. 1. Response time of  $\mathcal{G}_k$   $(T_{s1} = 6, C_{s1} = 1, T_{s2} = 10, C_{s2} = 2, C_{GC} = 4)$

memory initialization. Traditional worst-case response time formulation can be used to compute  $R_{GC}$ .

In Theorem 1, we show the worst-case response time of GC under the SS policy.

**Theorem 1.** Under the SS, for fixed  $C_{GC}$ ,  $C_{s1}$ ,  $T_{s1}$ ,  $C_{s2}$ , and  $T_{s2}$ , the response time of the garbage collector  $R_{GC}$  of the dual server approach is bounded by the  $k^{th}$  completion time of a virtual server task  $\overline{SS_{s2}}$  with  $T'_{s2} = T_{s2} + R_{\kappa}$  period,  $C'_{s2} = \vartheta$  capacity, and  $(T_{s2} - C_{s2})$  offset such that  $R_{\kappa}$  is the worst-case response time of a task  $\mathcal{M}_{\kappa}$  which is the lowest priority task among the higher priority tasks than the secondary server,  $\vartheta = C_{GC} - C_{s1} - \left(\left\lceil \frac{C_{GC} - C_{s1}}{C_{s2}}\right\rceil - 1\right) C_{s2}$  and  $k = \left\lceil \frac{C_{GC} - C_{s1}}{C_{s2}}\right\rceil$ .

**Proof.** Let  $\epsilon(>0)$  be the available capacity of the secondary server when a new GC request is released. If the condition  $C_{GC}-C_{s1} \leq \epsilon$  is satisfied, then the GC request  $\mathcal{G}_k$  is completely serviced within one period of the secondary server. Otherwise, additional server periods are required to complete  $\mathcal{G}_k$ . The remaining GC work must be processed after the capacity of the secondary server is replenished. We assume that there is always  $C_{s1}$  capacity available when a new GC request arrives. This is because the replenishment period of the primary server will always be shorter than or equal to that of the secondary server. If this assumption is not valid, GC requests will always fail.

The interval, say  $\Delta$ , between the beginning of  $\mathcal{G}_k$  and the first replenishment of the secondary server is at most  $(T_{s2}-C_{s2})$ . In other words, the first period of the secondary server is released  $\Delta$  time units after  $\mathcal{G}_k$  was requested because the secondary server may not be released immediately due to interference caused by higher priority tasks. In the proof of Theorem 1,  $R_{GC}$  is computed by using the capacity of the sporadic server and the replenishment period.

Roughly, the worst-case response time of  $\mathcal{G}_k$  coincides with the  $k^{th}$  completion time of the secondary server with  $\Delta$  offset such that  $k = \left\lceil \frac{C_{GC} - C_{s1}}{C_{s2}} \right\rceil$ . More correctly,

it is the sum of  $\Delta$ , any additional server periods required for replenishment, and the CPU demand remaining at the end of GC cycle. It results from the assumption that all the mutator tasks arrive exactly at which the first replenishment of the secondary server occurs. In this case, the second replenishment of the secondary server occurs at the time when all the higher priority tasks have been completed. Formally, in the worst-case, the longest replenishment period of the secondary server is equal to the worst-case response time of  $\mathcal{M}_{\kappa}$  denoted by  $R_{\kappa}$  where  $\mathcal{M}_{\kappa}$  is the lowest priority task among the higher priority tasks. Because the interference is always smaller than the worst-case interference at the critical instant, the following replenishment periods are always less than or equal to the first replenishment period. Hence, we can safely set the period of a virtual task  $\overline{SS_2}$  to  $(T_{s2}+R_{\kappa})$ . The CPU demand remaining at the end of GC cycle, say  $\vartheta$ , is given by:

$$\vartheta = C_{GC} - C_{s1} - \left( \left\lceil \frac{C_{GC} - C_{s1}}{C_{s2}} \right\rceil - 1 \right) C_{s2}.$$

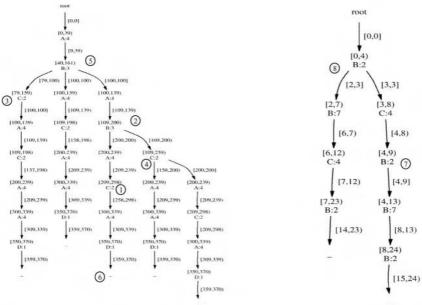

It follows that the sum of the server periods required and the CPU demand remaining at the end of GC cycle actually corresponds to the worst-case response time of the  $k^{th}$  response time of a virtual server task  $\overline{SS_{s2}}$  with  $T'_{s2}$  period and  $\vartheta$  capacity. Because a task's response time is only affected by higher priority tasks, this conversion is safe without loss of generality. Fig. 1 illustrates the worst-case situation.

Since the DS has different server capacity replenishment policy, we have the following theorem.

**Theorem 2.** Under the DS, for fixed  $C_{GC}$ ,  $C_{s1}$ ,  $T_{s1}$ ,  $C_{s2}$ , and  $T_{s2}$ , the response time of the garbage collector  $R_{GC}$  of the dual server approach is bounded by the  $k^{th}$  completion time of a virtual server task  $\overline{SS_{s2}}$  with  $T'_{s2} = T_{s2}$  period,  $C'_{s2} = \vartheta$  capacity, and  $(T_{s2} - C_{s2})$  offset such that  $\vartheta = C_{GC} - C_{s1} - \left(\left\lceil \frac{C_{GC} - C_{s1}}{C_{s2}} \right\rceil - 1\right)C_{s2}$  and  $k = \left\lceil \frac{C_{GC} - C_{s1}}{C_{s2}} \right\rceil$ .

**Proof.** The server capacity for the DS is fully replenished at the beginning of server's period while the SS replenishes the server capacity exactly  $T_s$  time units after the aperiodic request was released. For this reason, the period of a virtual task  $T_{s2}'$  equals  $T_{s2}$ .  $\Box$

For the dual server approach, we do not need to consider the replenishment of server capacity in computing  $M_{resv}$ . This is because there is always sufficiently large time interval to replenish the capacity of the primary server between two consecutive GC cycles. Finally we have:

$$M_{resv} = \sum_{i=1}^{n} \left\lceil \frac{R_{GC}}{T_i} \right\rceil A_i \,. \tag{3}$$

Let  $F'_{s2}(k)$  denote the  $k^{th}$  completion time of a virtual secondary server task  $\overline{SS_{s2}}$ . As shown above,  $F'_{s2}(k)$  is equal to  $R_{GC}$ . To derive the memory requirement, we now

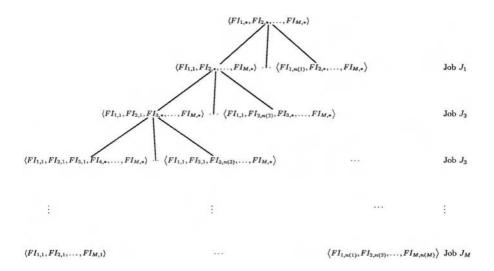

present how we can find  $F'_{s2}(k)$  with given parameters of the secondary server. We now apply Bernat's analysis to find  $F'_{s2}(k)$ . Bernat presents an extended formulation to compute the worst-case completion time of  $\mathcal{M}_i$  at its  $k^{th}$  invocation.

We explain briefly the extended worst-case response time formulation. Let us first consider the worst-case completion time of  $\mathcal{M}_i$  at the second invocation. The completion time of the second invocation  $F_i(2)$  includes its execution time and interference caused by higher priority tasks. The interference is always smaller than the worst-case interference at the critical instant. Formally, the idle time at priority level i at w, denoted by  $\delta_i(w)$ , is defined as the amount of CPU time can be used by tasks with lower priority than  $\mathcal{M}_i$  during the period [0, w) in [5]. Again, the amount of idle time at the start of each task invocation is written as:

$$\delta_i(k) = \delta_i(S_i(k)) .$$

Based on the above definitions,  $F_i(2)$  includes the time required to complete two invocations of  $\mathcal{M}_i$ , the CPU time used by lower priority tasks (level-i idle time), and the interference due to higher priority tasks. Thus, it is given by the following recurrence relation:

$$\begin{cases} w^{(0)} = S_i(2) + C_i \\ w^{(n+1)} = 2C_i + \delta_i(2) + I_i(w^{(n)}) \end{cases}$$

(4)

where  $I_i(w^{(n)})$  denotes the interference caused by tasks with higher priority than task i. The correctness of Eq. (4) is proved in [5].

Similarly, the completion time of the  $k^{th}$  invocation of  $\mathcal{M}_i$ ,  $F_i(k)$  is the sum of the time required to complete k invocations of  $\mathcal{M}_i$ , the CPU time used by lower priority tasks, and the interference due to higher priority tasks. Thus, we have  $F_i(k)$  as the smallest  $w \geq 0$  such that:

$$w = kC_i + \delta_i(k) + I_i(w).$$

(5)

More formally,  $F_i(k)$  corresponds to the smallest solution to the following recurrence relation:

$$\begin{cases} w^{(0)} = S_i(k) + C_i \\ w^{(n+1)} = kC_i + \delta_i(k) + I_i(w^{(n)}) \end{cases} .$$

(6)

As mentioned earlier, the worst-case response time of garbage collector equals  $F'_{s2}(k)$ . Following the definition of  $F'_{s2}(k)$ , it can be found by the worst-case response time analysis at the critical instant. For this reason, we can apply the Bernat's extended worst-case response time formulation to our approach without loss of generality.  $F'_{s2}(k)$  is the smallest solution  $w \ (\geq 0)$  where  $w^{(n+1)} = w^{(n)}$  to the following recurrence relation:

$$\begin{cases} w^{(0)} = S_{s2}(k) + C'_{s2} \\ w^{(n+1)} = kC'_{s2} + \delta_{s2}(k) + I_{s2}(w^{(n)}), \end{cases}$$

(7)

where

$$S_{s2}(k) = (k-1)T'_{s2}$$

,  $C'_{s2} = C_{GC} - C_{s1} - \left(\left\lceil \frac{C_{GC} - C_{s1}}{C_{s2}} \right\rceil - 1\right)C_{s2}$ ,  $\delta_{s2}(k) = \delta_{s2}(S_{s2}(k))$ , and  $I_{s2}(w^{(n)}) = \sum_{\mathcal{M}_j \in hp(\overline{SS}_{s2})} \left\lceil \frac{w^{(n)}}{T_j} \right\rceil C_j$ . In Eq. (7),  $S_{s2}(k)$

and  $I_{s2}(w^{(n)})$  can be easily computed because  $T'_{s2}$  is known *a priori*. Hence, we need only to compute  $\delta_{s2}(k)$  in order to compute  $F'_{s2}(k)$ .

To compute  $\delta_{s2}(k)$ , we assume another virtual task  $\bar{\mathcal{M}}$  as follows:

$$\bar{\mathcal{M}}=(\bar{C},\ \bar{T},\ \bar{D}),$$

where  $\bar{T}=S_{s2}(k),\ \bar{D}=\bar{T}$  .

At the beginning of this section, we compute the safe capacity of the secondary server at priority level i by computing  $\delta_i(D_i)$ . Similarly, the amount of idle time between  $[0, S_{s2}(k))$  which has been unused by the tasks with priorities higher than or equal to  $\mathcal{M}_i$  corresponds to the upper bound for the execution time of the virtual task  $\bar{\mathcal{M}}$ . Then,  $\delta_{s2}(k)$  is computed by obtaining the maximum  $\bar{C}$  which can guarantee that the virtual task  $\bar{\mathcal{M}}$  is schedulable. Formally, we have:

$$\delta_{s2}(S_{s2}(k)) = \max\{\bar{C} \mid \bar{\mathcal{M}} \text{ is schedulable}\}. \tag{8}$$

The maximum  $\bar{C}$  which satisfies the condition in Eq. (8) is the solution w where  $w^{(n+1)} = w^{(n)}$  and  $w^n \leq \bar{D}$  to the following equation:

$$w = \bar{C} + I_i'(w) \tag{9}$$

where  $I_i'(w)$  denotes the interference caused by the tasks with higher than or equal priority to task i. A simple way of finding  $\bar{C}$  is to perform binary search for the interval  $[0, \bar{D})$  of which complexity is  $O(log_2\bar{D})$ . Actually, this approach may be somewhat expensive because, for each value  $t \in [0, \bar{D})$ , the worst-case response time formulation must be done for higher priority tasks. To avoid this complexity, Bernat also presents an effective way of computing  $\delta_i(k)$  by finding more tighter bounds. However, his approach is not so cost-effective for our case which targets at finding a specific  $F_i(k)$ .

We present a simple approach to reduce the test space. It is possible by using the fact that  $\bar{C}$  is actually the idle time unused by the tasks with higher than or equal to priorities than the secondary server. Using the definition of  $I_i'(w)$ , the interference of tasks with higher than or equal priority to  $\mathcal{M}_i$ , the upper bound for  $\bar{C}$  is given by:

$$\bar{C} \le S_{s2}(k) - I_i'(S_{s2}(k)) < S_{s2}(k) - \sum_{j \in hep(SS_2)} \left\lfloor \frac{S_{s2}(k)}{T_j} \right\rfloor C_j$$

(10)

where  $hep(SS_2)$  denotes the set of tasks with higher than or equal priority to the secondary server.

The lower bound for  $\bar{C}$  can also be tightened as follows. Given any time interval  $w=[t_1,\ t_2)$ , the worst-case number of instances of  $\mathcal{M}_j$  within the interval can approximate  $\left\lceil \frac{t_2-t_1}{T_j} \right\rceil +1$ . We can optimize this trivial bound using the analysis in [3]. The analysis

uses the worst-case response time of  $\mathcal{M}_j$ ,  $R_j$ . It classifies the instances into three cases according to their invocation time. As a result of analysis, it follows that the number of instances of  $\mathcal{M}_j$  within a given time interval w, denoted by  $\phi_j$  is given by:

$$\phi_{j} = \left\lceil \frac{w}{T_{j}} \right\rceil + f(j), \text{ where}$$

$$f(j) = \left\{ \begin{aligned} 1 & \text{if } R_{j} \ge T_{j} - \left\{ w - \left( \left\lfloor \frac{w}{T_{j}} \right\rfloor T_{j} + 1 \right) \right\} \\ 0 & \text{ otherwise} \end{aligned} \right.$$

(11)

For details, refer to [3].

The above formulation can be directly applied to finding the lower bound for  $\delta_i(k)$  by substituting w for  $S_{s2}(k)$ . Finally, we have:

$$\bar{C} \ge S_{s2}(k) - \sum_{j \in hep(SS_2)} \left( \left\lceil \frac{S_{s2}(k)}{T_j} \right\rceil + f(j) \right) C_j. \tag{12}$$

#### 3.3 Live Memory Analysis

We have proposed a three-step approach to find the worst-case live memory for the single server approach in [4]. According to the live memory analysis, the worst-case live memory  $L_k^*$  equals the sum of the worst-case global live memory  $L_{k,glob}^*$  and the worst-case local live memory  $L_{k,local}^*$ . Usually, the amount of global live objects is relatively stable throughout the execution of application because global objects are significantly longer-lived than local objects. On the other hand, the amount of local live objects continues to vary until the time at which the garbage collector is triggered. For this reason, we concentrate on the analysis of the worst-case local live memory.

The amount of live objects for each task depends not on the heap size but on the state of each task. Although the amount of live memory is a function of  $A_i$  and varies during the execution of a task instance, it is stabilized at the end of the instance. Therefore, we find the worst-case live local memory by classifying the task instances into two classes: active and inactive<sup>2</sup>. Accordingly, we set the amount of live memory for an active task  $\mathcal{M}_i$  to  $A_i$  in order to cover an arbitrary live memory distribution. By contrast, the amount of live memory for an inactive task  $\mathcal{M}_j$  converges  $\gamma_j A_j$  where  $\gamma_j$  denotes the stable live factor out of  $A_j$ . Consequently, the worst-case live local live memory is bounded by:

$$L_{k,local}^* = max(\sum_{\mathcal{M}_i \in active(t_s^k)} A_i + \sum_{\mathcal{M}_j \in inactive(t_s^k)} \gamma_j A_j)$$

(13)

where active(t) and inactive(t) denote the set of active tasks and the set of inactive tasks at time t, respectively. We also assume the amount of global live memory to be a constant  $L_{k,glob}^*$  because it is known to be relatively stable throughout the execution of the application. Then,  $L_k^*$  equals the sum of  $L_{k,local}^*$  and  $L_{k,glob}^*$ .

We now modify the live memory analysis slightly to cover the dual server approach. We first summarize the three-step approach as follows:

We regard a task as *active* if the task is running or preempted by higher priority tasks at time instant t. Otherwise, the task is regarded as *inactive*.

- Step 1. Find the active windows: For each tasks, find the time intervals in which the task instances are running or preempted by higher priority tasks, i.e., active. Those time intervals are referred as active windows and represented by  $\mathcal{A}_{i,j} = [\mathcal{S}_{i,j}, \mathcal{F}_{i,j}]$  where  $\mathcal{S}_{i,j}$  and  $\mathcal{F}_{i,j}$  denote the earliest start time and the latest completion time of  $\mathcal{M}_{i,j}$ , respectively. First, we put a restriction on the periods of mutators;  $\mathcal{M}_i$  is harmonic with respect to  $\mathcal{M}_1$  [6]. This constraint helps to prune the search space. Second, the search space is limited to a hyperperiod H. We compute  $\mathcal{S}_{i,j}$  from the worst-case completion time of a task instance  $\mathcal{M}_{\kappa,l}$  where  $\mathcal{M}_{\kappa}$  is the lowest priority task among the tasks such that their priorities are higher than that of  $\mathcal{M}_i$  and  $\exists l, (j-1)T_i = lT_k$  for  $1 \leq l \leq \frac{H}{T_k}$ . We also compute  $\mathcal{F}_{i,j}$  under the assumption that the total capacity of aperiodic server is used for GC, i.e., the garbage collector behaves like a periodic task. Then,  $\mathcal{F}_{i,j}$  equals the sum of  $(j-1)T_i$  and the worst-case response time of  $\mathcal{M}_i$ , denoted by  $R_i^s$ , including the interference caused by another periodic task with  $(C_i, T_i, D_i, A_i) = (server capacity, T_1, T_1, 0)$ .

- Step 2. Find the transitive preemption windows: Using the active windows found in Step 1, this step finds the preemption windows. The preemption window  $P_{\mathcal{M}_i \Rightarrow ... \Rightarrow \mathcal{M}_k}$  is the set of time intervals in which tasks  $\mathcal{M}_i$ , ...,  $\mathcal{M}_k$  are all active. They are equivalent to the intervals overlapped among active windows for mutator tasks. Those tasks are active because one of them is running and the others are preempted by higher priority tasks.

- Step 3. Compute the worst-case live memory: This step computes the worst-case local live memory using Eq. (13).

As to the live memory, the worst-case scenario is that a GC request is issued when all the tasks are active. Generally, the possibility of a certain task being active<sup>3</sup> is proportional to CPU utilization of given task set. Hence, we try to find the worst-case local live memory under the highest utilization attainable. For this purpose, we assume the CPU bandwidth reserved for GC is fully utilized because the CPU utilization of periodic tasks for given task set is fixed.

And therefore, we need a simple modification on the computation of active windows in order that it may include the interference caused by the secondary server. In Step 1 of our live-memory analysis,  $\mathcal{S}_{i,j}$  and  $\mathcal{F}_{i,j}$  determine the active window of  $\mathcal{M}_{i,j}$ . Because the computation of  $\mathcal{S}_{i,j}$  ignores the bandwidth reserved for GC, only the latest completion time  $\mathcal{F}_{i,j}$  should be recomputed. Suppose that  $R_i^{s'}$  denotes the worst-case response (completion) time of  $\mathcal{M}_i$ . Then, we can compute  $R_i^{s'}=w$  using the following recurrence relation:

$$w = C_i + \sum_{l \in hp(i)} \left\lceil \frac{w}{T_l} \right\rceil C_l \tag{14}$$

where hp(i) is the set of tasks, including the aperiodic servers, whose priorities are higher than that of  $\mathcal{M}_i$ . The only difference from the single server approach is that hp(i) does not always include the secondary server although it does include the primary server. This is because the secondary server may not have higher priority than that of  $\mathcal{M}_i$  whilst

<sup>&</sup>lt;sup>3</sup> In most cases, it means that the task is preempted by a higher priority task.

the primary server has the highest priority. Steps 2 and 3 are applied to the dual server approach without any modification. Example 1 clarifies the modified approach.

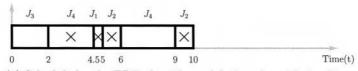

Example 1. Consider the task set whose parameters are as given in Table 2.

| Table 2. Example task set: $T_s$ | $L = 10, C_{s1} =$ | $1, T_{s2} =$ | $30, C_{s2} = 6$ |

|----------------------------------|--------------------|---------------|------------------|

|----------------------------------|--------------------|---------------|------------------|

|                 | $C_i$ | $T_i$ | $D_i$ | $A_i$ | $\gamma_i$ | $R_i^s$ |

|-----------------|-------|-------|-------|-------|------------|---------|

| $M_1$           | 2     | 10    | 10    | 988   | 0.43       | 3       |

|                 |       |       |       | 1028  |            |         |

| $M_3$           | 10    | 60    | 60    | 1200  | 0.38       | 29      |

| $\mathcal{M}_4$ | 15    | 120   | 120   | 1696  | 0.27       | 108     |

- Step 1. The active windows of periodic tasks in the example are

$$\begin{split} \mathcal{A}_{1,j} &= [10(j-1),\ 10(j-1)+3],\\ \mathcal{A}_{2,j} &= [30(j-1)+2,\ 30(j-1)+16],\\ \mathcal{A}_{3,j} &= [60(j-1)+6,\ 60(j-1)+29],\\ \mathcal{A}_{4,j} &= [120(j-1)+18,\ 120(j-1)+108],\ \text{where}\ 1 \leq j \leq \frac{120}{T_i} \ . \end{split}$$

- Step 2. Using the active windows found in Step 1, we can determine the preemption windows for the following combinations:  $\mathcal{M}_1 \Rightarrow \mathcal{M}_2$ ,  $\mathcal{M}_1 \Rightarrow \mathcal{M}_3$ ,  $\mathcal{M}_1 \Rightarrow \mathcal{M}_4$ ,  $\mathcal{M}_2 \Rightarrow \mathcal{M}_4$ ,  $\mathcal{M}_3 \Rightarrow \mathcal{M}_4$ , and  $\mathcal{M}_1 \Rightarrow \mathcal{M}_3 \Rightarrow \mathcal{M}_4$ .

- Step 3. As a result of Eq. (13),  $\mathcal{M}_1 \Rrightarrow \mathcal{M}_3 \Rrightarrow \mathcal{M}_4$  is the combination that maximizes the amount of local live memory. In this case,  $L_{k,local}^*$  is reduced by up to 13% compared with the trivial bound.

#### 3.4 Worst-Case Memory Requirement

As mentioned in Sect. 3.2, the worst-case memory requirement is derived from the sum of the amount of memory reserved for hard real-time periodic mutators and the worst-case live memory. Because the reserved memory depends on the worst-case GC time  $C_{GC}$  and vice versa, we need to compute the amount of reserved memory,  $M_{resv}$ , iteratively. First, we set the amount of memory allocated by all the mutators during a hyperperiod to the initial value of  $M_{resv}$ . This is because, even in the worst-case, a GC cycle must be completed within a hyperperiod. Thereafter, the algorithm computes  $M_{resv}$  using  $C_{GC}$  and  $R_{GC}$  recursively until  $M_{resv}^{(n+1)} = M_{resv}^{(n)}$ . We can easily compute  $C_{GC}$  using  $L_k^*$  obtained from the off-line live memory analysis [4]. The worst-case response time for GC can also be computed using Theorem 1 and 2. In summary,  $M_{resv}$  is the smallest

solution to the following recurrence relation:

$$\begin{cases} w^{(0)} = \sum_{i=1}^{n} \frac{H}{T_i} A_i \\ w^{(n+1)} = \sum_{i=1}^{n} \left\lceil \frac{R_{GC}(w^{(n)})}{T_i} \right\rceil A_i \end{cases}$$

(15)

where  $R_{GC}(w^{(n)})$  denotes the worst-case GC response time derived from the amount of memory reservation computed in the previous iteration. Finally, we can compute the system memory requirement using Eq. (15) in Sect. 2.

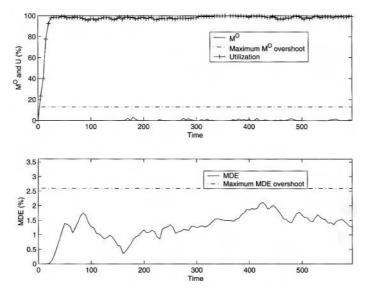

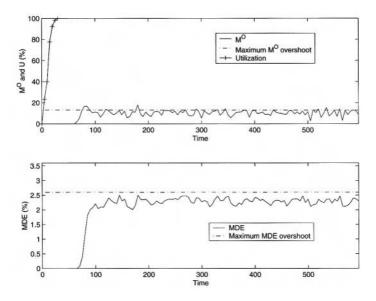

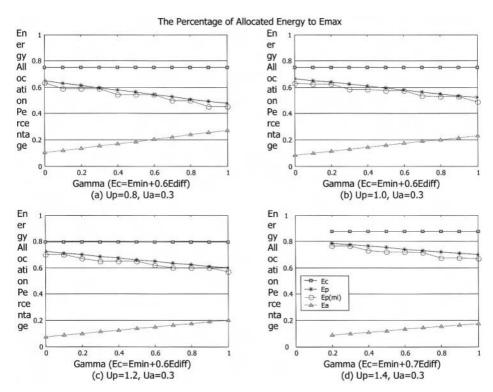

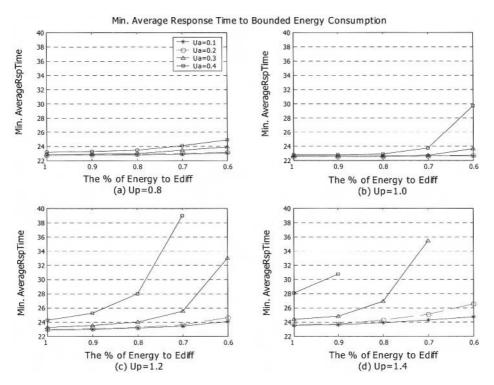

#### 4 Performance Evaluation

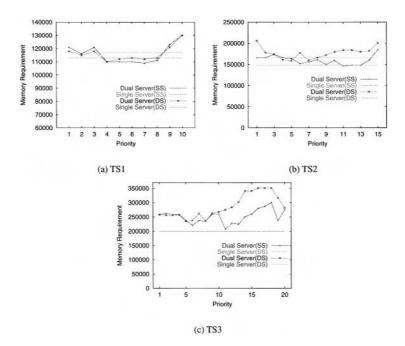

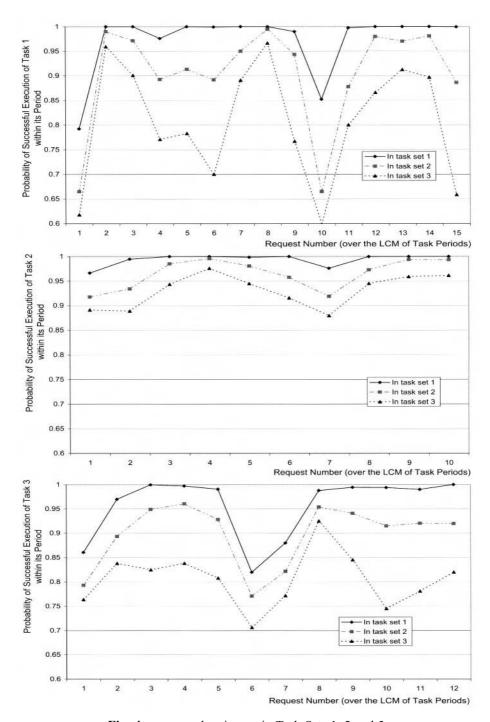

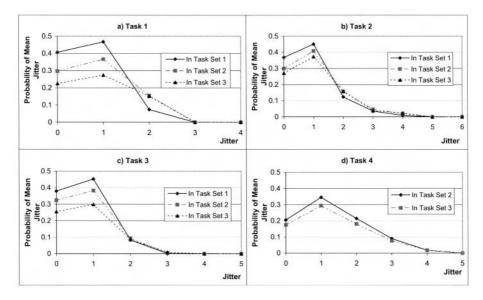

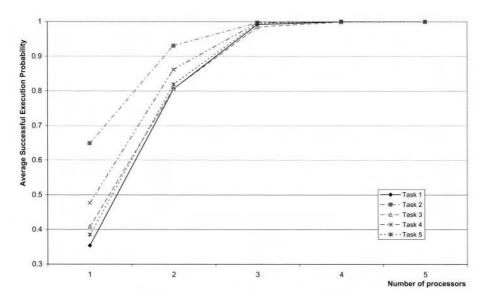

This section presents the performance evaluation of our scheme. We show the efficiency of our approach by evaluating memory requirement through extensive analysis. Analytic results are verified by simulation based on trace-driven data. Experiments are performed on the trace-driven data acquired from five control applications written in Java and three sets of periodic tasks created out of the sample applications. The CPU utilization for those three task sets of TS1, TS2, and TS3 are 0.673, 0.738, and 0.792, respectively. The parameters used in the computation of the worst-case garbage collection work are

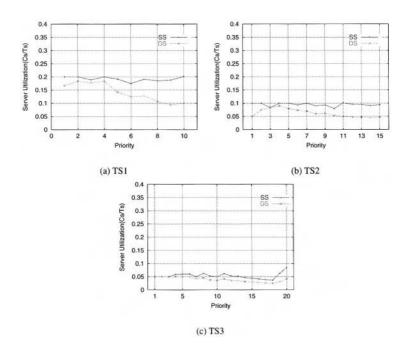

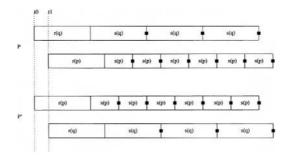

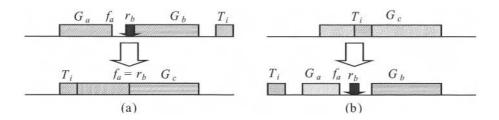

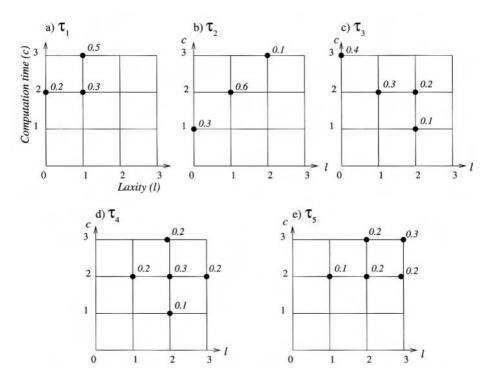

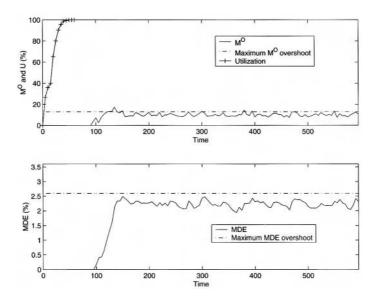

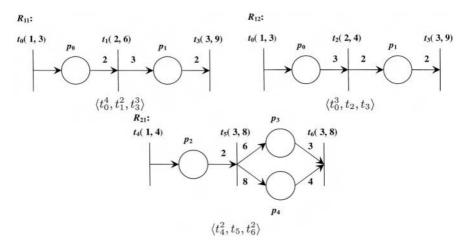

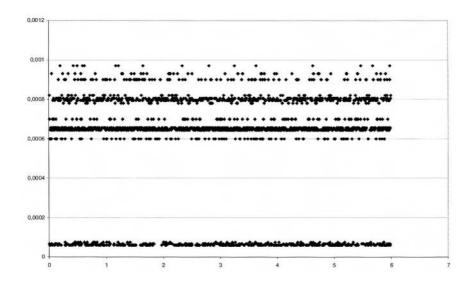

**Fig. 2.** Capacity of the secondary server at each priority level.

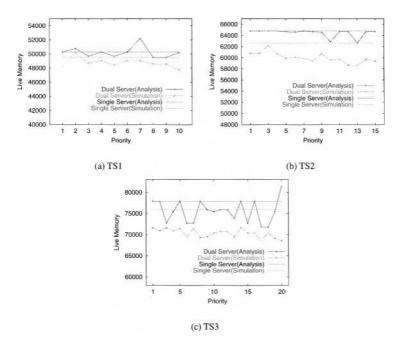

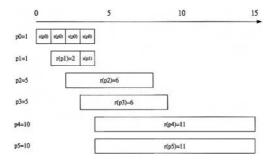

Fig. 3. Live memory of each task sets for the dual server approach.

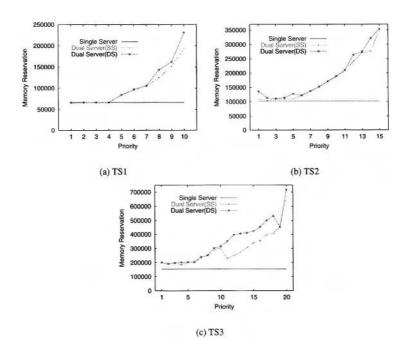

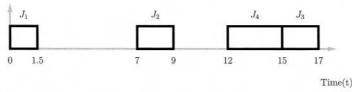

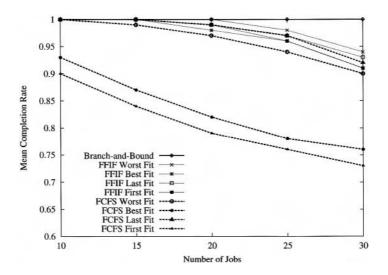

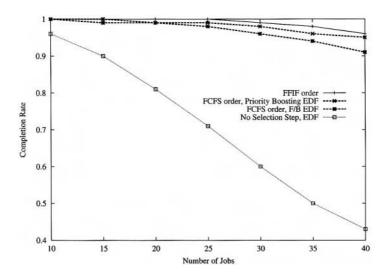

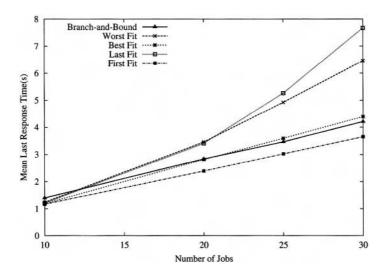

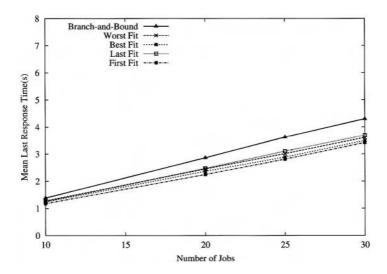

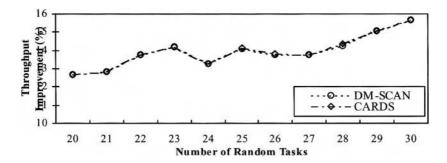

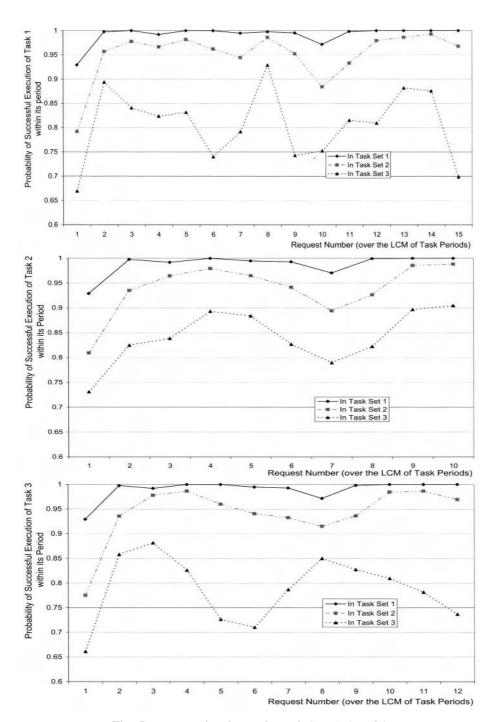

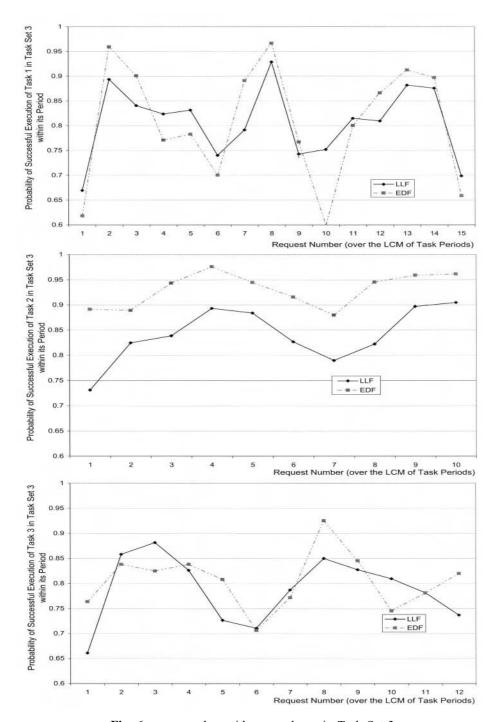

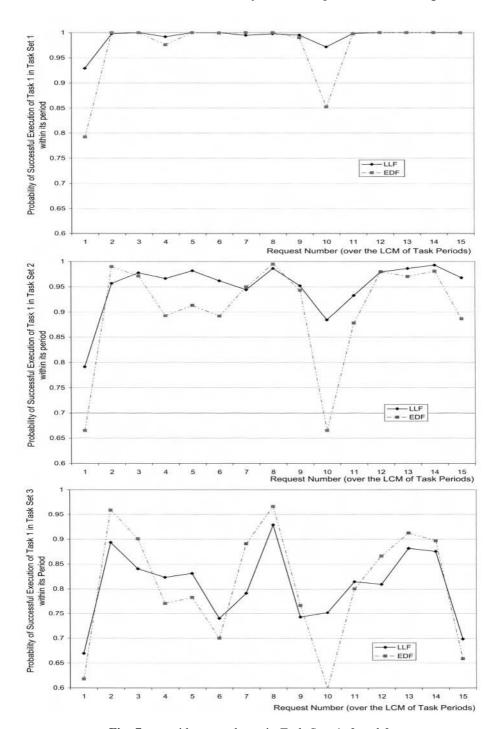

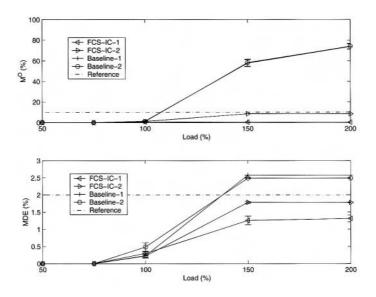

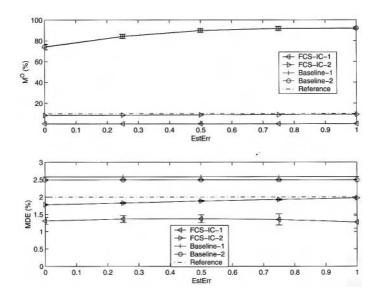

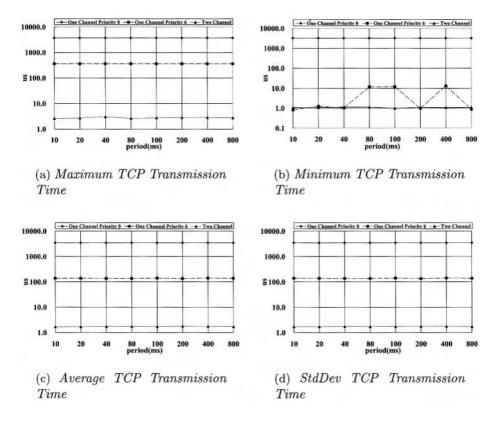

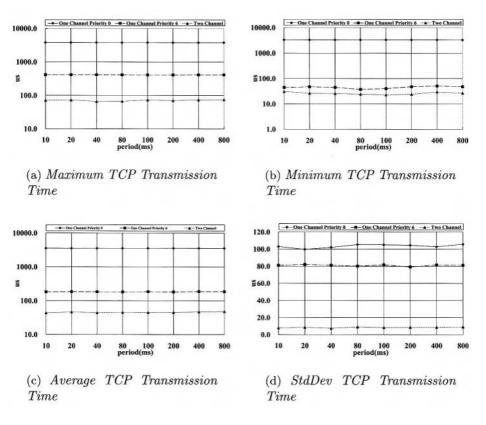

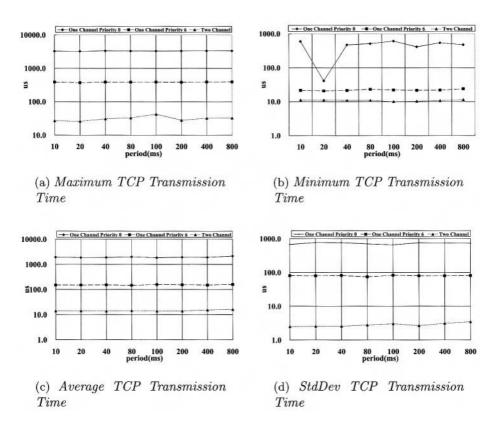

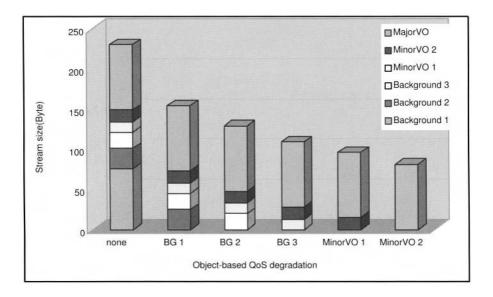

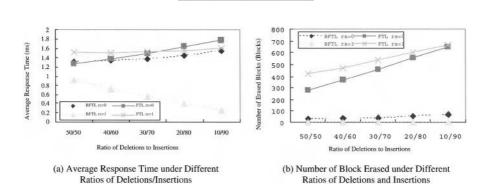

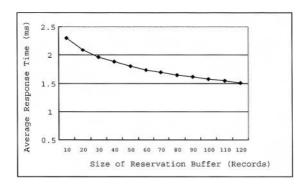

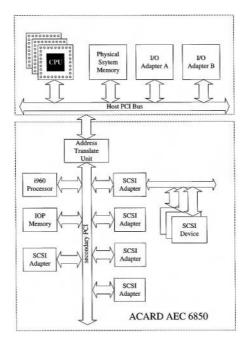

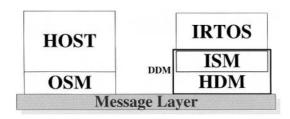

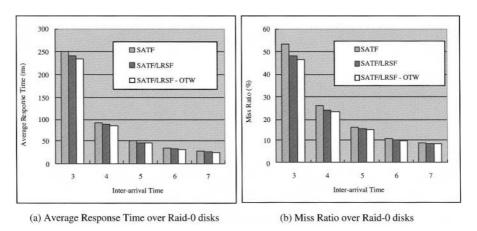

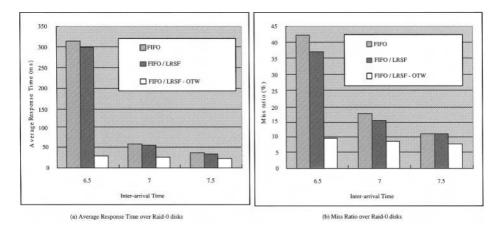

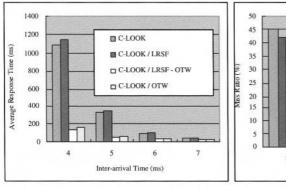

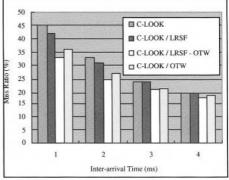

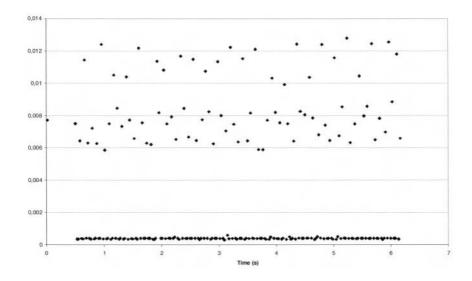

derived from a static measurement of the prototype garbage collector running on 50 MHz MPC860 with SGRAM. For details on the experiment environment, refer to [1]. Because the major goal of our approach is to reduce the worst-case memory requirement, our interest lies in the following three parameters. First, we compare the worst-case live memory of the dual server with that of the single server. Second, we analyze the worst-case memory reservation of both schemes. Third, we conduct a series of simulations to compare the feasible memory requirement. Figs. 3,4, and 5 show performance evaluation results.

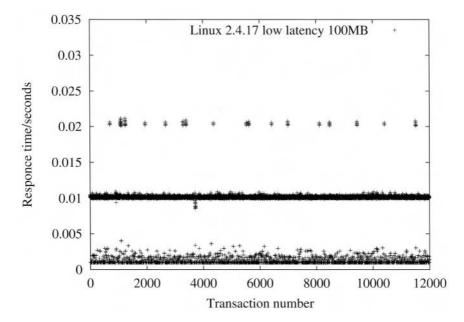

We first compute the capacity of the secondary server at each priority level using traditional worst-case response time formulation. For this purpose, the capacity of the primary server is set to  $C_{s1}=1$  for simplicity. The only job of the primary server is to flip two semispaces and to initialize the heap space. As shown in [3], efficient hardware support enables the memory initialization to be done within hundreds of microseconds. Hence, we make this assumption without loss of generality. Fig. 2 illustrates the capacity of the secondary server for the SS and the DS. The x axis is the priority level and the y axis is the maximum utilization that can be allocated to the secondary server. In all the graphs shown in this section, the lower the priority level in the graph the higher the actual priority is. And, the secondary server has higher priority than that of a periodic task which has identical period with it. The DS algorithm can also be directly applied to our approach. The graphs in Fig. 2 show that the capacity of the secondary server for the DS is generally smaller than that of the SS. As pointed out in [7], for the DS, the

maximum server utilization occurs at low capacities; in other words, at high priorities under the RM policy. This is because the larger the capacity the larger the *double hit* effect, and therefore the lower the total utilization. However, as can be seen in Fig. 2, there is little difference in maximum server utilization of both schemes.

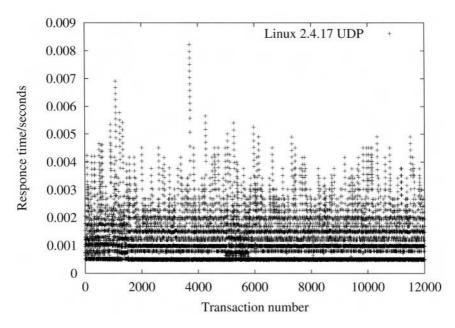

Fig. 3 illustrates the worst-case local live memory derived from the simulation and the analysis for the dual server approach. For comparison, the worst-case local live memory acquired from the simulation and the analysis for the single server approach is also presented. These results demonstrate that the analytic bound accords well with the simulation bound. The dual server approach also may reduce the worst-case local live memory by up to 8 % compared with the single server approach. It results from the fact that the dual server approach causes smaller interference over mutator tasks compared with the single server approach.

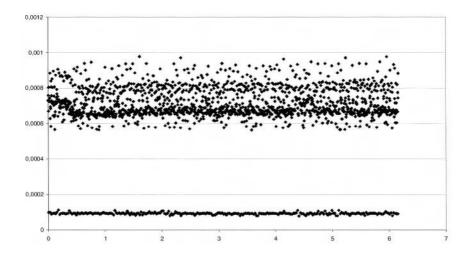

We also compare the memory reservation of the dual server approach with that of the single server approach. Fig. 4 illustrates the worst-case memory reservation for each task set. The graphs show that, at relatively high priority level, the dual server approach can provide comparable performance to the single server approach. The results also demonstrate that noticeable differences in memory reservation are observed from the priority levels 5 in TS1,7 in TS2, and 7 in TS3, respectively. For the DS, we can find that at those priority levels the server utilization starts to decrease. Following Theorem 2 in Sect. 3.2, this server utilization has a great impact on the worst-case GC response time, and thus memory reservation. On the other hand, for the SS, the performance begins

Fig. 4. Memory reservation of given task sets.

to degrade at certain priority level though the server utilization has relatively uniform distribution. This is because the period of a virtual task representing the SS dual server is much longer than that of the DS server, which yields longer GC response time. For details, see Theorem 1 in Sect. 3.2.

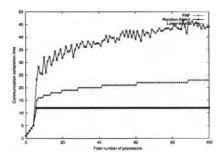

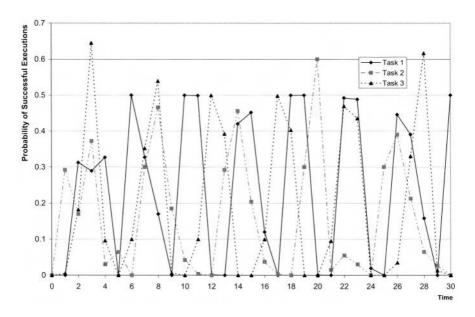

Fig. 5 compares the feasible memory requirements of both schemes. We mean *feasible* memory requirement by the amount of heap memory to guarantee hard deadlines without memory shortage under a specific memory consumption behavior. In our study, the feasible memory requirement is found by iterative simulation runs. We regard a given memory requirement as feasible if no garbage collection errors and deadline misses are reported after 100 hyperperiods runs. In Fig. 5, the SS-based dual server approach provides feasible memory requirement comparable to the single server approach for all the task sets. For TS3, the single server approach remarkably outperforms the dual server approach. This is because the periodic utilization of TS3 is relatively high, and therefore the CPU utilization allocated for the secondary server is smaller than the cases for TS1 and TS2. A noticeable performance gap between the SS-based single server and the SS-based dual server is found in Fig. 5 (c). At the priority level 18, the performance gap between two approaches is maximized because the CPU utilization allocated for the secondary server is minimized at this priority level as shown in Fig. 2. It results in longer GC response time, and thus large heap memory is needed.

The results also report that the DS provides comparable performance to the SS at high priorities although, at low priorities, the SS generally outperforms the DS. For TS1,

Fig. 5. Feasible memory requirement of given task sets for the dual server.

the performance gap between two schemes is within 2.8 %. Although the capacities of the SS is much larger than those of the DS at low priority levels, the double hit effect offsets the difference. However, for TS3, a noticeable performance gap is observed at low priority levels. This is because the periodic utilization of TS3 is quite high, and therefore the double hit effect diminishes at low priorities. Although the DS may not provide stable performance compared with the SS, it can provide comparable performance to, even better than at some configuration, the SS. And, it has another advantage over the SS; its implementation and run-time overheads are quite low. In summary, the DS is still an attractive alternative to the SS in terms of scheduling-based garbage collection.

#### 5 Conclusions

We have proposed a new scheduling-aware real-time garbage collection scheme. Our previous work [1] employed single aperiodic server to service garbage collection requests. By integrating task scheduling with garbage collection algorithm, the scheme achieves small memory footprint while guaranteeing hard deadlines. However, this scheme is sometimes impractical because it may inevitably not reserve sufficiently large server capacity. A new scheduling-aware garbage collection scheme based on dual aperiodic servers is introduced to overcome the limitation of the single server approach while achieving similar performance compared with the single server approach. The results obtained in this paper are summarized as follows. In general, the dual server approach shows comparable performance to the single server whilst it enables more flexible system design. In addition, the DS can be an alternative solution to the scheduling-aware garbage collection scheme. Simulation results show that it can provide similar performance to the SS with smaller implementation and run-time overheads.

#### References

- Kim, T., Chang, N., Shin, H.: Joint scheduling of garbage collector and hard real-time tasks for embedded applications. Journal of Systems and Software 58 (2001) 245–258

- Liu, C.L., Layland, J.W.: Scheduling algorithms for multiprogramming in a hard real-time environment. Journal of the ACM 20 (1973) 46–61

- Kim, T., Chang, N., Kim, N., Shin, H.: Scheduling garbage collector for embedded real-time systems. In: Proceedings of the ACM SIGPLAN 1999 Workshop on Languages, Compilers and Tools for Embedded Systems. (1999) 55–64

- Kim, T., Chang, N., Shin, H.: Bounding worst case garbage collection time for embedded real-time systems. In: Proceedings of The 6th IEEE Real-Time Technology and Applications Symposium. (2000) 46–55

- 5. Bernat, G.: Specification and Analysis of Weakly Hard Real-Time Systems. Ph.D. Thesis, Universitat de les Illes Balears, Spain (1998)

- Gerber, R., Hong, S., Saksena, M.: Guaranteeing end-to-end timing constraints by calibrating intermediate processes. In: Proceedings of Real-Time Systems Symposium. (1994) 192–203

- Bernat, G., Burns, A.: New results on fixed priority aperiodic servers. In: Proceedings of Real-Time Systems Symposium. (1999) 68–78

## On the Composition of Real-Time Schedulers\*

Weirong Wang and Aloysius K. Mok

Department of Computer Sciences University of Texas at Austin Austin, Texas 78712-1188 {weirongw,mok}@cs.utexas.edu

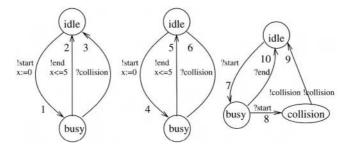

**Abstract.** A complex real-time embedded system may consist of multiple application components each of which has its own timeliness requirements and is scheduled by component-specific schedulers. At run-time, the schedules of the components are integrated to produce a system-level schedule of jobs to be executed. We formalize the notions of schedule composition, task group composition and component composition. Two algorithms for performing composition are proposed. The first one is an extended Earliest Deadline First algorithm which can be used as a composability test for schedules. The second algorithm, the Harmonic Component Composition algorithm (HCC) provides an online admission test for components. HCC applies a rate monotonic classification of workloads and is a hard real-time solution because responsive supply of a shared resource is guaranteed for in-budget workloads. HCC is also efficient in terms of composability and requires low computation cost for both admission control and dispatch of resources.

#### 1 Introduction

The integration of components in complex real-time and embedded systems has become an important topic of study in recent years. Such a system may be made up of independent application (functional) components each of which consists of a set of tasks with its own specific timeliness requirements. The timeliness requirements of the task group of a component is guaranteed by a scheduling policy specific to the component, and thus the scheduler of a complex embedded system may be composed of multiple schedulers. If these components share some common resource such as the CPU, then the schedules of the individual components are interleaved in some way. In extant work, a number of researchers have proposed algorithms to integrate real-time schedulers such that the timeliness requirements of all the application task groups can be simultaneously met. The most relevant work in this area includes work in "open systems" and "hierarchical schedulers" which we can only briefly review here. Deng and Liu proposed the open system environment, where application components may be admitted

<sup>\*</sup> This work is supported in part by a grant from the US Office of Naval Research under grant number N00014-99-1-0402 and N00014-98-1-0704, and by a research contract from SRI International under a grant from the NEST program of DARPA

J. Chen and S. Hong (Eds.): RTCSA 2003, LNCS 2968, pp. 18-37, 2004.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2004

online and the scheduling of the component schedulers is performed by a kernel scheduler [2]. Mok and Feng exploited the idea of temporal partitioning [6], by which individual applications and schedulers work as if each one of them owns a dedicated "real-time virtual resource". Regehr and Stankovic investigated hierarchical schedulers [8]. Fohler addressed the issue of how to dynamically schedule event-triggered tasks together with an offline-produced schedule for time-triggered computation [3]. In [10] by Wang and Mok, two popular schedulers: the cyclic executive and fixed-priority schedulers form a hybrid scheduling system to accommodate a combination of periodic and sporadic tasks.

All of the works cited above address the issue of schedule/scheduler composition based on different assumptions. But what exactly are the conditions under which the composition of two components is correct? Intuitively, the minimum guarantee is that the composition preserves the timeliness of the tasks in all the task groups. But in the case an application scheduler may produce different schedules depending on the exact time instants at which scheduling decisions are made, must the composition of components also preserve the exact schedules that would be produced by the individual application schedulers if they were to run on dedicated CPUs? Such considerations may be important if an application programmer relies on the exact sequencing of jobs that is produced by the application scheduler and not only the semantics of the scheduler to guarantee the correct functioning of the application component. For example, an application programmer might manipulate the assignment of priorities such that a fixed priority scheduler produces a schedule that is the same as that produced by a cyclic executive for an application task group; this simulation of a cyclic executive by a fixed priority scheduler may create trouble if the fixed priority scheduler is later on composed with other schedulers and produces a different schedule which does not preserve the task ordering in the simulated cyclic executive. Hence, we need to pay attention to semantic issues in scheduler composition.

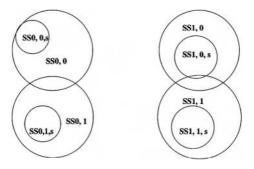

In this paper, we propose to formalize the notions of composition on three levels: schedule composition, task group composition and component composition. Based on the formalization, we consider the questions of whether two schedules are composable, and how components may be efficiently composed. Our formalization takes into account the execution order dependencies (explicit or implicit) between tasks in the same component. For example, in cyclic executive schedulers, a deterministic order is imposed on the execution of tasks so as to satisfy precedence, mutual exclusion and other relations. As is common practice to handle such dependencies, sophisticated search-based algorithms are used to produce the deterministic schedules offline, e.g., [9]. To integrate such components into a complex system, we consider composition with the view that: First, the correctness of composition should not depend on knowledge about how the component schedules are produced, i.e., compositionality is fundamentally a predicate on schedules and not schedulers. Second, the composition of schedules should be *order preserving* with respect to its components, i.e., if job x is scheduled before job y in a component schedule, then job x is still scheduled before y in the integrated system schedule. Our notion of *schedule composition* is an interleaving of component schedules that allows preemptions between jobs from different components.

The contributions of this paper include: formal definitions of schedule composition, task group composition and component composition, an optimal schedule composition algorithm for static schedules and a harmonic component composition algorithm that has low computation cost and also provides a responsiveness guarantee. The rest of the paper is organized as follows. Section 2 defines basic concepts used in the rest of the paper. Section 3 addresses schedule composition. Section 4 defines and compares task group composition and component composition. Section 5 defines, illustrates and analyzes the Harmonic Component Composition approach. Section 6 compares HCC with related works. Section 7 concludes the paper by proposing future work.

#### 2 Definitions

#### 2.1 Task Models

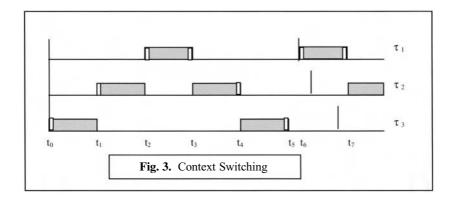

Time is defined on the domain of non-negative real numbers, and the time interval between time b and time e is denoted by (b,e). We shall also refer to a time interval (i,i+1) where i is a non-negative integer as a time unit. A resource is an object to be allocated to tasks. It can be a CPU, a bus, or a packet switch, etc. In this paper, we shall consider the case of a single resource which can be shared by the tasks and components, and preemption is allowed. We assume that context switching takes zero time; this assumption can be removed in practice by adding the appropriate overhead to the task execution time.

A job is defined by a tuple of three attributes (c, r, d) each of which is a non-negative real number:

- -c is the *execution time* of a job, which defines the amount of time that must be allocated to the job;

- -r is the *ready time* or *arrival time* of the job which is the earliest time at which the job can be scheduled;

- -d is the *deadline* of the job which is the latest time by which the job must be completed.

A task is an infinite sequence of jobs. Each task is identified by a unique ID i. A task is either periodic or sporadic.

The set of periodic tasks in a system is represented by  $T_p$ . A periodic task is denoted by (i,(c,p,d)), where i identifies the task, and tuple (c,p,d) defines the attributes of its jobs. The jth job of i is denoted by job (i,j).

Suppose X identifies an object and Y is one of the attributes of the object. we shall use the notation X.Y to denote the attribute Y of X. For instance, if (i,j) identifies a job, then (i,j).d denotes the deadline of job (i,j).

The attributes in the definition of a periodic task, c, p and d, are non-negative real numbers:

- -c is the *execution time* of a task, which defines the amount of time that must be allocated to each job of the task;

- -p is the *period* of the task;

- d is the *relative deadline* of the task, which is the maximal length of time by which a job must be completed after its arrival. We assume that for every periodic task,  $c \le d \le p$ .

If a periodic task i is defined by (c, p, d), job (i, j) is defined by  $(c, j \cdot p, j \cdot p + d)$ . A sporadic task is denoted by a tuple (i, (c, p, d)), where i identifies the task, and (c, p, d) defines the attributes of its jobs, as follows: The jth job of sporadic task i is identified as job (i, j),  $j \ge 0$ . The arrival times of jobs of a sporadic task are not known a priori and are determined at run time by an arrival function A that maps each job of a sporadic task to its arrival time for the particular run:

$A :: T_s \times \mathbf{N} \to \mathbf{R}$ , where **N** is the set of natural numbers and **R** is the set of real numbers.

A(i, j) = t if the job (i, j) arrives at time t.

$A(i, j) = \perp$  if the job (i, j) never arrivals.

The attributes c and d of a sporadic task are defined the same as those of a periodic task. However, attribute p of a sporadic task represents the *minimal* interval between the arrival times of any two consecutive jobs. In terms of the function A,  $A(i,(j+1)) - A(i,j) \ge p$  if A(i,(j+1)) is defined.

For a sporadic task (i, (c, p, d)), job (i, j) is defined as (c, A(i, j), A(i, j) + d).

A task group TG consists of a set of tasks (either periodic or sporadic). We shall use STG to denote a set of task groups. The term component denotes a task group and its scheduler. Sometimes we call a task group an application task group to emphasize its association with a component which is one of many applications in the system.

#### 2.2 Schedule

A resource supply function Sup defines the maximal time that can be supplied to a component from time 0 to time t. Time supply function must be monotonically non-decreasing. In other words, if  $t \le t'$ , then  $Sup(t) \le Sup(t')$ .

The function S maps each job to a set of time intervals:

$S :: TG \times \mathbb{N} \to \{(\mathbb{R}, \mathbb{R})\}$  where TG is a task group, and  $\mathbb{N}$  and  $\mathbb{R}$  represent the set of natural numbers and the set of real numbers respectively.

$S(i,j) = \{(b_{i,j,k}, e_{i,j,k}) | 0 \le k < h\}$  where k and h are natural numbers.

S is a *schedule* of TG under supply function Sup if and only if all of the following conditions are satisfied:

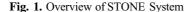

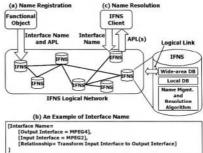

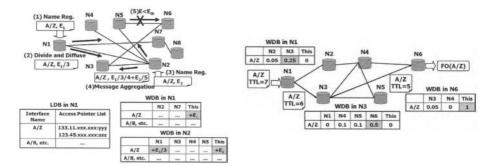

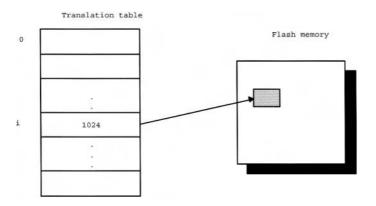

- Constraint 1: For every job (i, j), every time interval assigned to it in the schedule must be assigned in a time interval allowed by the supply function, i.e., for all  $(b, e) \in S(i, j)$ , Sup(e) - Sup(b) = e - b.