# NOGATECH INC.

Nogatech reserves the right to make changes without further notice to any product herein. Nogatech makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Nogatech assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Nogatech products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Nogatech product could create a situation where personal injury or death may occur.

NT1003-1 USBVision

Full Video Interface solution for Video via USB

Nov-1998

# **Table of Contents:**

| 1. General Architecture                  | I |

|------------------------------------------|---|

| 2. Registers Bank (Control and Status)14 | 4 |

| 3. Power Management                      | 1 |

| 4. Video Input Interface                 | 2 |

| 5. DRAM Control and Interface            | 3 |

| 6. Camera Control Serial Port            | 6 |

| 7. External EEPROM                       | 3 |

| 8. NT1003-1 USB and Status Registers     | 9 |

| 9. Programmable I/O Pins                 | 0 |

| 10. Software Package                     |   |

#### NT1003-1

#### USBVision

Full Video Interface solution for Video via USB

The NT1003-1 is an ideal solution for digital camera manufacturers who want to utilize the Universal Serial Bus as an interface between the camera and the computer. Using a proprietary video compression algorithm, the NT1003-1 enables a throughput of up to 30f/s for CIF size images, utilizing only half of total available bandwidth of the USB port. An appropriate software driver in the host computer decompresses the incoming USB data, consuming only 25% of CPU time (@ CIF 30f/s). The resulting digital image quality is almost identical to the source coming from the camera. This monolithic feature of the NT1003-1 makes it ideal to be used as a one chip solution for a very low cost USB portable Video Camera.

The NT1003-1 can also be used to transfer video sequence from a Composite-Video source to the computer for editing (this requires adding some video decoder chip). Due to the fact that the USB bandwidth used by the NT1003-1 can be adjusted (0.5-8.0 Mbit/sec), the video software application always has enough time to record the incoming compressed video data on disk and display full frame-rate on screen simultaneously.

#### Features

- Up to 30 frames/sec @ CIF size (352x288 pixels)

- Supports VGA-size cameras

- Connects to various YUV sources (4:4:4, 4:2:2, 16 or 8-bit bus)

- Selectable Raw/Compressed video out

- Variable Compression ratio

- Selectable USB bandwidth (0.5Mbps 7.5Mbps in 0.5Mbps steps):

- Built-in programmable true scaler (Down Scale horizontal and vertical)

- Built in Zoom and Pan Capabilities

- Supports high resolution still image capture (640x480 pixels)

- Selectable Data/Clock serial protocols ideal for camera control

- General Programmable I/O pins enable software to control remote devices

- Low power consumption (240mW @ 3.3V) can use USB power source

- Direct connection to USB port

- Handles device Power Management (complies with USB standard spec.)

- Fits Intel's MMX<sup>®</sup> concept

- Supports most popular software applications that require digital video.

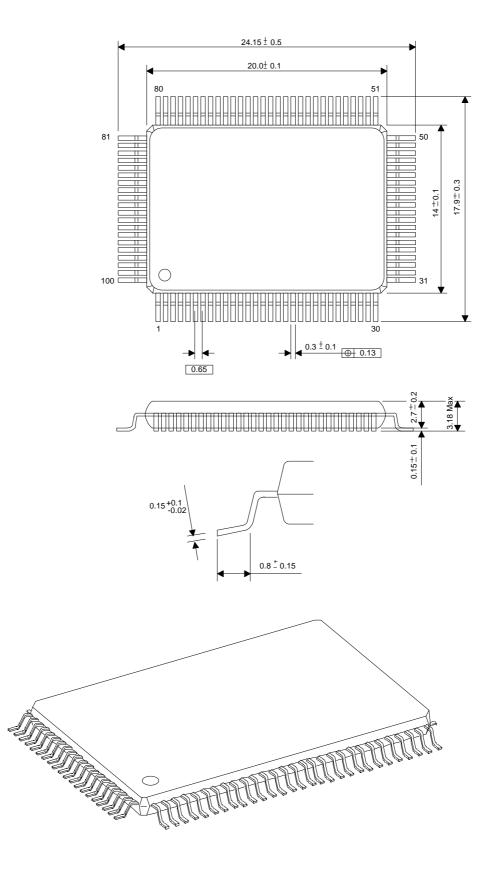

- 100-pin PQFP package

NT1003-1

## **Product Description**

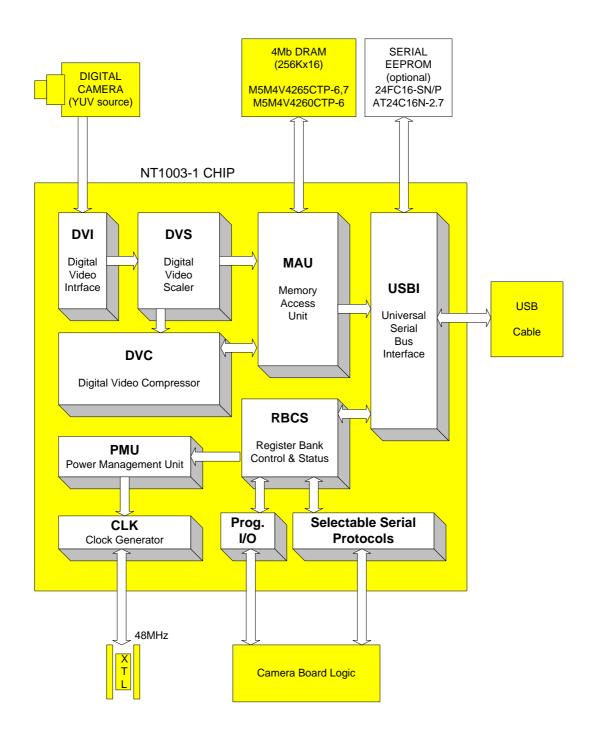

Refer to Fig.1 for an internal Block Diagram of the NT1003-1.

Fig.1 NT1003-1 Block Diagram

The NT1003-1 utilizes a single USB port to enable the host computer to access two different data channels simultaneously. These two channels are the Digital Video input (8Mbit/sec) and I/O control (internal registers, programmable I/O pins, and selectable Data/Clock serial protocols).

Due to the sophisticated architecture and protocol of the USB, the software application is not required to take care of the time-sharing management of several tasks using a single serial bus; This is handled by the lower-level drivers, so that the application program can access each function of the NT1003-1 as if the component was connected to the computer's parallel bus.

In normal operation, the NT1003-1 will provide the system with the following services:

- **Compressed Video Channel:** The NT1003-1 connects to Y/U/V video digital source, scales the image on the fly horizontally and vertically, compresses the data down to 0.5-8Mbit/sec, and sends it to the host computer via the USB port. The NT1003-1 scaler supports zoom-in like effects, by applying combinations of zooming and cropping built-in functions. The unique method of compression is a special design of Nogatech, to allow easy and fast de-compression in software only means. The de-compression software driver supplied with the NT1003-1, will accept the compressed data and convert it back to standard video formats in less time than it takes to read raw video from any external port. Still images can be captured and sent via the USB in the best quality and resolution that the camera can provide.

- **Camera Control:** Camera (or any video source) control and status monitoring can be carried out by a built-in serial interface, or direct I/O pins. The serial interface supports some commonly used serial protocols. These ports can be used by the application software to control and monitor some other remote devices as well. In a Video Conference application, this allows the local or remote user to set the focus, zoom, and other parameters of the camera, or even to switch the camera to the power-down mode. The NT1003-1 also supports usage of an external capture button that is mounted on the camera board and used for capturing video frames on the host computer disk (this is application dependent; the NT1003-1 only delivers the capture command signaling from button to host computer via USB).

NT1003-1

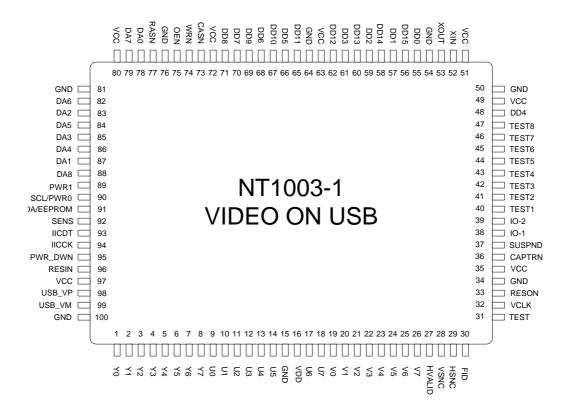

### **Pin Assignments (Top View)**

| PIN DESCRIPTIONS |

|------------------|

|------------------|

| PIN NUMBER                   | SIGNAL | I/O | DESCRIPTION                                                                                                                                                                          |

|------------------------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35,49,51,63,<br>72,80,97     | VCC    |     | Digital 3.3V power supply                                                                                                                                                            |

| 16                           | VDD    |     | 3.3V/5V power supply for video input buffers (pins 1-32 only)                                                                                                                        |

| 15,34,50,54,64,<br>76,81,100 | GND    |     | Digital ground connection                                                                                                                                                            |

| 1-8                          | Y0-Y7  | Ι   | Video Luminance input from camera. The NT1003-1 uses the VCLK input to sample this bus. These input pins are 5-volt tolerant.                                                        |

| 9-14,17-18                   | U0-U7  | Ι   | Video Chroma U-component input from camera. The NT1003-1 uses<br>the VCLK input to sample this bus. These input pins are 5-volt<br>tolerant. Should be connected to GND if not used. |

| 19-26                        | V0-V7  | Ι   | Video Chroma V-component input from camera. The NT1003-1 uses<br>the VCLK input to sample this bus. These input pins are 5-volt<br>tolerant. Should be connected to GND if not used. |

| 27                           | HVALID | Ι   | Video Clock Enable input qualifier. This input pin is 5-volt tolerant.<br>Should be connected to GND if not used.                                                                    |

| 28                           | VSNC   | Ι   | Video Vertical-Sync input signal from camera. This input pin is 5-<br>volt tolerant. Should be connected to GND if not used.                                                         |

| 29                           | HSNC   | Ι   | Video Horizontal-Sync input signal from camera. This input pin is 5-<br>volt tolerant. Should be connected to GND if not used.                                                       |

| 30                           | FID    | Ι   | Video Field-ID input signal from camera. This input pin is 5-volt tolerant. Should be connected to GND if not used.                                                                  |

| 31                           | TEST   | Ι   | This pin must be connected to GND.                                                                                                                                                   |

| 32                           | VCLK   | Ι   | Video Pixel-Clock input from camera. This input pin is 5-volt tolerant, and has a C-mos Schmitt- Trigger characteristics.                                                            |

## NT1003-1

Data Sheet

#### PIN DESCRIPTIONS (continued)

| PIN NUMBER       | SIGNAL      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33               | RESON       | Ο   | General Reset output. This output is active low, and it reflects the<br>Power-On Reset and all the following USB-Reset events that are<br>generated by host computer. This pin is an Open Drain output.                                                                                                                                                                                                                                                                                                                         |

| 36               | CAPTRN      | Ι   | Capture Command input. This input has an internal pull-up to Vcc.<br>When forced to '0', host computer is automatically informed that a<br>video frame capture was requested by user. This input is Schmitt-<br>Trigger type.                                                                                                                                                                                                                                                                                                   |

| 37               | SUSPND      | 0   | USB Suspend mode control output. This pin is an Open Drain output.<br>A Power-On Reset or a USB-Reset clear this output to 0 volt; it is set<br>to high-z when the NT1003-1 enters the Suspend mode, and cleared<br>back to '0' upon detection of Resume condition.                                                                                                                                                                                                                                                             |

| 38-39            | IO-1 - IO-2 | I/O | General Programmable I/O pins. Each of these 2 pins has an Open<br>Drain output, and it is supposed to be connected to an external pull-up<br>resistor to Vcc. The host uses these pins as programmable output<br>ports by writing '0' or '1' to set them to 0-volt or Vcc respectively. By<br>writing '1' and read back, the host can use these pins as input ports -<br>as this allows any external source to force the pull-up resistor. These<br>outputs are temporarily forced to high-z while in the Suspend<br>position. |

| 40               | TEST1       | Ι   | This pin must be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 41               | TEST2       | 0   | This pin must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 42               | TEST3       | 0   | This pin must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 43               | TEST4       | Ι   | This pin must be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 44               | TEST5       | 0   | This pin must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 45               | TEST6       | 0   | This pin must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 46               | TEST7       | 0   | This pin must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 47               | TEST8       | 0   | This pin must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 52               | XIN         | Ι   | Crystal Oscillator input pin (48 MHz). Crystal frequency must have<br>not worse than 100 PPM accuracy. 3rd harmony crystal is used.                                                                                                                                                                                                                                                                                                                                                                                             |

| 53               | XOUT        | 0   | Crystal Oscillator output pin (48 MHz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 48, 55-62, 65-71 | DD0-DD15    | I/O | DRAM Data bus input/output pins. These pins have internal Pull-Up resistors, and are temporarily forced to High-Z while in the Suspend position                                                                                                                                                                                                                                                                                                                                                                                 |

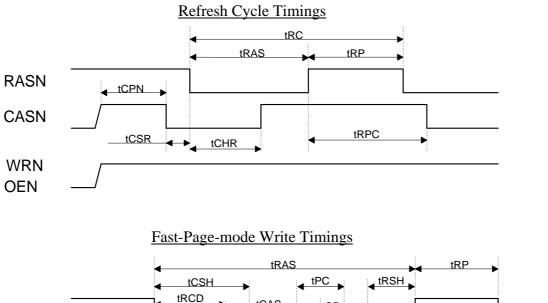

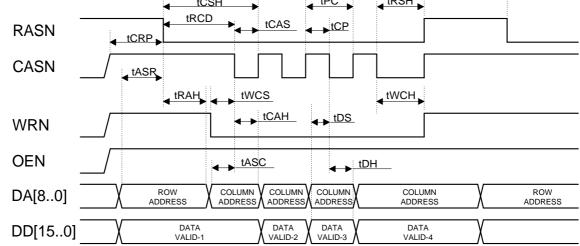

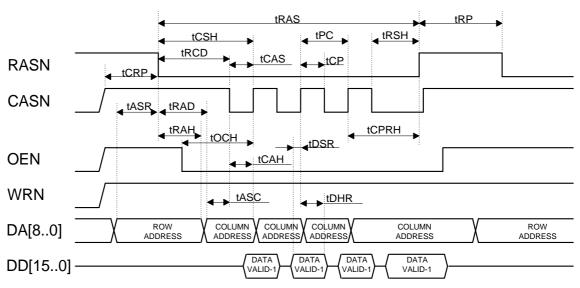

| 73               | CASN        | 0   | DRAM Column-Select control signal. This 8-mA output is designed<br>to drive 2 input pins of the external DRAM that are tied together<br>(LCAS+UCAS). This output is temporarily forced to '1' while in the<br>Suspend position.                                                                                                                                                                                                                                                                                                 |

| 74               | WRN         | 0   | DRAM Write control signal. This output is temporarily forced to '1' while in the Suspend position.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 75               | OEN         | 0   | DRAM Read control signal. This output is temporarily forced to '1' while in the Suspend position.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 77               | RASN        | 0   | DRAM Row-Select control signal. This output is temporarily forced to '1' while in the Suspend position.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 78-79, 82-88     | DA0-DA8     | 0   | DRAM Row/Column Address-bus. These outputs are temporarily forced to '0' while in the Suspend position.                                                                                                                                                                                                                                                                                                                                                                                                                         |

## NT1003-1

Data Sheet

#### PIN DESCRIPTIONS (continued)

| PIN NUMBER | SIGNAL     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 89         | PWR1       | Ι   | MSbit of Device Power Code. The voltage level in this input (Vcc or GND) is used by the NT1003-1 as the MSbit of the Device Power Code for the USB Device Descriptor. If an external EEPROM exists, this input is ignored.                                                                                                                                                                                                           |

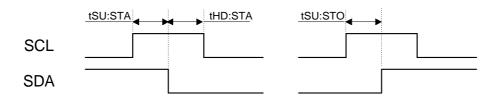

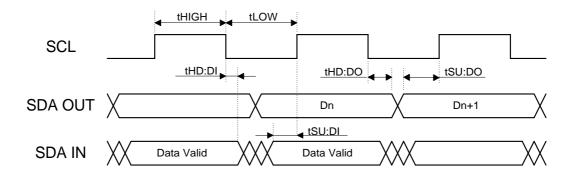

| 90         | SCL/PWR0   | I/O | Serial EEPROM clock signal, and LSbit of Device Power Code. If an EEPROM was detected, then this pin is used as the EEPROM clock output signal; otherwise its voltage (Vcc or GND) is used by the NT1003-1 as the LSbit of the Device Power Code for the USB Device Descriptor. This pin is temporarily forced to '1' while in the Suspend position.                                                                                 |

| 91         | SDA/EEPROM | I/O | Serial EEPROM data signal, and EEPROM Detect pin. If EEPROM<br>is used, a $10K\Omega$ pull-up resistor to Vcc should be connected to this<br>pin; otherwise it should be tied to GND. During a Reset operation the<br>NT1003-1 samples the voltage level on this pin, to determine if an<br>external EEPROM exists. This pin has an Open Drain output. This<br>output is temporarily forced to high-z while in the Suspend position. |

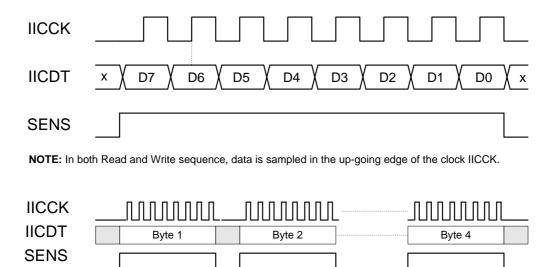

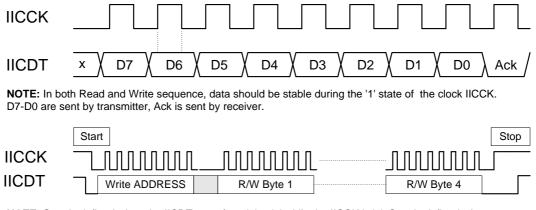

| 92         | SENS       | Ο   | Serial control Enable Signaling. This output is temporarily forced to<br>'0' while in the Suspend or Power-Down position.                                                                                                                                                                                                                                                                                                            |

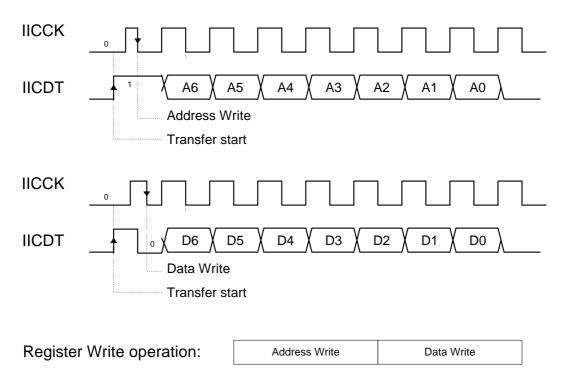

| 93         | IICDT      | I/O | Camera-Control Data I/O (supports some commonly used serial protocols). This pin has an Open Drain output, and should be connected to an external $3.3-10$ K $\Omega$ pull-up resistor to Vcc. This output is temporarily forced to high-z while in the Suspend or Power-Down position.                                                                                                                                              |

| 94         | IICCK      | 0   | Camera-Control Clock output (supports some commonly used serial protocols). This output is temporarily forced to 0v while in the Suspend or Power-Down position.                                                                                                                                                                                                                                                                     |

| 95         | PWR_DWN    | 0   | Camera Power-Down control. This is an Open Drain output. The NT1003-1 uses this output to switch On/Off the camera and/or external circuit. Upon Reset operation to the NT1003-1, this output is set to high-z (=Off). It is also set to high-z in the Suspend position, and remains high-z after Suspend position is over.                                                                                                          |

| 96         | RESIN      | Ι   | Power-On Reset input. This input is Schmitt-Trigger type, and it is active low.                                                                                                                                                                                                                                                                                                                                                      |

| 98         | USB_VP     | I/O | Universal-Serial-Bus Positive data line; This line should be connected<br>to an external pull-up resistor of $1.5K\Omega$ . Refer to Electrical<br>Characteristics table for pin spec. This pin is kept high-z while in the<br>Suspend position.                                                                                                                                                                                     |

| 99         | USB_VM     | I/O | Universal-Serial-Bus Negative data line. Refer to Electrical<br>Characteristics table for pin spec. This pin is kept high-z while in the<br>Suspend position.                                                                                                                                                                                                                                                                        |

#### NT1003-1

#### ABSOLUTE MAXIMUM RATINGS (Voltages Referenced to GND)

| Rating                                                 | Symbol                | Value                        | Unit |

|--------------------------------------------------------|-----------------------|------------------------------|------|

| DC Supply Voltage                                      | V <sub>CC</sub> - GND | -0.5 to 4.6                  | V    |

| Voltage, any pin to GND                                | V                     | -0.5 to $V_{\rm CC}^{}$ +0.5 | V    |

| DC Current Drain per Pin (Excluding $V_{CC}^{}$ , GND) | Ι                     | ±10                          | mA   |

| Operating Temperature Range                            | T <sub>A</sub>        | 0 to +70                     | °C   |

| Storage Temperature Range                              | T <sub>stg</sub>      | -65 to +150                  | °C   |

## **ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ =3.3V, $T_A$ = 0 to 70° C)

| Characteristic                                                     | Symbol              | Min                 | Тур  | Max                         | Unit |

|--------------------------------------------------------------------|---------------------|---------------------|------|-----------------------------|------|

| DC Supply Voltage (V <sub>CC</sub> to GND)                         | V <sub>CC</sub>     | 3.0                 | 3.3  | 3.6                         | V    |

| DC Supply Current (@ V <sub>CC</sub> =3.3V)                        | I <sub>CC</sub>     | -                   | -    | 73                          | mA   |

| Suspend mode Current (@ V <sub>CC</sub> =2.1V)                     | ISuspend            | -                   | -    | 2400                        | μΑ   |

| High Level Input Voltage (other than XIN, CAPTRN, and RESIN)       | V <sub>IH</sub>     | 2.0                 | -    | $V_{\rm CC}^{+0.3^{*}}$     | V    |

| Low Level Input Voltage (other than XIN, CAPTRN, and RESIN)        | V <sub>IL</sub>     | -0.3                | -    | 0.8                         | V    |

| High Level Input Voltage (XIN, CAPTRN, and RESIN)                  | V <sub>IH-s.t</sub> | 0.7 V <sub>CC</sub> | -    | V <sub>CC</sub> +0.3        | V    |

| Low Level Input Voltage (XIN, CAPTRN, and RESIN)                   | V <sub>IL-s.t</sub> | -0.5                | -    | 0.2V <sub>CC</sub> -<br>0.1 | V    |

| Input Current $V_{I} = V_{CC} + 0.3 \text{ or GND}$                | I <sub>in</sub>     | -10                 | +1   | +10                         | μΑ   |

| Input Capacitance                                                  | C <sub>in</sub>     | -                   | 2.5  | 7.0                         | pF   |

| 3-State Output Leakage Current $V_0 = V_{CC} + 0.3 \text{ or GND}$ | I <sub>OZ</sub>     | -10                 | +1   | +10                         | μA   |

| Output Capacitance                                                 | C <sub>out</sub>    | -                   | 2.0  | 7.0                         | pF   |

| High Level Output Voltage (@ Iout = -2mA)                          | V <sub>OH</sub>     | 2.4                 | -    | V <sub>CC</sub>             | V    |

| Low Level Output Voltage (@ Iout = 2mA)                            | V <sub>OL</sub>     | 0                   | -    | 0.4                         | V    |

| Crystal Frequency (at XIN and XOUT pins)                           | F <sub>XTL</sub>    | 47.9952             | 48.0 | 48.0048                     | MHz  |

\* Vcc+0.3 is for regular inputs. 5-volt Tolerant inputs allow maximum input voltage of VDD+0.3 volt.

#### **USB\_VP/VM pins ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ =3.3V, $T_A$ = 0 to 70° C)

| Characteristic                                                                                                                        | Symbol           | Min | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Hi-Z State Data Line Leakage (@ 0 <vin<3.3v)< td=""><td>I<sub>LO</sub></td><td>-10</td><td>-</td><td>+10</td><td>μΑ</td></vin<3.3v)<> | I <sub>LO</sub>  | -10 | -   | +10 | μΑ   |

| Differential Input Sensitivity                                                                                                        | V <sub>DI</sub>  | 0.2 | -   | -   | V    |

| Differential Common Mode Range                                                                                                        | V <sub>CM</sub>  | 0.8 | -   | 2.5 | V    |

| Single Ended Receiver Threshold                                                                                                       | V <sub>SE</sub>  | 0.8 | -   | 2.0 | V    |

| Static Output Low (@ $1.5K\Omega$ pull-up resistor to $3.6v$ )                                                                        | V <sub>OL</sub>  | -   | -   | 0.3 | V    |

| Static Output High (@ $15K\Omega$ pull-down resistor to GND)                                                                          | V <sub>OH</sub>  | 2.8 | -   | 3.6 | V    |

| Capacitance                                                                                                                           | C                | -   | -   | 20  | pF   |

| Rise Time (@ $C_L = 50 \text{ pF}$ )                                                                                                  | T <sub>R</sub>   | 4   | -   | 20  | nS   |

| Fall Time (@ $C_L = 50 \text{ pF}$ )                                                                                                  | T <sub>F</sub>   | 4   | -   | 20  | nS   |

| Driver Output Resistance                                                                                                              | Z <sub>DRV</sub> | 28  | -   | 43  | Ω    |

#### VIDEO PARAMETERS SPECIFICATION

| Parameter                                      | Symbol | Value                                      | Unit |

|------------------------------------------------|--------|--------------------------------------------|------|

| Digital Video Input Format <sup>(1)</sup>      | Y/U/V  | -                                          | -    |

| Down Scaling (V/H independent and arbitrary)   | -      | up to 16:1 vertical<br>and horizontal      | -    |

| Horizontal Anti Aliasing Filter <sup>(2)</sup> | -      | 2-5 taps                                   | -    |

| Vertical Anti Aliasing Filter <sup>(2)</sup>   | -      | 2-3 taps                                   | -    |

| Interpolation Phase Resolution                 | -      | 360°/4                                     | -    |

| Image Cropping (V/H independent and arbitrary) | -      | any window of<br>length 0 to full<br>image | -    |

| Video Compression Ratio                        | Cr     | 1-8                                        | -    |

| Video Compressor Clock Frequency               | -      | 48.000                                     | MHz  |

| Compressed Video Bit Rate                      | -      | 0.5 to 8 Mbit/sec                          | -    |

| Notes:                                         |        |                                            |      |

Refer to *Video Channel* chapter for specification of digital video input modes and waveforms.

Filter uses interpolation process.

#### USB INTERFACE PARAMETERS SPECIFICATION

| Parameter                                | Value | Unit     | USB Pipe<br>mode  |

|------------------------------------------|-------|----------|-------------------|

| USB Maximum Data Rate                    | 12    | Mbit/sec | -                 |

| Compressed Video Maximum Data Rate       | 8     | Mbit/sec | Isochronous       |

| I/O channel Rate Capacity <sup>(1)</sup> | 0-256 | Kbit/sec | Control &<br>Bulk |

| Notes:                                   |       |          |                   |

1. I/O channel uses transactions of up to 8-bytes per package.

## **<u>1. General Architecture</u>**

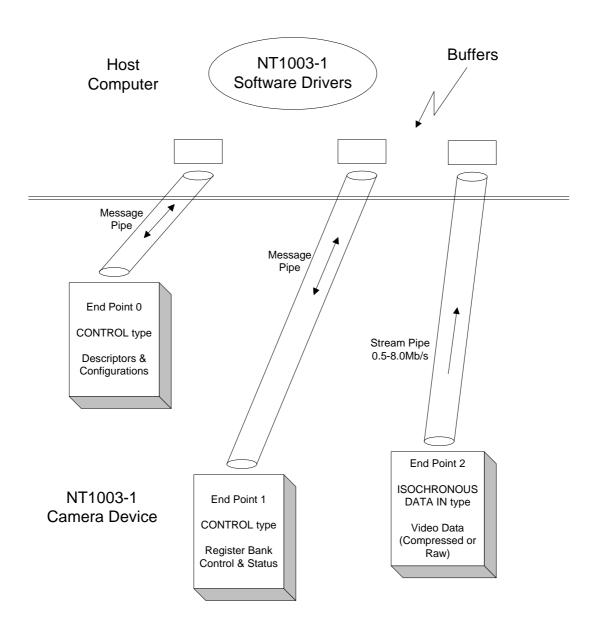

The following diagram describes the general architecture of the NT1003-1, regarding it as a standard USB device:

The NT1003-1 has 3 USB End-Points located on chip:

- \* End-Point #0: This is the Descriptors and Configuration End-Point, which is mandatory by the USB standard.

- \* End-Point #1: This is the NT1003-1 Register Bank; the host computer uses these registers to control the NT1003-1 and Camera.

- \* End-Point #2: This End-Point produces and sends the digital Video Data to the host computer. It uses 0.5 to 8.0Mb/s of the USB bandwidth, depending on how much bandwidth is available for the camera.

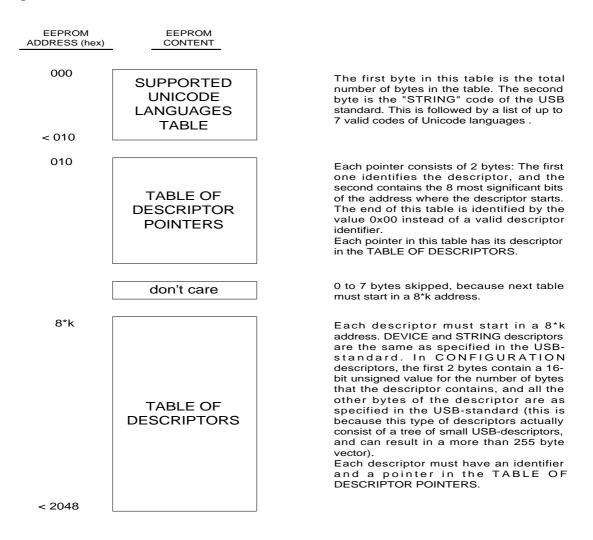

- \* The NT1003-1 has a default set of USB Descriptors on-chip, which are automatically used in absence of an external serial EEPROM (otherwise, all descriptors are read from the EEPROM). The default descriptors allow the host computer to select only one configuration to operate the camera, which is defined as Configuration #1.

If an external serial EEPROM is used, then new configurations can be defined, (which combine only the available End-Points). Also, String-Descriptors can be added (in multiple languages) to define the camera vendor's name, product name, serial-number, and others; the USB standard regards these features as optional.

The NT1003-1 supports USB Power-Management-Protocol. The Camera and external circuits can be power-controlled by their vendor-specific software drivers, via serial Data/Clock, and I/O ports; also, the PWR\_DWN output pin can be used to turn off the local power supply to these external circuits (refer to NT1003-1 application notes). The NT1003-1 uses a single 48MHz crystal to derive all its internal clock sources. Power Management also involves switching of internal clock sources which are not in use in certain modes of operation; this further reduces the power consumption of the device.

The NT1003-1 has two sources of Reset control: The Power-On Reset that comes from a dedicated input pin RESIN, and the USB-Reset command received from the host computer. Both reset sources are joined inside the NT1003-1 into a single reset signal, which initializes the NT1003-1 and all the other external camera circuits (via its Reset output pin RESON). It is assumed that a power-on-reset should be applied to the RESIN pin before any USB transaction is sent to the NT1003-1 by host; this is required so that the Serial-Interface-Engine inside the NT1003-1 will be able to receive any valid host command that will follow (including a USB-Reset command).

#### NT1003-1

The total USB bandwidth that is occupied by the NT1003-1 is mainly affected by the bandwidth of the Video Data Stream (End-Point #2). In order for a host computer, which initially has a small available bandwidth, not to reject the camera device, the NT1003-1 uses the Alternate-Interface mechanism to enable variable bandwidth. This allows the host computer to select the highest bit-rate that it can reserve for the Video Stream, starting from 8Mb/s down to 0.5Mb/s in descending 0.5Mhz steps (of course, this affects the video quality as well).

## 2. Registers Bank (Control and Status)

The NT1003-1 uses the End-Point #1 message pipe for NT1003-1 and camera control. As a bi-directional pipe, this channel allows the host computer to write contents to control registers, as well as to read status registers. Also, the control registers can be read by host computer to check their contents. All registers are byte-oriented.

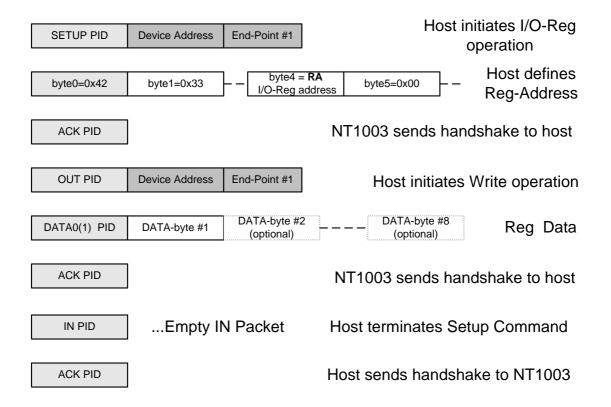

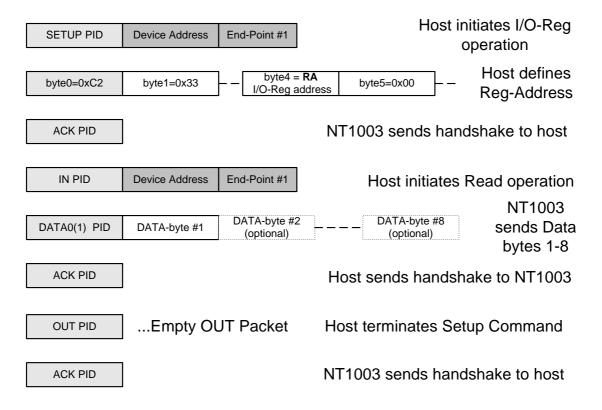

The following section defines a USB vendor-specific protocol for Read and Write operations applied to the NT1003-1 register bank. This protocol uses a standard USB Request of a vendor-specific type (defined in chapter 9.3 of USB standard rev.1.0) to perform a data transfer of up to 8 bytes long to/from End-Point #1. A single Write operation will write 1-8 concurrent bytes to the register bank, and a single Read operation will read 1-8 concurrent bytes from the register bank. The USB Request Command always defines the address of the first I/O-register to be read or write; this address is automatically incremented by the NT1003-1 for the following data bytes. The first byte of the USB Request Command defines the direction of the data transfer (0x42 for Write, and 0xC2 for Read); the second byte is a NT1003-1 specific code - 0x33. The address of the first I/O-register in list is defined in the **wIndex** parameter of the standard USB Request Command are not important to the NT1003-1.

## Write transaction protocol:

#### NT1003-1

The following table specifies the addresses where the NT1003-1 stores each of the bytes that appear in the data-section of the USB OUT transaction. These addresses relate to the contents of the **wIndex** parameter (bytes 4&5 of the SETUP command), which is denoted here by **RA**.

| DATA<br>byte # | Contents | Description                                           |

|----------------|----------|-------------------------------------------------------|

| 1              | Out Data | Will be stored in register at address RA.             |

| 2              | Out Data | Optional. Will be stored in register at address RA+1. |

| 3              | Out Data | Optional. Will be stored in register at address RA+2. |

| 4              | Out Data | Optional. Will be stored in register at address RA+3. |

| 5              | Out Data | Optional. Will be stored in register at address RA+4. |

| 6              | Out Data | Optional. Will be stored in register at address RA+5. |

| 7              | Out Data | Optional. Will be stored in register at address RA+6. |

| 8              | Out Data | Optional. Will be stored in register at address RA+7. |

#### **Read transaction protocol:**

#### NT1003-1

| DATA<br>byte # | Contents      | Description                                        |

|----------------|---------------|----------------------------------------------------|

| 1              | Register Data | Byte read from register at address RA.             |

| 2              | Register Data | Optional. Byte read from register at address RA+1. |

| 3              | Register Data | Optional. Byte read from register at address RA+2. |

| 4              | Register Data | Optional. Byte read from register at address RA+3. |

| 5              | Register Data | Optional. Byte read from register at address RA+4. |

| 6              | Register Data | Optional. Byte read from register at address RA+5. |

| 7              | Register Data | Optional. Byte read from register at address RA+6. |

| 8              | Register Data | Optional. Byte read from register at address RA+7. |

**Note:** Reading from an address that does not exist is legal, but will return unpredicted data.

The tables in the following pages specify all the Control and Status registers in the NT1003-1. A brief description is given for every specific bit in these registers, and the default values (after Reset operation) are defined. For more details about a specific register, one should consult the appropriate session in this data sheet.

#### NT1003-1

## General Control Registers (Power, Restart EP, USB, IO-pins, Camera Control):

| Reg.<br>Address | Reg. Name  | Function                                                  |            |  |

|-----------------|------------|-----------------------------------------------------------|------------|--|

| 0               | PWR_REG    | d0: reserved                                              | 00H        |  |

|                 | _          | d1: SSPND_EN: '1' Enables Suspend-Resume logic            |            |  |

|                 |            | d2: RES2: '0' Restarts End-Point #2 logic, '1' Releases   |            |  |

|                 |            | d3: reserved                                              |            |  |

|                 |            | d4: reserved                                              |            |  |

|                 |            | d5: PWR_VID: '1' Video-logic Power-On                     |            |  |

|                 |            | d6: reserved                                              |            |  |

|                 |            | d7: E2_EN: '1' Enables EEPROM R/W                         |            |  |

| 1               | CONFIG_REG | d7-d0: Configuration (set via USB). Read-Only reg.        | 00H        |  |

| 2               | ADRS_REG   | d6-d0: Device Address (set via USB). Read-Only reg.       | 00H        |  |

|                 |            | d7: '0'. reserved.                                        |            |  |

| 3               | ALTER_REG  | d3-d0: Video Bandwidth (set via USB). Read-Only reg.      | 00H        |  |

|                 |            | d7-d4: '0000'. reserved.                                  |            |  |

| 4               | FORCE_     | d3-d0: NEW_ALT Forced Video Bandwidth. R/W reg.           | 00H        |  |

|                 | ALTER_REG  | d7: FORCE_ALT ('1'=force, '0'=ignore)                     |            |  |

|                 |            | d6-d4: '000'. reserved.                                   |            |  |

| 5               | STATUS_REG | d0: VFRM_BLNK Vertic. Blank (if '1'). Read-Only reg.      | 00H        |  |

|                 |            | d7-d1: '0000000'. reserved.                               |            |  |

| 6               | IOPIN_REG  | d0: IO_1 Read/Write level of NT1003-1 pin IO-1            | 00H        |  |

|                 |            | d1: IO_2 Read/Write level of NT1003-1 pin IO-2            |            |  |

|                 |            | d7-d2: '000000'. reserved                                 |            |  |

| 7               | SER_MODE   | d7-d4: MODE (Soft, IICC, Cam1,Cam2,,,)                    | 00H        |  |

|                 |            | normally (when not in Soft mode):                         |            |  |

|                 |            | d0: CLK_RATE ('0' = 93.75KHz, '1' =1.5MHz)                |            |  |

|                 |            | d1: CLK_POL ('0' = Normal, '1' = Inverted)                |            |  |

|                 |            | d2: '0'. reserved.                                        |            |  |

|                 |            | d3: VSYNC ('1' = wait to new input video field)           |            |  |

|                 |            | Soft mode:                                                |            |  |

|                 |            | d0: CLK_OUT (functional in Soft mode only)                |            |  |

|                 |            | d1: DAT_IO (functional in Soft mode only)                 |            |  |

|                 |            | d2: SENS_OUT (functional in Soft mode only)               |            |  |

| 8               | SER_ADRS   | d7-d0: Address of serial device/camera-param.             | 00H        |  |

| 9               | SER_CONT   | d2-d0: SER_LEN Number of bytes to Wr/Rd                   | 00H        |  |

|                 |            | d3: SER_DIR ('0' = Wr, '1' = Rd)                          |            |  |

|                 |            | d4: SER_GO/SER_BUSY                                       |            |  |

|                 |            | d5: NACK_RCV (Read-Only. '1' means Not Ack.)              |            |  |

| 10              |            | d7-d6: '00'. reserved.                                    | 00H        |  |

| 10              | SER_DAT1   | d7-d0: 1 <sup>st</sup> serial byte to be sent/received    |            |  |

| 11              | SER_DAT2   | d7-d0: 2 <sup>nd</sup> serial byte to be sent/received    | 00H<br>00H |  |

| 12              | SER_DAT3   | d7-d0: 3 <sup>rd</sup> serial byte to be sent/received    |            |  |

| 13              | SER_DAT4   | d7-d0: 4 <sup>th</sup> serial byte to be sent/received 00 |            |  |

## **EEPROM Read/Write Registers:**

| Reg.<br>Address | Reg. Name | Function                                      | Default<br>Value |

|-----------------|-----------|-----------------------------------------------|------------------|

| 14              | EE_DATA   | d7-d0: EEPROM byte to be Written/Read         | 00H              |

| 15              | EE_LSBAD  | d7-d0: 8-LSbits of byte address in EEPROM     | 00H              |

| 16              | EE_CONT   | d2-d0: 3-MSbits of byte address in EEPROM     | 00H or           |

|                 |           | d3: EE_DIR ('0' = Write, '1' = Read)          | xxx0000          |

|                 |           | d4: EE_GO/EE_BUSY                             | (when no         |

|                 |           | d7-d5: EE_CLK_FORCE (This field is Read-Only) | EPROM)           |

#### NT1003-1

| Reg.<br>Address | Reg. Name | Function                                        | Default<br>Value |

|-----------------|-----------|-------------------------------------------------|------------------|

| 18              | DRM_CONT  | d0: REF ('0' = 8.2ms, '1' = 128ms refresh rate) | 00H              |

|                 |           | d1: '0'. reserved.                              |                  |

|                 |           | d2: RES_UR Restart video out buff. read logic   |                  |

|                 |           | d3: RES_FDL Restart video-frame-delay logic     |                  |

|                 |           | d4: RES_VDW Restart vid.out buff. write logic   |                  |

|                 |           | d7-d5: '000'. reserved.                         |                  |

| 19              | DRM_PRM1  | d0: Bit 8 of UR_1ST_ROW parameter               | 00H              |

|                 |           | d1: Bit 8 of UR_LST_ROW parameter               |                  |

|                 |           | d2: Bit 8 of FDL_1ST_ROW parameter              |                  |

|                 |           | d4-d3: Bits 17-16 of FDL_LST_WORD param.        |                  |

|                 |           | d5: Bit 8 of VDW_1ST_ROW parameter              |                  |

|                 |           | d6: Bit 8 of VDW_LST_ROW parameter              |                  |

|                 |           | d7: '0'. reserved.                              |                  |

| 20              | DRM_PRM2  | d7-d0: Bits 7-0 of UR_1ST_ROW parameter         | 00H              |

| 21              | DRM_PRM3  | d7-d0: Bits 7-0 of UR_LST_ROW parameter         | 00H              |

| 22              | DRM_PRM4  | d7-d0: Bits 7-0 of FDL_1ST_ROW parameter        | 00H              |

| 23              | DRM_PRM5  | d7-d0: Bits 7-0 of FDL_LST_WORD param.          | 00H              |

| 24              | DRM_PRM6  | d7-d0: Bits 15-8 of FDL_LST_WORD param.         | 00H              |

| 25              | DRM_PRM7  | d7-d0: Bits 7-0 of VDW_1ST_ROW parameter        | 00H              |

| 26              | DRM_PRM8  | d7-d0: Bits 7-0 of VDW_LST_ROW parameter        | 00H              |

#### DRAM and Memory Buffers Setup Registers:

# Video Setup and Control Registers:

| Reg.<br>Address | Reg. Name | Function                                                       | Default<br>Value |

|-----------------|-----------|----------------------------------------------------------------|------------------|

| 27              | VIN_REG1  | d2-d0: VIN_MODE Digital video input format                     | 00H              |

|                 |           | d3: VSNC_POL Vertical-Sync. pulse polarity                     |                  |

|                 |           | d4: HSNC_POL Horizontal-Sync. pulse polarity                   |                  |

|                 |           | d5: FID_POL Field Identity signal polarity                     |                  |

|                 |           | d6: HVALID_POL Pixel Envelope polarity                         |                  |

|                 |           | d7: VCLK_POL ('1'=data valid on up-going clock)                |                  |

| 28              | VIN_REG2  | d0: AUTO_FID Auto Field Identity generation. When set          | 00H              |

|                 |           | to '1', the NT1003-1 ignores the FID input from camera,        |                  |

|                 |           | and generates an internal toggling signal of its own           |                  |

|                 |           | instead.                                                       |                  |

|                 |           | d1: NONE_INTERLACE Interlace/Non-Interlace mode.               |                  |

|                 |           | If set to '1', all the input fields from camera are processed, |                  |

|                 |           | otherwise the odd fields are ignored.                          |                  |

|                 |           | d2: NO_HVALID If set to '1', HVALID input ignored.             |                  |

|                 |           | d3: UV_ID If set to '1', use V7 pin as UV-id ('1'=U).          |                  |

|                 |           | d4: FIX_2C If set to '1', U7 and V7 are inverted (2's comp).   |                  |

|                 |           | d5: SEND_FID If set to '1', Frame_Phase[0]=FID.                |                  |

|                 |           | d6: '0' reserved.                                              |                  |

|                 |           | d7: KEEP_BLANK Set to '1' to drop incoming frames.             |                  |

(Continued...)

NT1003-1

#### Video On USB

## Video Setup and Control Registers (Continued):

| Reg.<br>Address | 0           |                                                                                                                  | Default<br>Value |

|-----------------|-------------|------------------------------------------------------------------------------------------------------------------|------------------|

| 29              | LXSIZE_IN   | d7-d0: bits 7-0 of input video line length                                                                       | 00H              |

| 30              | MXSIZE_IN   | d1-d0: bits 9-8 of input video line length d7-d2: '000000' reserved.                                             | 00H              |

| 31              | LYSIZE_IN   | d7-d0: bits 7-0 of input video number of lines                                                                   | 00H              |

| 32              | MYSIZE_IN   | d1-d0: bits 9-8 of input video number of lines d7-d2: '000000' reserved.                                         | 00H              |

| 33              | LX_OFFST    | d7-d0: bits 7-0 of input video horizontal offset                                                                 | 00H              |

| 34              | MX_OFFST    | d1-d0: bits 9-8 of input video horizontal offset d7-d2: '000000' reserved.                                       | 00H              |

| 35              | LY_OFFST    | d7-d0: bits 7-0 of input video vertical offset                                                                   | 00H              |

| 36              | MY_OFFST    | d1-d0: bits 9-8 of input video vertical offset<br>d7-d2: '000000' reserved.                                      | 00H              |

| 37              | FRM_RATE    | d4-d0 Frame-Rate factor for video data output                                                                    | 00H              |

| 38              | LXSIZE_O    | d7-d0: bits 7-0 of output video line length                                                                      | 00H              |

| 39              | MXSIZE_O    | d1-d0: bits 9-8 of output video line length d7-d2: '000000' reserved.                                            | 00H              |

| 40              | LYSIZE_O    | d7-d0: bits 7-0 of output video number of lines                                                                  | 00H              |

| 41              | MYSIZE_O    | d1-d0: bits 9-8 of output video number of lines d7-d2: '000000' reserved.                                        | 00H              |

| 42              | FILT_CONT   | d2-d0: XFILT_CONT Horizontal-Filter select<br>d4-d3: YFILT_CONT Vertical-Filter select<br>d7-d5: '000' reserved. | 00H              |

| 43              | VO_MODE     | d5-d0 Digital Video-Out format (4:2:0, 4:1:1,,,)<br>d6: ('1' = Compressed Vid, '0' = Raw)<br>d7: '0' reserved.   | 00H              |

| 44              | INTRA_CYC   | d7-d0: Intra-Compression cycle (in frame units)                                                                  | 00H              |

| 45              | STRIP_SZ    | d3-d0: ACT_STRIP Actual Strip width (# of vid.lines)<br>d7-d4: VIRT_STRIP Virtual Strip width (# of vid.lines)   | 00H              |

| 46              | FORCE_INTRA | d0: $('1' = Force next frame Intra)$<br>d7-d1: '0000000' reserved.                                               |                  |

| 47              | FORCE_UP    | d0: ('1' = Force Up-mode Intra segments)<br>d7-d1: '0000000' reserved.                                           |                  |

| 48              | BUF_THR     | d7-d0: Threshold for buffer space Frame-Drop decision (given in units of 2KB).                                   |                  |

| 49              | DVI_YUV     | d2-d0: Code for YUV re-order processor.<br>d7-d3: '00000' reserved.                                              |                  |

(Continued...)

#### NT1003-1

## Compression Ratio Management Registers (Continued):

| Reg.<br>Address | Reg. Name        | Function                                                                                                                                | Default<br>Value |

|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 56              | PCM_THR1         | d7-d0: PCM Threshold 1 (unsigned 0-255)                                                                                                 | 00H              |

| 57              | PCM_THR2         | d7-d0: PCM Threshold 2 (unsigned 0-255)                                                                                                 | 00H              |

| 58              | DIST_THR_L       | d7-d0: bits 7-0 of DIST_THR (Distortion Threshold)                                                                                      | 00H              |

| 59              | DIST_THR_H       | d3-d0: bits 11-8 of DIST_THR (Distortion Threshold) d7-d4: '0000' reserved.                                                             | 00H              |

| 60              | MAX_DIST_L       | d7-d0: bits 7-0 of MAX_DIST (Maximum Distortion)                                                                                        | 00H              |

| 61              | MAX_DIST_H       | d0: bit 8 of MAX_DIST (Maximum Distortion)<br>d7-d1: '0000000' reserved.                                                                | 00H              |

| 62              | VID_BUF_<br>LEFT | d7-d0: Space left in NT1003-1 DRAM buffer for compressed video data (given in units of 2KB). <b>Read-Only Register.</b>                 | 00H              |

| 63              | LFP_LSB          | d7-d0: bits 10-3 of LAST_FRM_PNTR (DRAM pointer).<br>Read-Only Register.                                                                | 00H              |

| 64              | LFP_MSB          | d6-d0: bits 17-11 of LAST_FRM_PNTR (DRAM pointer)<br>d7: RAM_FULL ('1' if event occurred from last Read).<br><b>Read-Only Register.</b> | 00H              |

## 3. Power Management

In order to meet the USB standard, the NT1003-1 should be able to control USB power supply for the whole device. Two pins of the NT1003-1 were dedicated to this task: PWR\_DWN and SUSPND. Both pins are Open-Drain, and active when Hi-Z.

The USB standard requires that soon after a device is hot-connected to the computer, it should consume no more than 100mA from USB port; After configuration, the device may consume up to 500mA from the port. Also it is required that in the Suspend mode the device must not consume more than 0.5mA from the USB port.

The NT1003-1 uses its power management pins as follows:

- ⇒ The PWR\_DWN pin was designed to switch the USB 5v source to the video source circuit (CCD, DSP, ADC,  $\mu$ -Controller, Video-Decoder, etc.). The only ICs that continue to get normal power supply in the Power-Down state are the NT1003-1, DRAM, and EEPROM (all these are 3.3v operated).

- ⇒ The SUSPND pin was designed to shut-down the 3.3v power supply that makes the 5v to 3.3v conversion for the NT1003-1, DRAM, and EEPROM (this must be a common and dedicated power-supply. The other parts of the camera cannot use it). In its Shut-Down mode, the power supply should only keep the voltage above 2.0v (@ I < 0.5mA).

Refer to the NT1003-1 Application Notes for an example of how the PWR\_DWN and SUSPND pins should be used, and for the 3.3v supply in application design.

The NT1003-1 software driver can control part of the power-management process through the following registers of the NT1003-1:

| Parameter | Register<br>address  | Usage                                                                                                                                                                                                                                  |

|-----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSPND_EN  | Reg.0/d1<br>SSPND_EN | <ul> <li>Enable Suspend state:</li> <li>0: Default (after Reset). Suspend state is disabled</li> <li>1: NT1003-1 is enabled to respond to USB Suspend condition as required by USB standard.</li> </ul>                                |

| PWR_VID   | Reg.0/d5<br>PWR_VID  | <ul><li>Apply USB 5v to Video Source</li><li>0: Default (after Reset). Video Source is OFF</li><li>1: Video Source is powered ON</li></ul>                                                                                             |

| RES2      | Reg.0/d2<br>RES2     | <ul> <li>Restart End-Point #2 (Vid. pipe) in the NT1003-1:</li> <li>0: Default (after Reset). Restart NT1003-1 video path.</li> <li>1: Enable NT1003-1 Video Processor and Pipe circuit (after video source is powered on).</li> </ul> |

After USB-Reset, the NT1003-1 is in its Power Down state (PWR\_DWN pin is Hi-Z). After configuration, software sets PWR\_VID bit to '1' to turn on camera circuit (PWR\_DWN='0'). Software also sets SSPND\_EN bit to '1' to enable Suspend mode. Suspend occurs if USB Idle state detected for 3ms, and it also resets PWR\_VID bit.

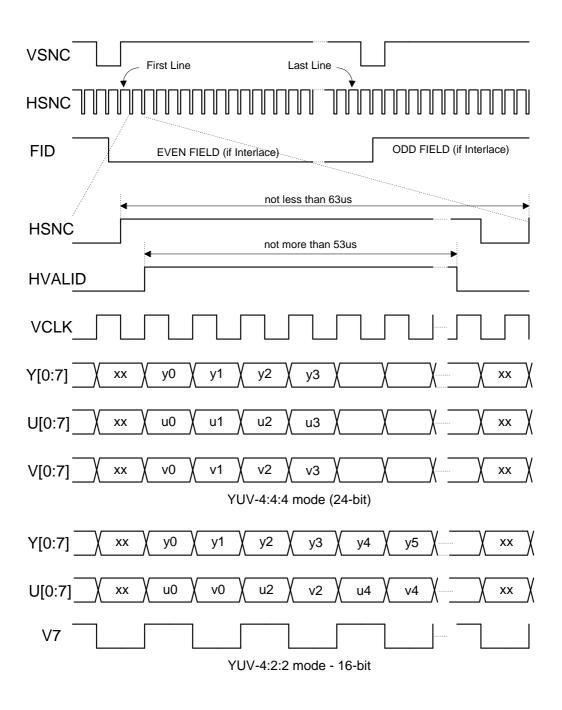

## 4. Video Input Interface

The NT1003-1 digital video input is YUV format. The NT1003-1 interface for this format is flexible and supports 4:4:4 (24-bit) as well as 4:2:2 timings (8-bit or 16-bit). Horizontal and Vertical controls can be physical pulses or coded signals; Also, Pixel Clock and pulse polarity of control signals can be programmed to be either positive or negative.

All the input buffers in the NT1003-1 that are supposed to be connected to the digital video source are 5-volt tolerant. This means that a camera that has 5-volt CMOS outputs will not cause any damage to the NT1003-1, even though the NT1003-1 operating voltage is 3.3 volts. In this case, the VDD pin (pin#16) should be connected to 5-volt power supply (rather than to 3.3v).

The NT1003-1 digital video input consists of the following signals:

#### Y0-Y7

In the 4:4:4 format (24-bit) and 4:2:2 16-bit modes, this is the Luminance input bus. In the 4:2:2 8-bit mode, this bus is used for mux YUV data. This bus is sampled by the VCLK input clock for the unsigned binary value (0-255) of the Y component (or U and V as well in the 8-bit mode).

#### U0-U7

This is the Color (U or U/V) input bus. In the 4:4:4 format (24-bit), This bus is sampled by the VCLK input clock for the unsigned binary value (0-255) of the U component. In the 4:2:2 16-bit format, this bus is sampled by the even cycles of VCLK input clock for the binary value (0-255) of the U component, and by the odd cycles of VCLK input clock for the binary value (0-255) of the V component.

#### V0-V7

This is the Color (V) input bus, which is used in the 4:4:4 format only. This bus is sampled by the VCLK input clock for the binary value (0-255) of the V component. In the 4:2:2 mode (16-bit or 8-bit) most of this bus is ignored by the NT1003-1 - only V7 is used as an optional U/V identifier.

#### VSNC

This is the Vertical Synchronization pulse, which indicates the start of a new video field (in Interlace mode) or the start of a new video frame (in Non-Interlace mode). Normally this pulse is negative.

#### HSNC

This is the Horizontal Synchronization pulse, which indicates the start of a new video line. Normally this pulse is negative.

#### FID

This signal is used in the Interlace mode, to indicates whether the current field is even or odd. In the Non-Interlace mode this input is ignored by the NT1003-1.

#### NT1003-1

## VCLK

This signal is the video pixel clock. It is used by the NT1003-1 to sample all the other inputs in the digital video interface.

## HVALID

This input is the pixel valid qualifier. When not active, the NT1003-1 refers to the samples that come from the Y, U, and V buses as Blank pixels (which are not considered a part of the digital image).

The timing of a camera signal that the NT1003-1 expects to receive in its digital video interface is normally as specified in the following timing diagram:

NT1003-1

####

YUV-4:2:2 mode 8-bit

#### Note:

In the YUV 8-bit mode the VCLK frequency is twice the pixel rate.

#### **Input Video Parameters**

The NT1003-1 was designed to interface to most available YUV formats. To make this possible, most of video parameters are programmable via specific registers from the NT1003-1 Register Bank.

The following tables specifies all the parameters that can be set by host computer to fit a specific video source (digital camera, video decoder, etc.):

| Parameter    | Register<br>address                                                        | Usage                                                                                                                                                                                                                                                                                                                  |  |

|--------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VIN_MODE[20] | Reg.27/d2-d0<br>VIN_REG1                                                   | Video input mode:<br>000: 8-bit 4:2:2 mode, using synchronization pulses<br>001: 8-bit 4:2:2 mode, using CCIR 656 sync. codes<br>010: 16-bit 4:2:2 mode, using synchronization pulses<br>011: 16-bit 4:2:2 mode, using CCIR 656 sync. codes<br>100: 24-bit 4:4:4 mode, using synchronization pulses<br>101-111: spare. |  |

| VSNC_POL     | Reg.27/d3Polarity of VSNC pulse:VIN_REG10: Negative pulse1: Positive pulse |                                                                                                                                                                                                                                                                                                                        |  |

| HSNC_POL     | Reg.27/d4<br>VIN_REG1                                                      | Polarity of HSNC pulse:<br>0: Negative pulse<br>1: Positive pulse                                                                                                                                                                                                                                                      |  |

| FID_POL      | Reg.27/d5<br>VIN_REG1                                                      | Polarity of FID (Field Identifier in Interlace mode) :<br>0: FID='0' during first (odd) field<br>1: FID='0' during second (even) field                                                                                                                                                                                 |  |

| HVALID_POL   | Reg.27/d6<br>VIN_REG1                                                      |                                                                                                                                                                                                                                                                                                                        |  |

| VCLK_POL     | Reg.27/d7<br>VIN_REG1                                                      | <ul><li>Polarity of VCLK (pixel clock):</li><li>0: Camera data valid at VCLK falling edge</li><li>1: Camera data valid at VCLK rising edge</li></ul>                                                                                                                                                                   |  |

#### NT1003-1

| 1   | · •   | 1    | \  |

|-----|-------|------|----|

| 100 | ntini | iea  | ۱. |

|     | ntinu | iuu. |    |

| (continued)   |              | <b>V</b>                                                |

|---------------|--------------|---------------------------------------------------------|

| Parameter     | Register     | Usage                                                   |

|               | address      |                                                         |

| AUTO_FID      | Reg.28/d0    | 0: Use external FID signal                              |

|               | VIN_REG2     | 1: Generate internal toggling FID. Ignore FID pin.      |

| NON_INTERLACE | Reg.28/d1    | 0: Interlace mode. Only even fields are transferred.    |

|               | VIN_REG2     | 1: Non-interlace mode. All frames are transferred.      |

| NO_HVALID     | Reg.28/d2    | 0: Normal operation                                     |

|               | VIN_REG2     | 1: Ignore the HVALID input                              |

| UV_ID         | Reg.28/d3    | 0: Normal operation                                     |

|               | VIN_REG2     | 1: Use V7 input as a U/V identifier ('1'=U, '0'=V)      |

| FIX_2C        | Reg.28/d4    | Fix 2's Compliment U/V values                           |

|               | VIN_REG2     | 0: Normal operation                                     |

|               | <b>D D D</b> | 1: Invert U[7] and V[7] to fix to Unsigned Binary       |

| XSIZE_IN[90]  | Regs.29-30   | Number of pixels in active line of video source         |

|               | LXSIZE_IN    |                                                         |

|               | MXSIZE_IN    |                                                         |

| YSIZE_IN[90]  | Regs.31-32   | Number of active lines in frame (/field) of video       |

|               | LYSIZE_IN    | source                                                  |

|               | MYSIZE_IN    |                                                         |

| X_OFFST[90]   | Regs.33-34   | Horizontal offset (number of pixels to be skipped after |

|               | LX_OFFST     | start of line).                                         |

|               | MX_OFFST     |                                                         |

| Y_OFFST[90]   | Regs.35-36   | Vertical offset (number of lines to be skipped after    |

|               | LY_OFFST     | start of frame).                                        |

|               | MY_OFFST     |                                                         |

| DVI_YUV[20]   | Reg.49/d2-d0 | Order of Ya/U/V/Yb components of a pixel-pair in 8-     |

|               | DVI_YUV      | bit modes:                                              |

|               |              | d0: '0': U comes after V                                |

|               |              | '1': U comes before V<br>d1: '0': Ya comes after U/V    |

|               |              | '1': Ya comes before U/V                                |

|               |              | d2: '0': Yb comes after U/V                             |

|               |              | '1': Yb comes before U/V                                |

#### **Frame-Rate Control**

Normally a camera or any other video source provides a fixed number of frames per second - for example, a NTSC based camera will always provide 30 frames/sec. The NT1003-1 allows the application software to modify the effective frame rate to fit its needs; in this way some of the frames coming from camera are dropped before processing, which eliminates the effort that could be wasted on those frames that would be dropped by the computer anyway.

The parameter that controls the effective frame-rate is called FRM\_RATE, and is specified in the following table:

#### NT1003-1

| Parameter    | Register<br>address      | Usage                                                                                                |

|--------------|--------------------------|------------------------------------------------------------------------------------------------------|

| FRM_RATE[40] | Reg.37/d4-d0<br>FRM_RATE | Frame Drop factor (n = 0-31). Effective frame rate is:<br>NTSC: $30^{(n+1)/32}$ PAL: $25^{(n+1)/32}$ |

The FRM\_RATE parameter ranges from 0 to 31. The value 31 indicates to the NT1003-1 to transfer to host computer full frame-rate that is delivered from the video source. Any value **n** that is less than 31 results in a frame-dropping from time to time, so that the effective frame rate is only  $(\mathbf{n}+1)/32$  of full frame-rate.

## **Video Scaling**

The NT1003-1 has two independent down scalers: one for frame width and one for frame height. It is the responsibility of the software application to select such scale factors that result in a reasonable aspect ratio.

In order to set the scaling factor, the host computer should just specify the desired size of the output frame; scaling is done automatically by the NT1003-1, regarding the input frame size versus the output frame size.

The following table specifies the parameters that are used to set the output frame size:

| Parameter   | Register   | Usage                                                 |

|-------------|------------|-------------------------------------------------------|

|             | address    |                                                       |

| XSIZE_O[90] | Regs.38-39 | Number of pixels in line of scaled output video frame |

|             | LXSIZE_O   |                                                       |

|             | MXSIZE_O   |                                                       |

| YSIZE_O[90] | Regs.40-41 | Number of lines in scaled output video frame          |

|             | LYSIZE_O   |                                                       |

|             | MYSIZE_O   |                                                       |

Note that if host computer specifies the same values for input frame size and output frame size, then no scaling occurs (scaling factor is 1:1).

The NT1003-1 performs no Up-Scaling<sup>(1)</sup>. This means that XSIZE\_O should never be greater than XSIZE\_IN, and YSIZE\_O should never be greater than YSIZE\_IN.

(1) To produce CIF size from 240-line video fields, a special interpolation process is applied by software driver.

### Video Filters

The NT1003-1 uses internal programmable anti aliasing filters for the scaling process. There are two filters that are used: One for the horizontal scaling, and the other for the vertical scaling. The filters are programmed independently of each other, and independently of the scaling factors.

Both horizontal and vertical filters use a combination of FIR structure and interpolation to eliminate the pixel jitter in the output frame. The interpolation process effectively improves x4 the resolution of the input frame both horizontally and vertically.

The following table specifies the register that is used to set the filter parameters:

| Parameter      | Register     | Usage                                       |

|----------------|--------------|---------------------------------------------|

|                | address      |                                             |

| XFILT_CONT[20] | Reg.42/d2-d0 | Select one of 5 possible Horizontal Filters |

|                | FILT_CONT    |                                             |

| YFILT_CONT[10] | Reg.42/d4-d3 | Select one of 3 possible Horizontal Filters |

|                | FILT_CONT    |                                             |

The following table specifies the Horizontal filters:

| XFILT_CONT[20] | FIR filter applied         | Interpolation  |  |

|----------------|----------------------------|----------------|--|

|                | (Horizontally)             | (Horizontally) |  |

| 000            | FIR = (1.0)                | NO             |  |

| 001            | FIR = (1.0)                | YES            |  |

| 010            | FIR = (1.0, 1.0)           | YES            |  |

| 011            | FIR = (1.0, 2.0, 1.0)      | YES            |  |

| 100            | FIR = (1.0, 1.0, 1.0, 1.0) | YES            |  |

The following table specifies the Vertical filters:

| YFILT_CONT[10] | FIR filter applied<br>(Vertically) | Interpolation<br>(Vertically) |

|----------------|------------------------------------|-------------------------------|

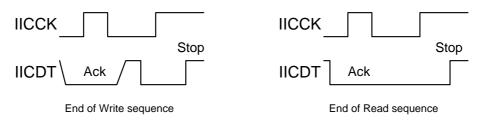

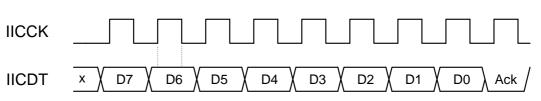

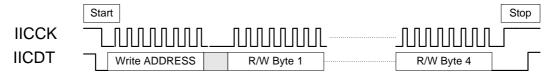

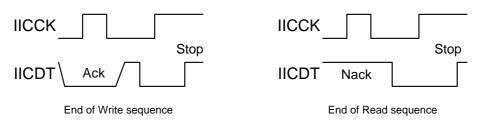

| 00             | FIR = (1.0)                        | NO                            |