# IBM Microelectronics IBM31T1602 Infrared Communications Controller Data Sheet and Application Notes

#### Note:

Before using this information and the product it supports, be sure to read the general information under "Notices" on page 7

Release 2.0 (February, 1998)

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law:

INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

Requests for technical information about IBM products should be made to your IBM Authorized Dealer or your IBM Marketing Representative.

### © Copyright International Business Machines Corporation 1998. All Rights Reserved.

Note to U.S. Government Users – Documentation related to restricted rights – Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

# TABLE OF CONTENTS

| 1 | IBM31'   | <b>F1602 Infrared Communications Controller</b>                                       | 8  |

|---|----------|---------------------------------------------------------------------------------------|----|

|   |          | ghlights                                                                              |    |

|   | 1.2. Ge  | neral Description                                                                     | 8  |

|   | 1.3. Ar  | chitecture Description                                                                | 8  |

|   | 1.4. Sys | stem Configuration                                                                    | 9  |

|   | 1.4.1.   | Plug and Play Configuration Register Access                                           | 9  |

|   | 1.4.2.   | Indirect Configuration Register Access                                                | 10 |

|   | 1.4.3.   | Direct Configuration Register Access                                                  | 10 |

|   | 1.5. UA  | RT Subsystem Configuration                                                            | 10 |

|   |          | R Subsystem Configuration                                                             |    |

|   | 1.6.1.   | FIR Transmit Operation                                                                | 11 |

|   | 1.6.2.   | FIR Receive Operation                                                                 | 12 |

|   | 1.7. Int | errupt Handling                                                                       | 14 |

|   | 1.8. Ex  | ternal Transceiver Interface                                                          | 14 |

|   | 1.9. Po  | wer Management Feature                                                                | 14 |

|   | 1.10.    | Pin Descriptions                                                                      | 15 |

|   |          | IBM31T1602 Pin Descriptions                                                           |    |

|   |          | Register Summary                                                                      |    |

|   | 1.11.1.  | Plug and Play Register Summary                                                        | 20 |

|   |          |                                                                                       |    |

|   | 1.11.3.  | Indirect Configuration Register Summary                                               | 21 |

|   | 1.11.4.  | Direct Configuration Register Summary                                                 |    |

|   | 1.11.5.  | UART Control Register Summary                                                         |    |

|   | 1.11.6.  | FIR Control Register Summary                                                          |    |

| 2 | IBM31'   | Г1602 Operational Modes                                                               |    |

|   |          | erview                                                                                |    |

|   |          | g and Play Configuration                                                              |    |

|   |          | lirect Configuration - Host DMA                                                       |    |

|   | 2.3.1.   | -                                                                                     |    |

|   | 2.3.2.   |                                                                                       |    |

|   | 2.4. Ind | lirect Configuration - Shared Memory                                                  | 28 |

|   | 2.4.1.   | Configuration Register Power-up Defaults - Indirect Configuration, Shared Memory Mode |    |

|   |          | 29                                                                                    |    |

|   |          | 1 IBM31T1602 Configuration                                                            |    |

|   |          | 2 IBM31T1602 Configuration                                                            |    |

|   |          | rect Configuration - Host DMA                                                         |    |

|   | 2.5.1.   | Direct Configuration Characteristics                                                  |    |

|   |          | st DMA Approach vs. Shared Memory Approach for Fast IR                                |    |

| 3 |          | cing Optical Transceivers to the IBM31T1602                                           |    |

|   |          | erview                                                                                |    |

|   |          | erfacing to Transceivers from IBM, Temic, Sharp, and Hewlett-Packard                  |    |

|   |          | erface to the IBM31T1101 Transceiver                                                  |    |

|   | 3.4. Int | erface to the IBM31T1100 and TFDS6000 Transceivers                                    |    |

|   | 3.4.1.   | Bandwidth Switching with the IBM31T1101, IBM31T1100 and TFDS6000 Transceivers.        | 35 |

|   | 3.4.2.   | Switching from SIR Mode to FIR Mode                                                   |    |

|   | 3.4.3.   | Switching from FIR Mode to SIR Mode                                                   |    |

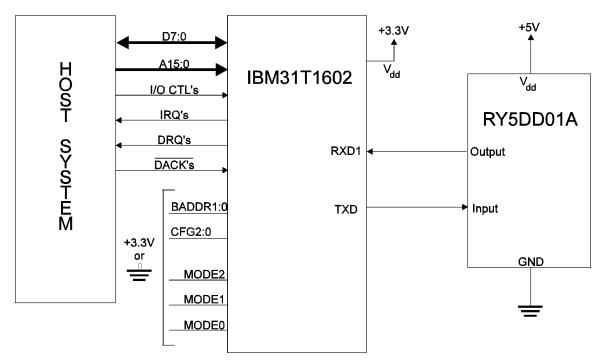

|   |          | erface to the RY5DD01A (Sharp)                                                        |    |

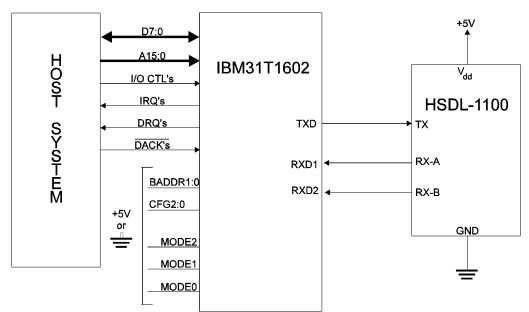

|   | 3.6. Int | erface to the HSDL-1100 (Hewlett-Packard)                                             | 38 |

|   | 3.6.1.   | Using the IBM31T1602 PDK with an HP Transceiver                                       |    |

|   |          | arp Carrier Detect                                                                    |    |

|   |          | S Auto Reset Function                                                                 |    |

|   | 3.9. Pro | grammed I/O Receive for the FIR Subsystem                                             | 39 |

| 4 | Register  | Description                                                                   | 40 |

|---|-----------|-------------------------------------------------------------------------------|----|

|   | 4.1. Plug | g and Play Mode                                                               |    |

|   | 4.1.1.    | Configuration Register Access                                                 | 40 |

|   | 4.1.2.    | Plug and Play Configuration                                                   |    |

|   | 4.1.3.    | Set Read Data Port Address Register (Configuration Location=0x00)             |    |

|   | 4.1.4.    | Serial Isolation Register (Configuration Location=0x01)                       | 42 |

|   | 4.1.5.    | Configuration Control Register (Configuration Location=0x02)                  |    |

|   | 4.1.6.    | Wake Command Register (Configuration Location=0x03)                           | 42 |

|   | 4.1.7.    | Resource Data Register (Configuration Location=0x04)                          |    |

|   | 4.1.8.    | Status Register (Configuration Location=0x05)                                 |    |

|   | 4.1.9.    | Card Select Number (CSN) Register (Configuration Location=0x06)               |    |

|   | 4.1.10.   | Logical Device Number (LDN) Register (Configuration Location=0x07)            |    |

|   | 4.1.11.   | Activate Register (Configuration Location=0x30)                               |    |

|   | 4.1.12.   | I/O Range Check Register (Configuration Location=0x31)                        |    |

|   | 4.1.13.   | Power Management Register (Configuration Location=0x38)                       | 44 |

|   | 4.1.14.   | Shared Memory Base Address Bits 23:16 Register (Configuration Location=0x40)  |    |

|   | 4.1.15.   | Shared Memory Base Address Bits 15:8 Register (Configuration Location=0x41)   |    |

|   | 4.1.16.   | Shared Memory Control Register (Configuration Location=0x42)                  |    |

|   | 4.1.17.   | Shared Memory Range/Limit Bits 23:16 Register (Configuration Location=0x43)   |    |

|   | 4.1.18.   | Shared Memory Range/Limit Bits 15:8 Register (Configuration Location=0x44)    |    |

|   | 4.1.19.   | UART Base Address Upper Byte Register (Configuration Location=0x60            |    |

|   | 4.1.20.   | UART Base Address Lower Byte Register (Configuration Location=0x61)           |    |

|   | 4.1.21.   | FIR Subsystem Base Address Upper Byte Register (Configuration Location=0x62)  |    |

|   | 4.1.22.   | FIR Subsystem Base Address Lower Byte Register (Configuration Location=0x63)  |    |

|   | 4.1.23.   | UART IRQ Select Configuration Register (Configuration Location=0x70)          |    |

|   | 4.1.24.   | UART IRQ Type Configuration Register (Configuration Location=0x71)            |    |

|   | 4.1.25.   | FIR Subsystem IRQ Select Configuration Register (Configuration Location=0x72) |    |

|   | 4.1.26.   | FIR Subsystem IRQ Type Configuration Register (Configuration Location=0x73)   |    |

|   | 4.1.27.   | First DMA Channel Configuration Register (Configuration Location=0x74)        |    |

|   | 4.1.28.   | Second DMA Channel Configuration Register (Configuration Location=0x75)       |    |

|   |           | rect Configuration Registers                                                  |    |

|   | 4.2.1.    | Power Down Register (PDR, Index=0x02)                                         |    |

|   | 4.2.2.    | Identification Register (IDR, Index=0x08)                                     |    |

|   | 4.2.3.    | DMA Line Select Register (DLS, Index=0xA2)                                    |    |

|   | 4.2.4.    | Shared Memory Base Address Register (SMBA, Index=0xA2)                        |    |

|   | 4.2.5.    | Infrared Control Register (IRC, Index=0xA3)                                   |    |

|   | 4.2.6.    | UART High Address Register (UARTH, Index=0xA4)                                |    |

|   | 4.2.7.    | UART Low Address Register (UARTL, Index=0xA5)                                 |    |

|   | 4.2.8.    | FIR High Address Register (FIRH, Index=0xA6)                                  | 53 |

|   | 4.2.9.    | FIR Low Address Register (FIRL, Index=0xA7)                                   |    |

|   |           | ect Configuration Registers                                                   | 53 |

|   | 4.3.1.    | Identification 0 Register (ID0, Index=0x0)                                    |    |

|   | 4.3.2.    | Identification Register 1 (ID1, Index=0x1)                                    |    |

|   | 4.3.3.    | Setup Register (SET, Index=0x2)                                               | 54 |

|   | 4.3.4.    | UART Low Index Register (UARTL, Index=0x3)                                    |    |

|   | 4.3.5.    | UART High Address Register (UARTH, Index=0x4)                                 |    |

|   | 4.3.6.    | FIR Low Address Register (FIRL, Index=0x5)                                    |    |

|   | 4.3.7.    | FIR High Address Register (FIRH, Index=0x6)                                   |    |

|   | 4.3.8.    | Local DMA Control Register (LDMAC, Index=0x7)                                 |    |

|   | 4.3.9.    | Shared Memory Base Address Register (SMBA, Index=0x7)                         |    |

|   |           | RT Control Registers                                                          |    |

|   | 4.4.1.    | Receive Buffer Register (RBR, Index=0x0, DLAB=0)                              |    |

|   | 4.4.2.    | Transmit Holding Register (THR, Index=0x0, DLAB=0)                            |    |

|   | 4.4.3.    | Interrupt Enable Register (IER, Index=0x1)                                    |    |

|   | 4.4.4.    | Interrupt Identification Register (IIR, Index=0x2)                            |    |

|   | 4.4.5.    | FIFO Control Register (FCR, Index=0x2)                                        | 57 |

| 4.4.6.   | Line Control Register (LCR, Index=0x3)                      |    |

|----------|-------------------------------------------------------------|----|

| 4.4.7.   | Modem Control Register (MCR, Index=0x4)                     | 59 |

| 4.4.8.   | Line Status Register (LSR, Index=0x5)                       |    |

| 4.4.9.   | Modem Status Register (MSR, Index=0x6)                      | 61 |

| 4.4.10.  | Scratchpad Register (SCR, Index=0x7)                        |    |

| 4.4.11.  | Divisor Latch LSB Register (DLL, Index=0x0, DLAB=1)         |    |

| 4.4.12.  | Divisor Latch MSB Register (DLM, Index=0x1, DLAB=1)         |    |

| 4.5. FIR | Control Registers                                           |    |

| 4.5.1.   | Master Control Register (All Banks, Index=0x0)              | 63 |

| 4.5.2.   | Master Status Register (Bank=0, Index=0x1)                  |    |

| 4.5.3.   | Miscellaneous Control Register (Bank=0, Index=0x1)          |    |

| 4.5.4.   | RxFIFO Register (Bank=0, Index=0x2)                         |    |

| 4.5.5.   | TxFIFO Register (Bank=0, Index=0x2)                         |    |

| 4.5.6.   | TxControl 1 Register (Bank=0, Index=0x3)                    |    |

| 4.5.7.   | TxControl 2 Register (Bank=0, Index=0x4)                    |    |

| 4.5.8.   | TxStatus Register (Bank=0, Index=0x5)                       | 69 |

| 4.5.9.   | RxControl Register (Bank=0, Index=0x6)                      |    |

| 4.5.10.  | RxStatus Register (Bank=0, Index=0x7)                       |    |

| 4.5.11.  | Reset Command Register (Bank=0, Index=0x7)                  |    |

| 4.5.12.  | Frame Address Register (Bank=1, Index=0x1)                  |    |

| 4.5.13.  | Rx Byte Count Low Register (Bank=1, Index=0x2)              |    |

| 4.5.14.  | Rx Byte Count High Register (Bank=1, Index=0x3)             |    |

| 4.5.15.  | Rx Ring Frame Pointer Low Register (Bank=1, Index=0x4)      |    |

| 4.5.16.  | Rx Ring Frame Pointer High Register (Bank=1, Index=0x5)     | 73 |

| 4.5.17.  | Tx Byte Count Low Register (Bank=1, Index=0x6)              | 73 |

| 4.5.18.  | Tx Byte Count High Register (Bank=1, Index=0x7)             |    |

| 4.5.19.  | Infrared Configuration 1 Register (Bank=2, Index=0x1)       |    |

| 4.5.20.  | Infrared Transceiver Control Register 1 (Bank=2, Index=0x2) | 75 |

| 4.5.21.  | Infrared Transceiver Control Register 2 (Bank=2, Index=0x3) | 76 |

| 4.5.22.  | General Purpose Timer Register (Bank=2, Index=0x4)          |    |

| 4.5.23.  | Infrared Configuration 3 Register (Bank=2, Index=0x5)       |    |

| 4.5.24.  | Modem Tuning Register (Bank=2, Index=6)                     |    |

| 4.5.24   | 1 0                                                         |    |

| 4.5.24   | .2 Basic Pulse Shaping Operation                            |    |

| 4.5.24   | 1 1                                                         |    |

| 4.5.24   |                                                             |    |

| 4.5.24   |                                                             |    |

| 4.5.25.  | Shared Memory Page Register (Bank=3, Index=0x1)             |    |

| 4.5.26.  | TxDMA Start Address Low Register (Bank=3, Index=0x2)        |    |

| 4.5.27.  | TxDMA Start Address High Register (Bank=3, Index=0x3)       |    |

| 4.5.28.  | Revision ID Register (Bank=3, Index=0x7)                    |    |

|          | al Specifications                                           |    |

|          | ommended Operating Conditions                               |    |

|          | ver Requirements                                            |    |

|          | Specifications                                              |    |

| 5.3.1.   | Driver DC Voltage Specifications (in Volts)                 |    |

| 5.3.2.   | Driver DC Currents at Rated Voltages                        |    |

| 5.3.3.   | Receiver DC Voltage Specifications (in Volts)               |    |

| 5.3.4.   | Receiver DC Current Specifications                          |    |

| 6 Timing | Diagrams                                                    | 88 |

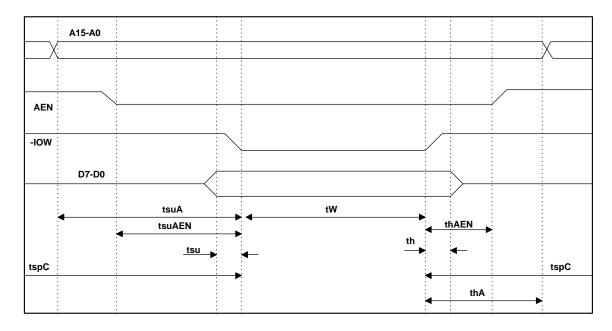

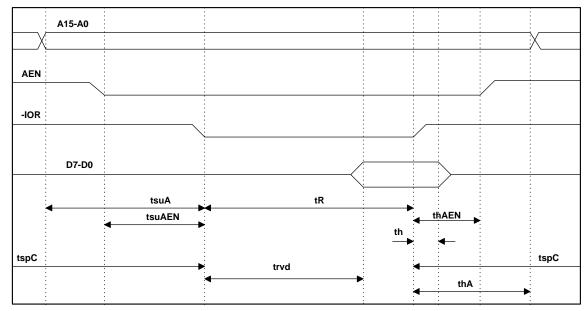

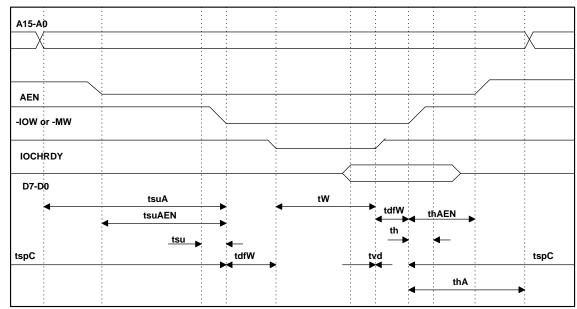

|          | 131T1602 in Host DMA Mode, ISA I/O Write Cycle              |    |

|          | 131T1602 in Host DMA Mode, ISA I/O Read Cycle               |    |

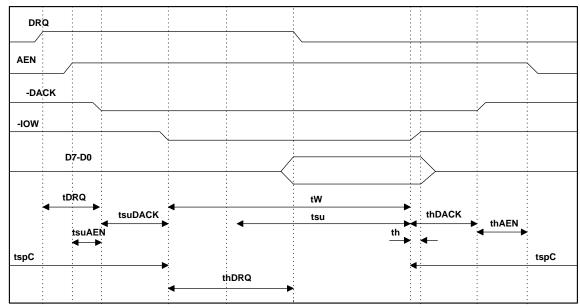

|          | 131T1602 in Host DMA Mode, ISA DMA Read Cycle (I/O Write)   |    |

| 6.3.1.   | ISA DMA Read (I/O Write) Timing Specification               |    |

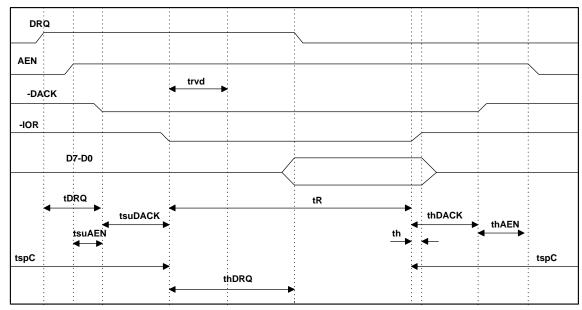

|          | 131T1602 in Host DMA Mode, ISA DMA Write Cycle (I/O Read)   |    |

| 6.4.1.   | ISA DMA Write (I/O Read) Timing Specification               |    |

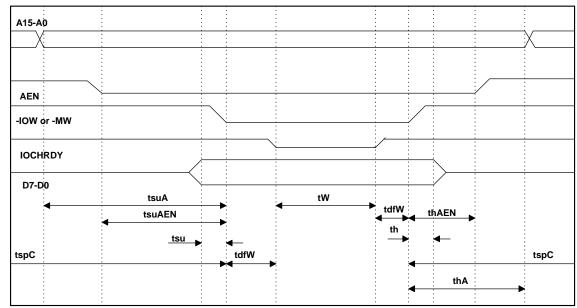

| 6.5. IBM31T1602 in Shared Memory Mode, ISA I/O or Memory Write Cycle with Wait State |     |

|--------------------------------------------------------------------------------------|-----|

| 6.6. IBM31T1602 in Shared Memory Mode, ISA I/O or Memory Read Cycle with Wait State  | 93  |

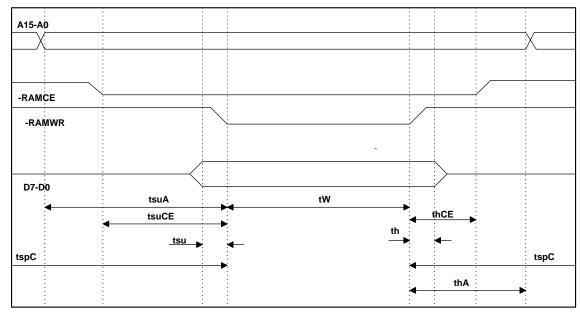

| 6.7. IBM31T1602 in Shared Memory Mode, Local Memory Write Cycle                      | 94  |

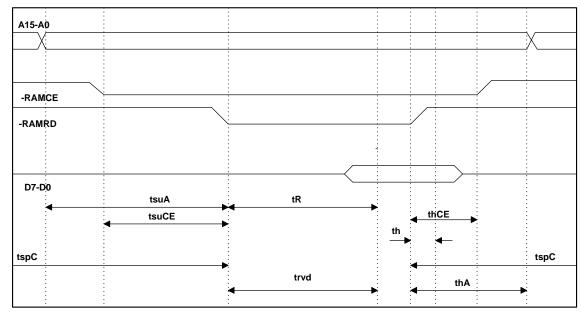

| 6.8. IBM31T1602 in Shared Memory Mode, Local Memory Read Cycle                       | 95  |

| Appendix A : Application Notes                                                       | 96  |

| A.1 : Metastability in FIR subsystem                                                 | 96  |

| A.2 : Premature reset of EOM with Auto Reset RTS on                                  | 96  |

| A.3 : Interrupt Status Bits Stability                                                |     |

| A.4 : Sharp Carrier Detection when in IrDA-FIR mode                                  | 97  |

| A.5 : Sharp Carrier Detection when in IrDA-SIR mode                                  |     |

| A.6 : Hard vs. Soft Powerdown for Plug and Play Shared Memory Mode                   | 97  |

| A.7 : RTS bit is write-only                                                          |     |

| Appendix B : IR Modulation Schemes                                                   | 99  |

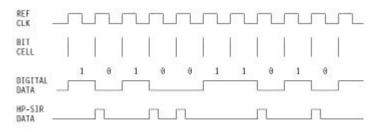

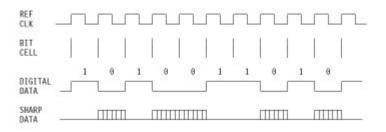

| HP-SIR Modulation                                                                    | 99  |

| B.2 : Sharp Modulation                                                               | 99  |

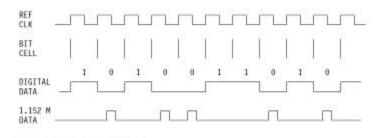

| B.3: 1.152 Mbits/s Modulation                                                        | 99  |

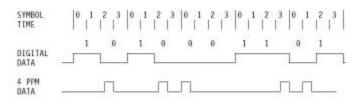

| B.4 : 4 Mbits/s 4PPM Modulation                                                      |     |

| B.4.1: 4 Mbits/s 4 PPM Format                                                        | 100 |

| B.4.2 : 4 PPM Baud Rate                                                              | 101 |

| Appendix C : Indirect Configuration Register Default Settings                        |     |

| Appendix D : UART Information                                                        | 104 |

| D.1 : UART Reset Control                                                             |     |

| D.2 : UART Interrupt Priority Settings Of the Interrupt Identification Register      | 104 |

| D.3 : Programmable Baud Rate Generator                                               | 105 |

| Appendix E : Bandwidth Switching with the IBM31T1101, IBM31T1100 and TFDS6000        |     |

| Transceivers                                                                         |     |

| E.1 : Switching from SIR Mode to FIR Mode                                            |     |

| E.2 : Switching from FIR Mode to SIR Mode                                            |     |

| Appendix F : Internal Resource Data Structure                                        |     |

| F.1 : Internal Resource Data Structure - Host DMA                                    |     |

| F.2 : Internal Resource Data Structure - Local DMA                                   |     |

| 7 Appendix G : Pinout Cross Reference                                                |     |

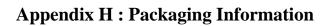

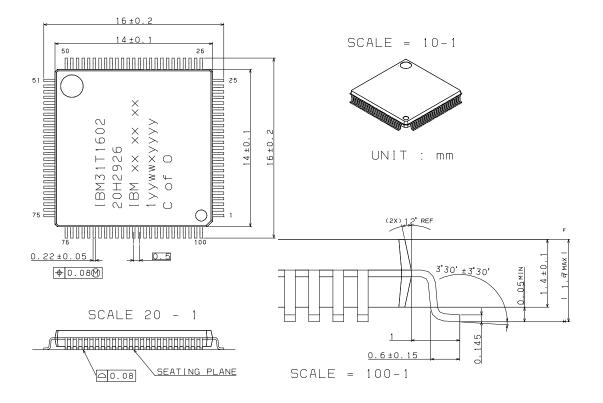

| Appendix H : Packaging Information                                                   |     |

| H.1 : IBM31T1602 Footprint                                                           |     |

| Appendix I : Ordering Information                                                    | 117 |

# NOTICES

References in this publication to IBM products, programs or services do not imply that IBM tends to make these available in all countries in which IBM operates. Any reference to an IBM licensed program in this publication is not intended to state or imply that only IBM's licensed program may be used. Any functionally equivalent product, program or service that does not infringe any of IBM's intellectual property rights may be used instead of the IBM product, program or service. Evaluation and verification of operation in conjunction with other products, except those expressly designated by IBM, are the user's responsibility.

IBM may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries in writing, to the IBM Director of Commercial Relations, IBM Corporation, Purchase, NY 10577.

The information provided is believed to be accurate and reliable. IBM reserves the right to make changes to the product described without notice. No liability is assumed as a result of its use nor for any infringement of the rights of others.

This document may contain preliminary information and is subject to change by IBM without notice. IBM assumes no responsibility of liability for any use of the information contained herein. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. Products described in this document are not intended for use in implementation or other direct life support applications where malfunction may result in direct physical harm or injury to persons.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6531

Fast Fax Service: 415-855-4121

## **Trademarks and Service Marks**

The following terms, denoted by an asterisk (\*), used in this publication, are trademarks or service marks of IBM Corporation in the United States or other countries:

IBM

**IBM Microelectronics**

The following terms, denoted by an asterisk (\*), used in this publication, are trademarks of other companies, as follows:

| IrDA      | Infrared Data Association     |

|-----------|-------------------------------|

| TFDS6000  | Temic Semiconductors          |

| RY5DD01A  | Sharp Electronics Corporation |

| HSDL-1100 | Hewlett Packard Company       |

# 1 IBM31T1602 Infrared Communications Controller

# 1.1. Highlights

IrDA 1.1\*\*, HP-SIR and Sharp ASK compatible Supports IrDA data rates up to 4 Mbits/s 16450 and 16550 standard UART compatibility Interfaces with the IBM31T1100 and IBM31T1101 infrared transceiver modules, and easily connects to other IrDA transceivers General purpose bidirectional I/O pins for external transceiver control ISA bus interface Full ISA Plug and Play support On-chip or external Plug and Play resource data structure Plug and Play, Indirect and Direct configuration Two programmable Rx lines Host DMA and Shared Memory modes Supports single or dual DMA channel operation Back-to-back packet transmission and reception Advanced interrupt configuration Low power consumption Power-down modes 48 MHz external clock input 3.3V supply voltage Small 100-pin Low Quad Flat Pack (LQFP) package

# **1.2.** General Description

The IBM31T1602 is a low-cost, low-power highly integrated Infrared Communications Controller capable of supporting both low-speed and high-speed infrared modulation schemes. The low-speed communication mode supports data rates up to 115.2 kbits/s. The high-speed mode supports both 1.152 Mbits/s and 4 Mbits/s data rates. Implemented in IBM Microelectronic's 0.8 micron CMOS technology, the IBM31T1602 offers high performance, and many on-chip functions to meet today's and tomorrow's requirements for infrared communications applications.

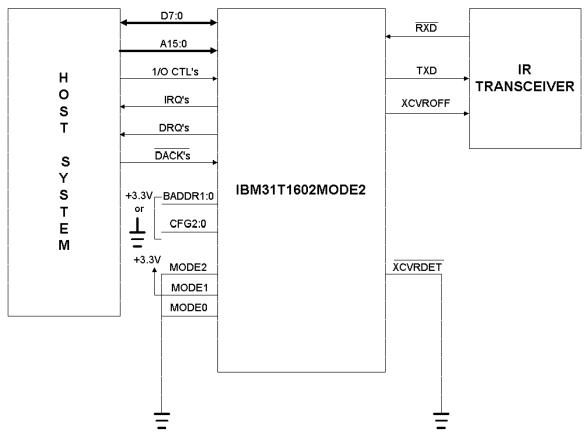

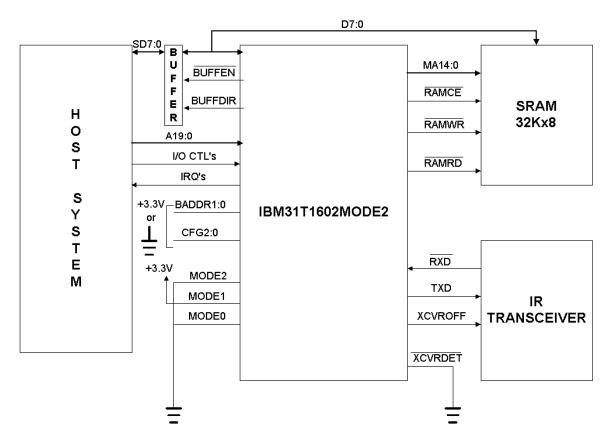

The IBM31T1602's internal architecture is designed to easily interface to an ISA system, as well as provide multiple configuration modes to satisfy a wide variety of programming needs.

Typical applications for the IBM31T1602 include: data communications, serial data transfer between notebook computers, desktops and printers, and digital camera technology.

# **1.3.** Architecture Description

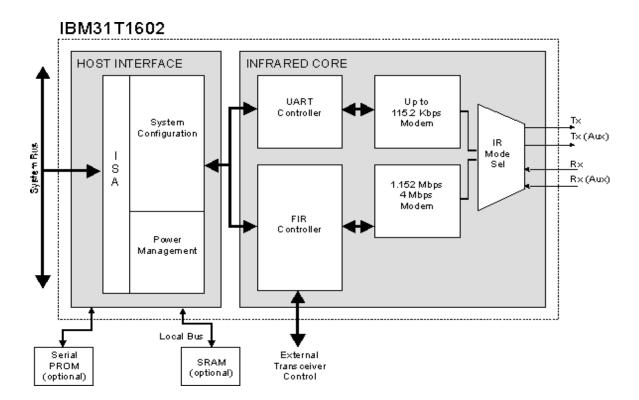

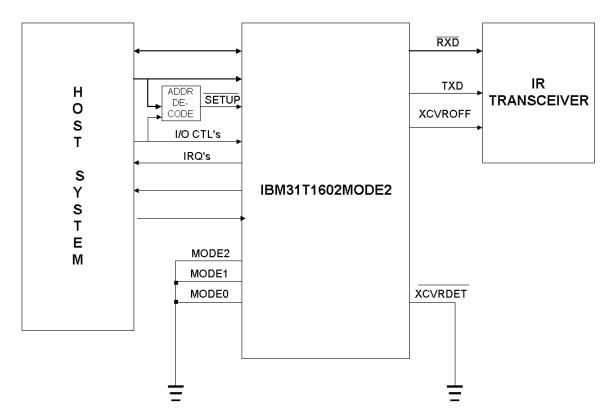

The IBM31T1602 Infrared Communications Controller consists of an Infrared Core module and a Host Interface module (see Figure 1-1 on page 1-2). The Infrared Core module controls all infrared communications functions and is divided into two subsystems: UART and Fast Infrared (FIR). Each subsystem consists of a controller and a modem.

The UART is fully compatible with the industry standard 16550 UART. The UART subsystem modem is capable of HP-SIR and Sharp ASK modulation. The FIR subsystem consists of a serial-to-parallel, parallel-to-serial converter and supports both 1.152 Mbits/s and 4 Mbits/s IrDA speeds.

The Host Interface module connects to an ISA bus. It contains the bus interface logic, system configuration registers, power management circuitry, and local DMA control functions. The IBM31T1602 supports two modes of block data transfers: Host DMA and Shared Memory Buffer. In Host DMA mode, data is transferred using the host system's DMA controller. In Shared Memory mode, data is first buffered in local RAM, then read by the host for receive or shifted out to the infrared link in transmit.

Figure 1-1. IBM31T1602 Functional Block Diagram

# **1.4.** System Configuration

The IBM31T1602 can be configured using one of three methods: plug and play, indirect, or direct configuration. The configuration method is determined by three mode pins: MODE2, MODE1, and MODE0. (See 1.10, "Pin Configuration" on page 1-7)

## 1.4.1. Plug and Play Configuration Register Access

Plug and Play (PnP) configuration has been implemented in the IBM31T1602 according to the Plug and Play ISA Specification Version 1.0a.

Configuration activity is achieved through three I/O ports: PnP Configuration Address Port, at I/O address 0279h, write-only PnP Configuration Write Data Port, at I/O address 0A79h, write-only PnP Configuration Read Data Port, at a variable address

Note that the Configuration Address Port and Configuration Write Data Port are located at fixed I/O addresses. The Configuration Read Data Port is assigned an address by configuration software, anywhere in the range 0203h to 03FFh as long as the address has 11b (binary) in the bits A1:0. Therefore, valid addresses are 0203h, 0207h, 020Bh, 020F, 0213h, 0217h, 021Bh, 021Fh, etc. The configuration program must ensure that the address does not conflict with a register on a non-PnP ISA device.

To access a PnP configuration register, the address of the target configuration register must first be written to the Configuration Address Port (at location 0279h). Note that a read from location 0279h actually reads the LPT1 printer status port. This is why the PnP Configuration Address Port, also at location 0279h, is a write-only register. To write data into the target configuration register, write the data into the Configuration Write Data Port at location 0A79h. To read data from the target configuration register, read the Configuration Read Data Port.

#### 1.4.2. Indirect Configuration Register Access

Two 8-bit I/O ports are used to access the configuration registers: the index port and data port.

The index port is used to address a specified configuration register. The data port is used to read or write to and from the configuration register that is being pointed to by the index port. The destination and source of the data is determined by the last setting of the index port.

To write to a configuration register, the programmer writes the index value of the configuration register to the index port (see Table 5 for index assignments). Next, the programmer loads the 8-bit data value destined for the configuration register in two consecutive write accesses to the data port. To read from a configuration register, the programmer writes the index value of the configuration register to the index port, then reads from the data port.

**Note:** Only two consecutive write operations to the data port can modify an indirect configuration register. This protection mechanism prevents accidental erasure of any previously set configuration data. A single read from the index and data port may be done at any time.

The table below shows four possible address locations of the index and data ports. The addresses are set by the BADDR0 and BADDR1 pins.

| Table 1-1 Index and Data Port Locations |        |       |       |  |  |  |  |

|-----------------------------------------|--------|-------|-------|--|--|--|--|

| BADDR1                                  | BADDR0 | Index | Data  |  |  |  |  |

| 0                                       | 0      | 0x398 | 0x399 |  |  |  |  |

| 0                                       | 1      | 0x26E | 0x26F |  |  |  |  |

| 1                                       | 0      | 0x15C | 0x15D |  |  |  |  |

| 1                                       | 1      | 0x02E | 0x02F |  |  |  |  |

#### **Index and Data Port Locations**

The programmer must determine the index port location after power-on-reset. This is done by reading all four index port addresses twice. After a hardware reset, the correct location is determined by an 0x88 value being returned on the first read, and a 0xDF value being returned on the second read. This signifies that the index port has been located successfully.

The IBM31T1602 can be set to a default configuration on power-up. This is accomplished by setting the CFG2-CFG0 pins. This feature is not available if Plug and Play or Direct Configuration mode is selected. Appendix C, "Indirect Configuration Register Default Settings" on page C-1 describes the different default configurations.

#### 1.4.3. Direct Configuration Register Access

This type of register access is similar to the one used in PS/2 Micro Channel\* systems where configuration (POS) registers are accessed by driving the SETUP line low during I/O cycles, and address lines (A2-A0) select one of eight direct configuration registers.

Note: Direct configuration register bits map directly into corresponding indirect configuration register bits.

## 1.5. UART Subsystem Configuration

The UART subsystem is a fully compatible version of the NS16550 UART. It has full EIA interface capability, however the EIA interface lines do not go out to the module pins, therefore this UART cannot be used as a fully functional COM port. It is mainly used for the low-speed infrared functions. Addressing

to the UART is programmable. The UART address registers must be properly set up during system configuration.

The low-speed infrared modulation in the IBM31T1602 is fully IrDA 1.0 compatible. The UART is used to serialize the packet data to the infrared link one character at a time. Each character has eight data bits, one start bit and one stop bit. Start character, stop character, transparency character insertion or removal and CRC generation or checking as specified in IrDA 1.0 are all done by software.

Two modulation schemes, HP-SIR or Sharp-ASK are supported. In receive, the HP-SIR pulse width can be 1.6  $\mu$ s or 3/16ths of a single bit time. In transmit, the pulse width is fixed at 1.6  $\mu$ s regardless of the data rate to conserve power.

# 1.6. FIR Subsystem Configuration

The FIR subsystem is fully IrDA 1.1 compatible. It supports the serial infrared link at 576 kbits/s, 1.152 Mbits/s and 4 Mbits/s. The lower speeds are a Synchronous Data Link Control (SDLC) protocol, packet based with start/stop flags delimiting a data packet encoded by 'zero-insertion'. The 4 Mbits/s bit protocol uses an optical preamble and postamble to

delimit the 4 Pulse Position Modulated (4 PPM) packet data.

The FIR High/Low Address Registers must be set up during the system configuration. The Enable Infrared bit must also be set to 1 to grant access to all the FIR internal registers. The FIR Address Registers default to a preset address according to CFG pins settings.

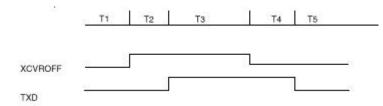

#### 1.6.1. FIR Transmit Operation

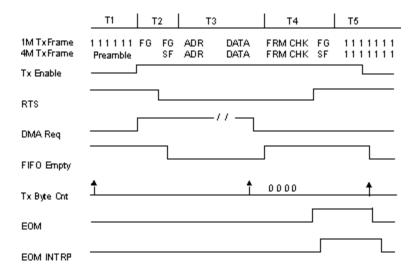

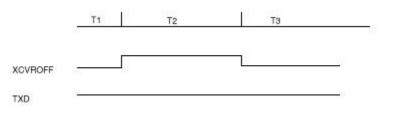

The FIR transmit operation is illustrated below:

#### T1 Set-up phase:

Set up Transmit Control Registers per desired options. Load the byte count to the Transmit Byte Count Register. Set up the host DMA controller and the Tx packet. Set RTS and Transmit Enable bits.

#### T2 Start-up phase:

RTS is active. If no carrier is detected, the transmitter starts transmitting. DMA Req is activated if DMA is enabled. The Tx FIFO is filled with transmit data. If DMA is not enabled, the Write Tx FIFO register can be used. If the Num Start Flag/Preamble bit is 0, the transmitter starts sending flags (1M) or preambles (4M) until the Tx FIFO is half filled (8 bytes). If the Num Start Flag/Preamble bit is 1, the transmitter waits until the Tx FIFO is half filled, then sends two start flags (1M mode) or preambles and one start flag (4M mode).

## T3 Send data phase:

The transmitter starts sending data stored in the FIFO. DMA Req to the host is active when the FIFO is not full.

#### **T4** End of transmission:

The Byte Counter counts down to 0. DMA Req stops. The transmitter sends out the remaining data in the FIFO. CRC generator inverts the CRC and sends it out. Closing flag is sent. EOM latch is set. Interrupt is activated.

#### T5 Idle phase:

The transmitter continues sending 1s or flags (1M) or preambles (4M), depending on the Idle line setting option. The host reads the TxStatus Register to check for transmission completion status.

Reset EOM, Transmit Enable and RTS bits. End of transmission.

### **1.6.2.** FIR Receive Operation

The FIR receive operation is illustrated below:

|                          | T1                        | т  | 2        | Т3         | T4           |                    | T5 | Т6                                    |

|--------------------------|---------------------------|----|----------|------------|--------------|--------------------|----|---------------------------------------|

| 1M TxFrame<br>4M TxFrame | 1 1 1 1 1 1 1<br>Preamble | FG | FG<br>SF | ADR<br>ADR | data<br>Data | FRM CHK<br>FRM CHK |    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| Rx Enable                |                           |    |          |            | <u> </u>     |                    | 1  |                                       |

| DMA Reg                  |                           |    |          |            | ,            |                    | L  |                                       |

| FIFO Half Full           |                           |    |          |            |              |                    |    |                                       |

| Synich/Hunt              |                           |    |          |            |              |                    |    |                                       |

| EOF                      |                           |    |          |            |              |                    |    |                                       |

| Special Cond INTRP       |                           |    |          |            |              |                    |    |                                       |

#### **Receiving logic facilities:**

Receive serialize-deserialize logic and its control circuitry. Receive Byte Count Register (keeps track of received bytes). Receive FIFO, 16 x 11 bits: 8-bit data, 3-bit status (Frame Error, Abort and End Of Frame). Receive Ring Frame Counter (keeps track of the number of receive bytes in the host Rx buffer). Receive Ring Frame Pointer (points to the last byte of the most recently received packet in the host Rx buffer).

T1 Start-up phase:

Set up Receive Control Registers per the receiving options. Set Receive Enable bit. FIR modem logic detects carrier, receive clock starts running. If continuous 1s are received, the receive clock may not be in sync with the incoming data.

T2 Flag(s)/Preambles detection:

When the start flag is detected, all counters in the receiver are initialized. Characters can be recognized from this point on. 0 deletion starts for 1Mbps mode only.

- **T3** Address matching: the first non-flag byte after the starting flag is the address. Depending on the address mode option, the frame can be rejected or receiving starts. If the frame is rejected, the receiver will look for the next starting flag and another address match.

- T4 Receive data:

When a byte of data is received, the data and the three status bits are stored in the Rx FIFO. If DMA is enabled, DMA Req is activated when the FIFO threshold level is reached. DMA continues until all data stored in the FIFO has been transferred to the host receive buffer. However, the three status bits in the FIFO are not transferred to the host. If DMA is not used, the Read Rx FIFO I/O command can be used. Read the status bits first, then read the data byte. If EOF or Abort is set to 1, the data byte just read is the last byte of the packet. If the FIFO is still not empty, the next entry is the beginning of another packet. The Receive Byte counter and Receive Ring Frame counter are increased accordingly.

T5 Closing flag:

When the closing flag is detected, the End Of Frame bit will set. CRC pattern is checked. Frame error is set if CRC is incorrect.

## T6 Post-frame phase:

DMA continues until all the received data in the FIFO has been transferred. Two more bytes will be stored in Rx FIFO and transmitted to the host receive buffer. Their format is:

| First byte:  | Bits 7-0 - byte count bits 7 to 0     |

|--------------|---------------------------------------|

| Second byte: | Bit 7 - Abort                         |

|              | Bit 6 - Frame Error                   |

|              | Bit 5 - Overrun                       |

|              | Bits 4 to 0 - Byte Count bits 12 to 8 |

DMA deactivates.

The Receive Ring Frame pointer is updated pointing to the second byte (see above) which has been stored successfully in the host Rx buffer.

If DMA is not used, the last two bytes will not be stored in the FIFO. Status bit EOF will be set at the last Frame Check byte received.

Steps T2 to T6 are repeated if continuous frame receiving is required.

# **1.7. Interrupt Handling**

Two subsystems in IBM31T1602 can generate host interrupts: the UART (SIR operation) and FIR controller. In direct mode there are four interrupt pins on the module that can be connected to any four host interrupts on the system board. They are: UART Interrupt (UIRQ pin 82), FIR Interrupt (FIRQ pin 83), IRQ3 (pin 49) and IRQ4 (pin 50). In Indirect and Plug and Play modes there are seven interrupt pins on the module that can be connected to any seven host interrupts on the ISA bus. They are: UART Interrupt (UIRQ/IRQ10 pin 82), FIR Interrupt (FIRQ/IRQ15 pin 83), IRQ3 (pin 49), IRQ4 (pin 50), IRQ5 (pin 86), IRQ11 (pin 99) and IRQ13 (pin 85).

The IBM31T1602 provides great flexibility for interrupt merging and routing. Setting the Advanced Interrupt Configuration bit (b3 of the Infrared Control Register) to 1 allows the UART Interrupt and the FIR interrupt to be routed to any of the external interrupt pins (see Interrupt Select bits in the UARTL and FIRL registers). If the Advanced Interrupt Configuration bit is set to 0, both the UART interrupt and the FIR interrupt are merged and can then be routed to IRQ3 or IRQ4. Once the configuration registers have been locked, further interrupts merging can be done by programming the Infrared Configuration 2 Register, which is one of the general control registers.

# **1.8.** External Transceiver Interface

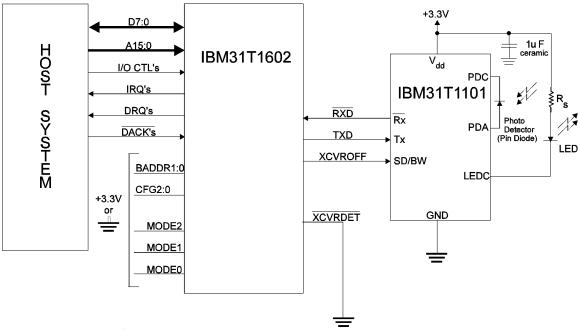

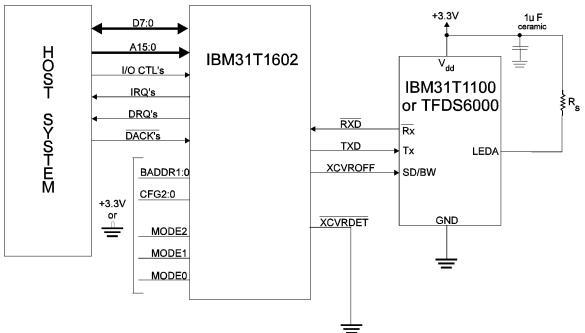

The IBM31T1602 can interface to the IBM31T1100 or IBM31T1101 transceivers with minimal circuitry. Only the following interface lines are used:

| TXD | Transmit data |

|-----|---------------|

|     |               |

**RXD** Receive data.

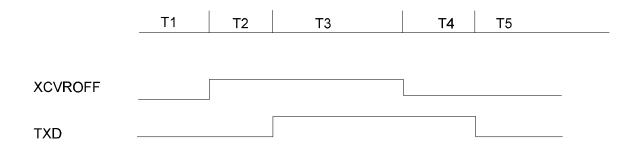

**XCVROFF** Transceiver off; powerdown and bandwidth switching control.

The IBM31T1100 and the IBM31T1101 transceivers require special control information when switching between low speed IrDA and high speed IrDA modes. A serial interface mechanism serves this purpose.

The IBM31T1602 is a 3.3 Volt part, whereas the IBM31T1100 and IBM31T1101 transceivers are 5 Volt parts. While the IBM31T1602 can receive the 5 Volt RXD signal, the TXD and XCVROFF signals to the transceivers must be buffered to 5 Volts.

If other transceivers are used, there are several other transceiver interface lines that can be used: **XCVRDET** Transceiver detect. **GPIO\_A - GPIO\_D** General Purpose Input/Output pins, controlled by internal registers.

Refer to *IBM31T1602 Infrared Controller Application Note* for information on connecting the IBM31T1602 to various transceivers.

# **1.9.** Power Management Feature

The IBM31T1602 powerdown operates two ways: complete shutdown or partial shutdown. In complete shutdown mode, clocks to all subsystems are disabled and minimum power dissipation is achieved. In partial shutdown mode, the subsystem that is not enabled or not in 'action' has its clocks disabled, leaving only the functional unit consuming required power.

To put the IBM31T1602 in complete powerdown mode, set En Power Down (b1 of the Power Down Register) to 1 and set Power Down (b0 of the Power Down Register) to 1, or activate (set low) the PWRDWN pin (this consumes the least amount of power); or, set En Infrared (b0 of the Infrared Configuration Register) to 0.

For partial powerdown mode, set En Power Down to 1, (the default value upon reset). Then, only the circuit that provides the function selected by the Infrared Configuration 1 Register will be active; the others will automatically shut down.

#### BUFFDIR RBUSY GPIOD ппппппппппп 76 MA10 E DRQ3/MA11 50 77 IRQ4 78 49 IRQ3 VDD **E** 79 48 DRQ0/MA14 C **コ** A15 DRQ1/MA13 80 47 **コ** A14 DRQ2/MA12 81 46 A13 IRQ10/UIRQ 45 82 IRQ15/FIRQ C 83 44 A12 VSS I 84 43 **A**11 IRQ13 85 42 **J** A10 IRQ5/SETUP 86 41 Α9 IBM31T1602 MODE0 87 40 RAMCE 100-pin LQFP 88 39 TME VDD **E** 89 38 GPIOC 37 CLK48 E 90 SA19 C 91 36 CFG2 AEN C 92 35 **3** A8 93 34 **J** A7 94 33 **⊐** A6 XCVRDET 95 32 **A**5 31 RXD2 C 96 CFG1 RXD1 97 30 **A**4 TXD C 98 29 CFG0 28 27 IRQ11 99 **A**3 IOCHRDY SER\_CLK C 100 26 SER\_DATA A1 BADDR0 A2 BADDR1 MW MAO Ao DACK1/MA6 DACK2/MA5 MODE2 DACK3/MA4 RESET DACK0/MA

### **1.10.** Pin Descriptions

| Table 1-2 (Page   | Table 1-2 (Page 1 of 6) Interface Configuration Signals                 |      |                                                                                                                                                                                                                                                           |  |  |  |

|-------------------|-------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal            | Pin                                                                     | Туре | Description                                                                                                                                                                                                                                               |  |  |  |

| BADDR1<br>-BADDR0 | 24, 22                                                                  | Ι    | Base Address Select. Select one of four base addresses of<br>the index and data ports which are used in accessing<br>indirect configuration registers. BADDR1-BADDR0 inputs<br>are used only in Indirect Configuration mode                               |  |  |  |

| CFG2<br>-CFG0     | 36, 31, 29                                                              | Ι    | Default Register Configuration Select. Sampled during an active chip reset cycle and in conjunction with MODE inputs, select the default settings of the indirect configuration registers. CFG2-CFG0 inputs are used only in Indirect Configuration mode. |  |  |  |

| A15 - A0          | 48, 47, 46, 44,<br>43, 42, 41, 35,<br>34, 33, 32, 30,<br>28, 23, 21, 20 | Ι    | System Address. 16-bit address bus provides addressing of IBM31T1602 registers and shared memory.                                                                                                                                                         |  |  |  |

| Table 1-2 (Page 2 of 6) Interface Configuration Signals |                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|---------------------------------------------------------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal                                                  | Pin             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| D7 - D0                                                 | 72, 71, 69, 68, | В    | System Data. 8-bit bidirectional system data bus transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                         | 65, 64, 61, 60  |      | data between the IBM31T1602, host processor, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                         |                 |      | external SRAM device. The data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                                         |                 |      | lines are tristated when not being driven.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| IOR                                                     | 93              | Ι    | I/O Read. This active-low input is asserted by the host processor during reads from the IBM31T1602                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| IOW                                                     | 94              | Ι    | I/O Write. This active-low input by the host processor during writes to the IBM31T1602.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| AEN                                                     | 92              | I    | Address Enable. When AEN is high, the host DMA controller has control of the ISA bus. AEN must be low before programmed I/O or shared memory accesses can be made to the IBM31T1602.                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| IOCHRDY                                                 | 27              | 0    | I/O Channel Ready. When driven low, this output extends<br>I/O and memory bus cycles. It is only used in Shared<br>Memory mode. In Host DMA mode, IOCHRDY is<br>tristated.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| IRQ3, IRQ4,<br>IRQ11, IRQ13                             | 49, 50, 99, 85  | 0    | Interrupt Request. When active, either the UART or the FIR<br>Controller is requesting service. These IRQs normally<br>operate in pulse mode. Advanced interrupt configuration<br>provides the capability to change these IRQs to active-low<br>interrupts. Advanced interrupt configuration also provides<br>independent routing of UART and FIR Controller internal<br>IRQ lines. These IRQs are tristated when they are not being<br>driven.                                                                         |  |  |  |

| IRQ10/UIRQ                                              | 82              | 0    | IRQ10/UART Subsystem Interrupt Request. In Indirect<br>Configuration mode, UAIRQ is a pulse-mode interrupt. In<br>Direct Configuration mode, UAIRQ is an active-high<br>interrupt. By using advanced interrupt configuration, both<br>the UART and FIR Controller can share the single UAIRQ<br>line. Also, advanced interrupt configuration provides the<br>capability to change UAIRQ to an active-low interrupt.<br>UAIRQ is tristated when not being driven.<br>In Plug and Play mode, this pin functions as IRQ10. |  |  |  |

| IRQ15/FIRQ                                              | 83              | 0    | IRQ15/FIR Controller Interrupt Request. In Indirect                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Table 1-2 (Page 2 | of 6) Interface Co | onfigurat | ion Signals                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-------------------|--------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal            | Pin                | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                   |                    |           | Configuration mode, FIRQ is a pulse-mode interrupt. In<br>Direct Configuration mode, FIRQ is an active-high<br>interrupt. By using advanced interrupt configuration, both<br>the UART and FIR Controller can share the single FIRQ<br>line. Also, advanced interrupt configuration provides the<br>capability to change FIRQ to an active-low interrupt. FIRQ<br>is tristated when not being driven. |  |

| DRQ3 - DRQ0       | 77, 81, 80, 79     | 0         | In Plug and Play mode, this pun functions as IRQ15.ODMA Request. Used to request a data transfer from the host<br>DMA controller. Up to two DMA request lines, one for<br>transmit and one for receive, may be used (selected during<br>configuration). The remaining DMA request lines are<br>tristated.                                                                                            |  |

|                   |                    |           | DRQ3-DRQ0 are used only in Host DMA mode. In Shared Memory mode, these pins become MA14-MA11.                                                                                                                                                                                                                                                                                                        |  |

| Table 1-2 (Page 3 | of 6) Interface Co | onfigurat |                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Signal            | Pin                | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DACK3             | 14, 17, 15, 16     | Ι         | DMA Acknowledge. When active, indicate the host DMA                                                                                                                                                                                                                                                                                                                                                  |  |

| DACK0             |                    |           | controller is acknowledging a corresponding DMA request (DRQ3 – DRQ0). Up to two DMA acknowledge lines, one                                                                                                                                                                                                                                                                                          |  |

|                   |                    |           | for transmit and one for receive, may be used (selected during configuration).                                                                                                                                                                                                                                                                                                                       |  |

|                   |                    |           | DACK3 - DACK0 lines are used only in Host DMA mode. In Shared Memory mode, these pins act as output pins for MA4-MA7.                                                                                                                                                                                                                                                                                |  |

| SA19 - SA16       | 91, 67, 63, 58     | Ι         | Extended System Address. Extension to System Address bus. Used to address shared memory.                                                                                                                                                                                                                                                                                                             |  |

|                   |                    |           | <b>Note:</b> The host memory window must be enabled. Also, the IBM31T1602 controller does not latch address bits 16 through 19 and so these pins must be connected to the appropriate SA address lines on the ISA and not the LA address lines.                                                                                                                                                      |  |

|                   |                    |           | In Host DMA mode these pins are ignored.                                                                                                                                                                                                                                                                                                                                                             |  |

| RAMCE             | 40                 | 0         | RAM Chip Enable. This active-low output is asserted by the IBM31T1602 when performing reads and writes to an                                                                                                                                                                                                                                                                                         |  |

|                   |                    |           | external SRAM device. RAMCE is used only in Shared                                                                                                                                                                                                                                                                                                                                                   |  |

|                   |                    |           | Memory mode. In Host DMA mode, RAMCE is tristated.                                                                                                                                                                                                                                                                                                                                                   |  |

| RAMRD             | 45                 | 0         | RAM Read. This active-low output is asserted by the IBM31T1602 when reading from an external SRAM                                                                                                                                                                                                                                                                                                    |  |

|                   |                    |           | device. $\overrightarrow{RAMRD}$ is used only in Shared Memory mode. In<br>Host DMA mode, $\overrightarrow{RAMRD}$ is tristated.                                                                                                                                                                                                                                                                     |  |

|                   | 51                 | 0         | RAM Write. This active-low output is asserted by the                                                                                                                                                                                                                                                                                                                                                 |  |

| RAMWR             |                    |           | IBM31T1602 when writing to an external SRAM device.                                                                                                                                                                                                                                                                                                                                                  |  |

|                   |                    |           | RAMWR is used only in Shared Memory mode. In Host DMA mode, RAMWR is tristated.                                                                                                                                                                                                                                                                                                                      |  |

| Table 1-2 (P | age 2 of 6) Interfa | ice Configurat | tion Signals                                                                                                                                                                                                                                            |  |

|--------------|---------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal       | Pin                 | Туре           | Description                                                                                                                                                                                                                                             |  |

|              |                     |                | external bidirectional drivers are used for the data pins.<br>BUFFDIR is active when:                                                                                                                                                                   |  |

|              |                     |                | The host processor is reading from an internal<br>IBM31T1602 register<br>The host DMA controller is reading from the IBM31T1602<br>FIR controller (Host DMA mode)<br>The host processor is reading from an external SRAM<br>device (Shared Memory mode) |  |

| Table 1-2 (Page 4 | of 6) Interface Co                                                | onfigurat | ion Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal            | Pin                                                               | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BUFFEN            | 56                                                                | 0         | <ul> <li>Buffer Enable. This active-low output can be used to enable external bidirectional drivers for the IBM31T1602 data pins. BUFFEN is active when:</li> <li>The IBM31T1602 is being accessed by the host processor The IBM31T1602 is being accessed by the host DMA controller in Host DMA mode</li> <li>An external SRAM device is being accessed by the host processor in Shared Memory mode</li> <li>Note: An external bidirectional driver is required for</li> </ul>                                                                                                                                         |

|                   |                                                                   |           | Shared Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                   |           | mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MA14 - MA0        | 79, 80, 81, 77,<br>76, 75, 74, 16,<br>15, 17, 14, 11,<br>9, 3, 19 | 0         | Shared Memory Address. When the &chip. is operating in<br>Shared Memory mode, these address lines are used to<br>address an external SRAM device. MA3-MA0 and MA10-<br>MA8 pins are tristated in Host DMA mode.                                                                                                                                                                                                                                                                                                                                                                                                         |

| MR                | 1                                                                 | Ι         | Memory Read. This active-low input is asserted by the host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                   |           | processor when performing memory reads. $\overline{MR}$ is used only in Shared Memory mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MW                | 25                                                                | Ι         | Memory Write. This active-low input is asserted by the host processor when performing memory writes. $\overline{MW}$ is used only in Shared Memory mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IRQ5/SETUP        | 86                                                                | В         | IRQ5/Setup Register Access. This active-low input is used<br>only when making I/O accesses to direct configuration<br>registers. When SETUP is active, the lower three bits of<br>the address bus are decoded to access one of eight direct<br>configuration registers. SETUP must be inactive when<br>performing all other I/O accesses. SETUP is used only in<br>Direct Configuration mode.<br>In Plug and Play mode, this pin is configured like all IRQs.<br>It is<br>selectable with advanced configuration in Indirect<br>Configuration mode,<br>and functions as the setup line in Direct Configuration<br>mode. |

| PWRDWN            | 88                                                                | Ι         | External Power Down. This active-low input is used in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Table 1-2 (Page 4 | Table 1-2 (Page 4 of 6) Interface Configuration Signals |      |                                                            |  |

|-------------------|---------------------------------------------------------|------|------------------------------------------------------------|--|

| Signal            | Pin                                                     | Туре | Description                                                |  |

|                   |                                                         |      | powering down the IBM31T1602 The power-down feature        |  |

|                   |                                                         |      | must be enabled before activating <b>PWRDWN</b>            |  |

| IRBUSY            | 54                                                      | 0    | IR Busy. When active, indicates that the IBM31T1602 is     |  |

|                   |                                                         |      | busy.                                                      |  |

| SER_DATA          | 26                                                      | В    | Serial PROM Data. This bidirectional pin is used in        |  |

|                   |                                                         |      | transferring data between the IBM31T1602 and an external   |  |

|                   |                                                         |      | serial PROM device.                                        |  |

| SER_CLK           | 100                                                     | 0    | Serial PROM Clock. This output is used to drive the serial |  |

|                   |                                                         |      | clock of an external serial PROM device.                   |  |

| CLK48             | 90                                                      | Ι    | Chip Clock. 48 MHz oscillator input.                       |  |

| Table 1-2 (Pag   | ge 5 of 6) Interface | Configura | tion Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

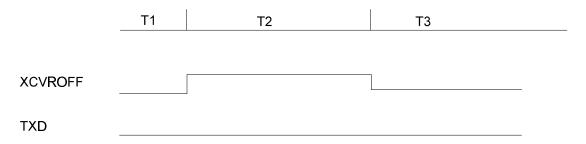

|------------------|----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|