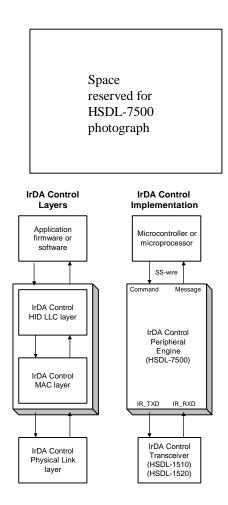

# IrDA<sup>a</sup> Control Compliant Peripheral Engine (PE)

File:

hsdl-7500\_datasheet\_v0.1au.pdf

# Technical Data

## Features

- Easy to use, all-in-one embedded communication controller

- Implements Endec, IrDA Control MAC layer, HID LLC layer

- All IrDA Control protocols available to a microprocessor or microcontroller via a simple command set.

- Simple 6-wire serial interface (SS-wire: Synchronous Serial wire) to mP/mC.

- Optimised interface to HP IrDA Control transceivers (HSDL-1510 and HSDL-1520).

- Low current consumption. I<sub>cc</sub>=3mA during operation.

- Low supply voltage. V<sub>DD</sub>=2.7 to 3.3V

## **Applications**

- Enables wireless capability for computer peripherals

- Computer peripherals: Mice, keyboards, joysticks, trackpads.

- Home appliances & consumer electronics: Televisions, HiFi sets, microwave ovens, universal remote controls

- Optimised for HP IrDA Control transceivers (HSDL-1510 or HSDL-1520) to peripheral or host processor.

## Description

The HSDL-7500 provides an optimised one-chip interface between a  $\mu P/\mu C$  and an IrDA Control transceiver (HSDL-1510 or HSDL-1520). It supports the full IrDA Control MAC and HID LLC layer services in hardware, making it easy to implement the IrDA Control protocol (compliant with Revision 1.0e). The HSDL-7500 also performs the modulation and demodulation functions used to

# PRELIMINARY

Thu Oct 1 15:57:41 SST 1998

## HSDL-7500

encode and decode the electrical pulses from the IrDA Control transceiver.

#### Preliminary Product Disclaimer

These products are under development. Until Hewlett-Packard (HP) releases these products for general sales, HP reserves the right at any time to alter prices, specifications, features, capabilities, functions, manufacturing release dates, and even general availability of the product. It is advisable to consult your local HP field sales engineer when considering these products for design-ins and production volumes.

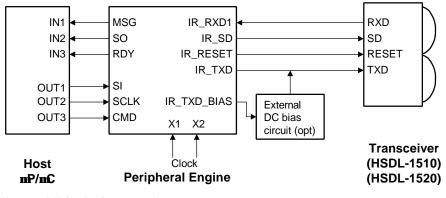

The PE can also be used in a host system, where it interfaces to a host  $\mu P/\mu C$  eg dongle to a host PC. Communication to the peripheral/host  $\mu P/\mu C$  is via a 6-wire serial interface with "Command" and "Message" attributes.

"Commands" are sent from the  $\mu P/\mu C$  to the PE, while the PE sends "messages" to the  $\mu P/\mu C$ . The message contents are the decode optical signals from the transceiver. Fig. 1 gives an overview of the connections and the grouping of I/O pins.

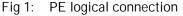

### Pinout

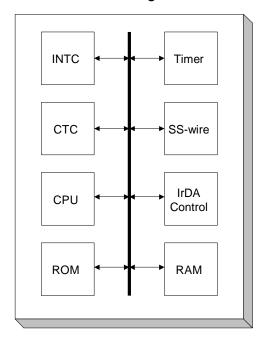

### **Functional Block Diagram**

### Fig. 3: HSDL-7500 Functional Block Diagram

#### **Preliminary Product Disclaimer**

These products are under development. Until Hewlett-Packard (HP) releases these products for general sales, HP reserves the right at any time to alter prices, specifications, features, capabilities, functions, manufacturing release dates, and even general availability of the product. It is advisable to consult your local HP field sales engineer when considering these products for design-ins and production volumes.

## I/O Pinout List

| Pin | Name            | Туре             | Function/Description                                                                                                                                                                                                                                                                                                                                              | Notes |

|-----|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 29  | SI              | In<br>(SS-wire)  | Serial input – from μP/μC                                                                                                                                                                                                                                                                                                                                         |       |

| 28  | SO              | Out<br>(SS-wire) | Serial output – to μP/μC                                                                                                                                                                                                                                                                                                                                          |       |

| 30  | SCLK            | In<br>(SS-wire)  | Serial data clock, from $\mu P/\mu C$ . Used to synch data transfers. When stopped SCLK=high.                                                                                                                                                                                                                                                                     |       |

| 26  | MSG             | Out<br>(SS-wire) | <ul> <li>Signal to μP/μC that PE holds a message. Active high signal, condition as follows:</li> <li>PE holds msg: PE asserts MSG. μP/μC must then issue Get_Message command to read in data.</li> <li>PE no msg: PE de-asserts MSG.</li> </ul>                                                                                                                   |       |

| 25  | RDY             | Out<br>(SS-wire) | Signal to $\mu P/\mu C$ for dataflow control. Active high<br>signal, asserted when the next byte can be<br>read/written through the data lines. The $\mu P/\mu C$ must<br>monitor the RDY line when it completes the last bit of<br>the current byte. If RDY is not asserted the $\mu P/\mu C$<br>should stop SCLK (SCLK=high) and wait until RDY is<br>asserted. |       |

| 27  | CMD             | In<br>(SS-wire)  | Signal from $\mu P/\mu C$ to indicate a command ID, active<br>high. The $\mu P/\mu C$ must assert CMD before sending<br>bit D7 of the command ID to SI. After sending bit D0<br>of the command ID, the $\mu P/\mu C$ must wait for RDY to<br>be asserted, then de-assert CMD (low).                                                                               |       |

| 8   | IR_TXD          | Out              | Data to HSDL-1510/HSDL-1520 transceiver input (T <sub>XD</sub> pin)                                                                                                                                                                                                                                                                                               |       |

| 10  | IR_TXD_BIAS     | Out              | DC bias output for transceiver LED drive.<br>(Use of DC Bias is not yet ratified in IrDA Control specification)                                                                                                                                                                                                                                                   |       |

| 11  | IR_TXD_LPFC     | Out              | n/c                                                                                                                                                                                                                                                                                                                                                               |       |

| 6   | IR_RXD1         | In               | Data from HSDL-1510/HSDL-1520 transceiver output (R <sub>XD</sub> pin)                                                                                                                                                                                                                                                                                            |       |

| 4   | IR_RXD2         | In               | n/c                                                                                                                                                                                                                                                                                                                                                               |       |

| 2   | IR_SD           | Out              | Signal to shutdown HSDL-1510/HSDL-1520 transceiver (SD pin).                                                                                                                                                                                                                                                                                                      |       |

| 3   | IR_RESET        | Out              | Signal to reset HSDL-1510/HSDL-1520 transceiver receiver sensitivity (RESET pin).                                                                                                                                                                                                                                                                                 |       |

| 35  | RST             | In               | PE hardware reset                                                                                                                                                                                                                                                                                                                                                 |       |

| 31  | X1              | In               | Clock input (6MHz)                                                                                                                                                                                                                                                                                                                                                |       |

| 33  | X2              | Out              | n/c                                                                                                                                                                                                                                                                                                                                                               |       |

|     | V <sub>DD</sub> |                  | Power                                                                                                                                                                                                                                                                                                                                                             |       |

|     | Gnd             |                  | Chip ground                                                                                                                                                                                                                                                                                                                                                       |       |

#### Preliminary Product Disclaimer

These products are under development. Until Hewlett-Packard (HP) releases these products for general sales, HP reserves the right at any time to alter prices, specifications, features, capabilities, functions, manufacturing release dates, and even general availability of the product. It is advisable to consult your local HP field sales engineer when considering these products for design-ins and production volumes.