## **Philips Semiconductors**

Interconnectivity

May 29, 1999

# **Philips USB-to-ATA Bridge**

## **Table of Contents**

| FEATURES                    | 2 |

|-----------------------------|---|

| SYSTEM ARCHITECTURE         | 2 |

| System Block Diagram        | 2 |

| Hardware Block Diagram      | 3 |

| Firmware Block Diagram      | 4 |

| Host Software Block Diagram | 5 |

Interconnectivity Page 2 of 5

### **USB-to-ATA Bridge**

### **Features**

Our proposed Philips Semiconductors USB-to-ATA bridge is a low-cost and flexible system solution.

This bridge can connect IDE hard disk, ATAPI CD-ROM drive, ATAPI Flash disk and other ATA devices to the USB bus. It enhances the accessibility of ATA devices with HotSwap and Plug and Play (PnP) support.

This bridge follows the following standards:

- Universal Serial Bus Specification Revision 1.1

- AT attachment-3 Interface

- Universal Serial Bus Mass Storage Class Revision 1.0

- Reduced Block Commands Revision 1.0

- Control/Bulk/Interrupt (CBI) Transport

## **System Architecture**

- System Block Diagram

- Hardware Block Diagram

- Firmware Block Diagram

- Host Software Block Diagram

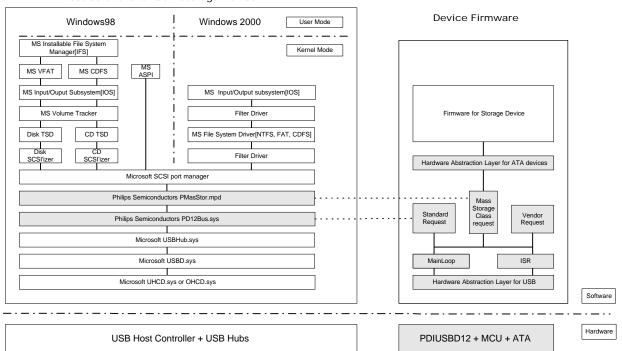

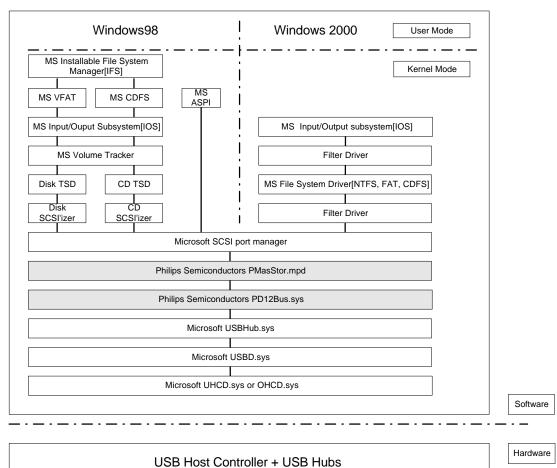

### System Block Diagram

Host Software for USB Storage Device

Interconnectivity Page 3 of 5

### **USB-to-ATA Bridge**

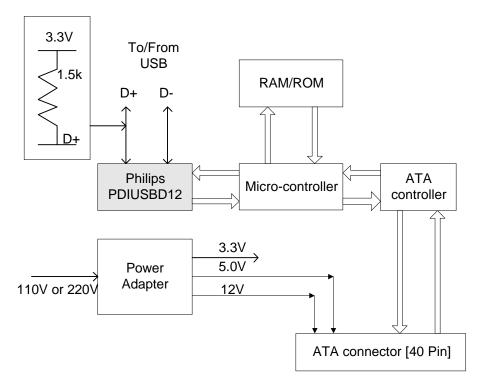

### Hardware Block Diagram

#### **Power Supply**

5 V and 12 V power source are used to supply ATA devices.

#### PDIUSBD12

A USB interface chip supports USB Control/Bulk/Interrupt (CBI) Transport. It has high ESD (8 kV), optimized register definition, and is offered in TSSOP28 and SO28 packages.

#### Microcontroller

Any microcontroller can be used, including 8051.

#### **ATA Controller**

An ATA controller has a data buffer of only 16 bits. It can be implemented in PLD.

These ATA signals are required:

DD[15:0], /DIOR,/DIOW,IORDY,CSEL,DA[2:0], PDIAG,/CS0,/CS1,/DASP

These ATA signals are optional:

DMARQ, /DMACK, INTRQ

Interconnectivity Page 4 of 5

## **USB-to-ATA Bridge**

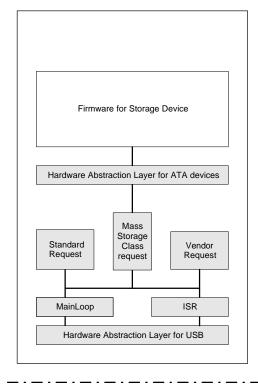

### Firmware Block Diagram

#### **Device Firmware**

#### Main Loop - MAINLOOP.C

The main loop routine checks the event flags and passes the events to the appropriate subroutine for further processing. It also contains the code for LED control and key scan.

#### Interrupt service routine - ISR.C

This part of the code handles interrupts generated by PDIUSBD12. It retrieves data from PDIUSBD12's internal FIFO, and sets up proper event flags to inform the main loop routine for further processing.

# Hardware Abstraction Layer for USB interface - HAL4USB.C

This function set supports PDIUSBD12 access.

#### USB Standard Request Handler - CHAP\_9.C

This handler support the requests defined in USB Spec Chapter 9.

# Hardware Abstraction Layer for ATA interface - HAL4ATA.C

This function set handles register-level access to ATA devices.

### Request Command Set - RBC.C

This function set handles Request Block Command set.

#### USB Class Request Handler - MASSSTOR.C

This handler supports USB Mass Storage Class Revision 1.0.

#### USB Vendor Request Handler for PhilipsD12 Bus - PD12BUS.C

This handler supports Philips Vendor Request to manage the *PhilipsD12 bus*: a bus that extends the D12 interface chip's functionality from single-device support to multiple-device support.

Software

Interconnectivity Page 5 of 5

## **USB-to-ATA Bridge**

# Host Software Block Diagram

### Host Software for USB Storage Device

#### PMasStor.mpd

A Philips SCSI miniport driver to support the mass storage devices on the PhilipsD12 bus. PmasStor.mpd uses Request Block Command to communicate with ATA devices.

### PD12Bus.sys

Philips USB WDM Bus driver is coded for the PhilipsD12 bus.

PD12Bus.sys is in charge of device enumeration, Plug and Play, and power management.