# USB97C196

# USB to Ethernet Bridge Controller with Integrated USB Hub

## FEATURES

### **USB** Interface

- USB to Ethernet Bridge Device

- Integrated USB Hub Provides 1 Downstream USB Port

- Supports Bus- or Self-Powered Operation

- High Performance USB Peripheral

- Controller Engine

- Integrated USB Transceiver

- Serial Interface Engine (SIE)

- Compliant to USB Rev 1.1 Core Specification

- Supports dedicated Isochronous, Bulk, Interrupt, and Control Data Endpoints

- Dynamic Hardware Allocation of Packet Buffer for Virtual Endpoints

- Dynamic Endpoint Buffer Length Allocation (0-1280 Byte Packets)

- Device Supports Self Powered or Bus

Powered Designs

## System Level Interface

- Embedded 8051 Micro controller (MCU)

- Standard 8051 "Stop Clock" Modes

- Additional USB and Ethernet Suspend /Resume Events

- Internal 8MHz Ring Oscillator for Immediate Low Power Code Execution

- 24, 16, 12, 8, 4, and 2 MHz PLL

- Taps For on the Fly MCU Clock

- Shared USB/Ethernet Memory Management Unit (MMU)

- 4096 Byte RAM On Board USB/Ethernet Packet Buffer

- USB Bus Snooping Capabilities

- 128 Byte Min. Page Size

- 12 Pages Maximum per Ethernet

Packet or USB Bulk Assembled Buffer

- Up to 32 Deep Receive Packet Queue for USB and Ethernet

- Up to 5 Deep Transmit Packet Queue, per Endpoint

- Hardware Generated Packet

Descriptor FIFO, Records Each

Logical Packet Status Automatically

- Simultaneous Buffer Arbitration Between MCU, SIE, and CSMA/CD Accesses

- Extended Power Management

- Independent Clock/Power

- Management for SIE, MMU, and CSMA/CD Blocks

- External MCU Memory Interface

- Up to 128k Byte Code and Data Storage

- Flash, SRAM, or EPROM

- Downloadable Code via USB, Serial Port

#### **Network Interface**

- Integrates 10BASE-T Transceiver Functions:

- Driver and Receiver

- Link Integrity Test

- Receive Polarity Detection and Correction

- Integrates AUI Interface

- Supports Standard 10Mbps and 1Mbps Data Rates

- Implements 10 Mbps Manchester Encoding/Decoding and Clock Recovery

- Device Able to Transmit and Receive Data Down to 1 Mbps for Home Networking Applications

- 7-Wire Serial ENDEC Interface Allows Connection to Home Networking Phys

- Automatic Retransmission, Bad Packet Rejection, and Transmit Padding

- External and Internal Loopback Modes

- Three (3) Direct Driven LEDs for Status/ Diagnostics

- Supports OnNow Technology via Packet Filtering Power Management Technology

- High Performance Chained ("Back-to-Back") Transmit and Receive Operations

- 3.3 Volt, Low Power Operation

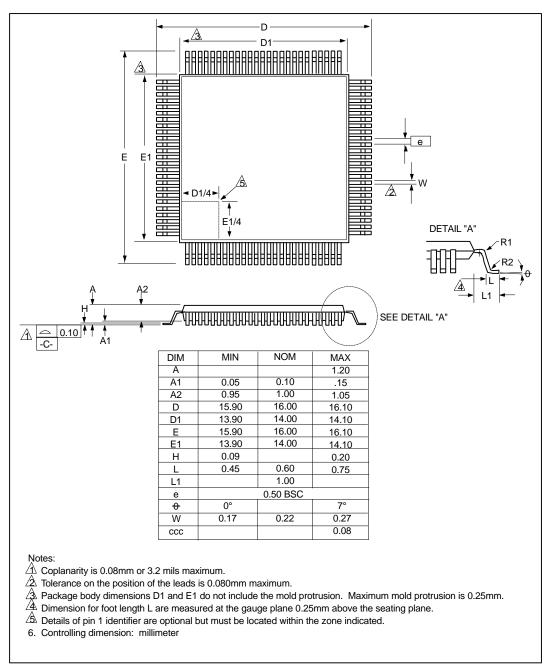

- 100 Pin TQFP Package

#### **GENERAL DESCRIPTION**

The SMSC USB97C196 is a USB to Ethernet bridge device. The device allows a simple and full-featured link allowing connectivity to an Ethernet LAN via a USB connection. Its unique dynamic buffer architecture overcomes the throughput disadvantages of existing fixed FIFO buffer schemes allowing maximum utilization of the USB connection's overall bandwidth. This architecture minimizes the integrated microcontroller's participation in the USB data flow, allowing back-to-back packet transfers to LAN oriented devices. The efficiency of this architecture allows a high data throughput via a "store and forward" architecture.

The SMSC USB97C196 allows external program code to be downloaded over the USB to allow easy implementation of varied peripheral USB Device Classes and combinations. This also provides a method for convenient field upgrades and modifications.

Standard Microsystems is a registered trademark and SMSC is a trademark of Standard Microsystems Corporation. Other product and company names are trademarks or registered trademarks of their respective holders.

## TABLE OF CONTENTS

| FEATURES                                                                      |      |

|-------------------------------------------------------------------------------|------|

| GENERAL DESCRIPTION                                                           |      |

| PIN CONFIGURATION                                                             | 6    |

| DESCRIPTION OF PIN FUNCTIONS                                                  | 7    |

| BUFFER TYPE DESCRIPTIONS                                                      | . 11 |

| FUNCTIONAL DESCRIPTION                                                        | . 13 |

| Serial Interface Engine (SIE)                                                 | . 13 |

| Micro Controller Unit (MCU)                                                   |      |

| SIEDMA                                                                        | . 13 |

| Memory Management Unit (MMU) Register Description                             | . 13 |

| Specific Support for USB Based SAR as Defined in the USB CDC Specification    | . 13 |

| Data Transfer Management via a USB Bulk Endpoint Pair                         |      |

| Assembly of Multiple USB Bulk Packets into an Ethernet Frame                  |      |

| Segmentation of an Ethernet Frame into Multiple USB Bulk Packets              | . 20 |

| Ethernet Packet Reception                                                     |      |

| APPLICATIONS                                                                  |      |

| TYPICAL SYSTEM IMPLEMENTATION                                                 | . 21 |

| CDC Device Class Requirements for the SMSC USB97C196                          |      |

| USB TO ETHERNET CDC DEVICE CLASS ENDPOINT ALLOCATION                          | . 24 |

| MCU Memory Map                                                                | . 25 |

| Code Space                                                                    |      |

| Data Space                                                                    | . 25 |

| Data Space and Code Space mappings                                            | . 26 |

| MCU Block Register Summary                                                    | . 28 |

| MMU Block Register Summary                                                    | . 29 |

| SIE Block Register Summary                                                    |      |

| EPH (Ethernet) Block Register Summary                                         |      |

| DESCRIPTION                                                                   | . 32 |

| MCU REGISTER DESCRIPTIONS                                                     | . 33 |

| MCU Runtime Registers                                                         | . 33 |

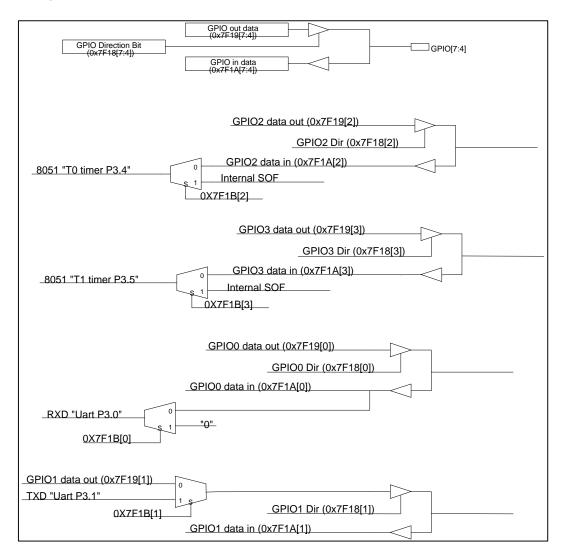

| GENERAL PURPOSE IO REGISTER DEFINITIONS                                       |      |

| GPIO Direction Register                                                       |      |

| GPIO Output Register                                                          |      |

| GPIO Input Register                                                           |      |

| Utility Configuration Register                                                | . 42 |

| GPIÓ MUXING BLOCK DIAGRAM                                                     |      |

| DEVICE POWER MANAGEMENT                                                       |      |

| USB97C196 Power States                                                        |      |

| ETHERNET Function                                                             |      |

| USB SIE Function                                                              |      |

| Network Device Power Conservation transition table (Systems Engineering Note) |      |

| MCU Power Management and Utility Registers                                    | . 46 |

| Code FLASH Bank Select Register                                               |      |

| Wakeup Source 1 Register                                                      |      |

| Wakeup Mask 1 Register                                                        | . 47 |

| RUNTIME REGISTERS                                                                       |    |

|-----------------------------------------------------------------------------------------|----|

| Ethernet Transmit Control Register1                                                     | 48 |

| Ethernet Transmit Control Register2                                                     | 48 |

| EPH STATUS REGISTER1                                                                    |    |

| EPH STATUS REGISTER2                                                                    | 50 |

| Ethernet Receive Control Register 1                                                     |    |

| Ethernet Receive Control Register 2                                                     |    |

| Ethernet Counter Register1                                                              |    |

| Ethernet Counter Register2                                                              | 53 |

| Ethernet Configuration Register 1                                                       | 54 |

| Ethernet Configuration Register 2                                                       | 55 |

| INDIVIDUAL ADDRESS REGISTER 0 - 5                                                       | 55 |

| MEMORY MANAGEMENT UNIT (MMU) REGISTER DESCRIPTIONS                                      |    |

| USB / Ethernet MMU Data Window Register                                                 |    |

| USB / Ethernet Pointer Register (Low)                                                   | 60 |

| USB / Ethernet Pointer Register (High)                                                  |    |

| SIE Transmit FIFO Select Register                                                       |    |

| MMU Command Register                                                                    |    |

| MMU Command Sequencing                                                                  |    |

| Allocation Result Register                                                              | 65 |

| Packet Number and Byte Count Registers                                                  |    |

| Packet Number Register                                                                  |    |

| Byte Count Register High                                                                |    |

| Byte Count Register Low                                                                 | 66 |

| Byte Count Conversion Registers                                                         | 67 |

| Byte Count Conversion Register High                                                     | 68 |

| Byte Count Conversion Register Low                                                      | 68 |

| USB and Ethernet POP Registers                                                          |    |

| USB Tx FIFO POP Register                                                                | 69 |

| USB Tx Done FIFO POP Register                                                           |    |

| Ethernet Tx Awaiting FIFO Register                                                      |    |

| Ethernet Tx Done FIFO POP Register                                                      |    |

| MEMORY INFORMATION REGISTER<br>USB Receive Data Packet Number and Length FIFO Registers | 71 |

| USB Receive Data Packet Number and Length FIFO Registers                                | 72 |

| USB Receive FIFO Packet Length Register Low                                             |    |

| USB Receive FIFO Packet Length Register High                                            |    |

| Ethernet Receive Data Packet Number and Length FIFO Registers                           | 72 |

| ETHERNET Receive Packet Number FIFO Register                                            | 13 |

| ETHERNET Receive FIFO Packet Length Register Low                                        | 13 |

| ETHERNET Receive FIFO Packet Length Register High                                       | 13 |

| USB Transmit FIFO Status Registers                                                      | 73 |

| USB Transmit FIFO Status Register A                                                     |    |

| USB Transmit FIFO Status Register B                                                     | 75 |

| USB TX / RX Management Register 1                                                       | 76 |

| PACKET HEADER DEFINITION.                                                               | 77 |

| SERIAL INTERFACE ENGINE (SIE) REGISTER DESCRIPTION                                      | 79 |

| SERIAL INTERFACE ENGINE (SIE) REGISTER DESCRIFTION                                      | 10 |

| Packet Header Definition                                   |     |

|------------------------------------------------------------|-----|

| Ethernet Transmit and Receive packet Status RAM definition | 79  |

| Ethernet RECEIVE FRAME STATUS WORD                         |     |

| Ethernet Transmit FRAME STATUS WORD (in Status RAM)        | 80  |

| SERIAL INTERFACE ENGINE (SIE) REGISTER DESCRIPTION         | 82  |

| Endpoint Control Registers                                 | 82  |

| NonControl Endpoint Register                               | 84  |

| Endpoint Command Register                                  | 85  |

| LSB FRAME Count Register                                   | 87  |

| MSB FRAME Count Register                                   | 87  |

| Local Address Register                                     |     |

| Alternate Address Register                                 | 88  |

| SIE Status Register                                        | 88  |

| SIE Control Register 1                                     |     |

| SIE Control Register 2                                     |     |

| SIE Configuration Register 1                               |     |

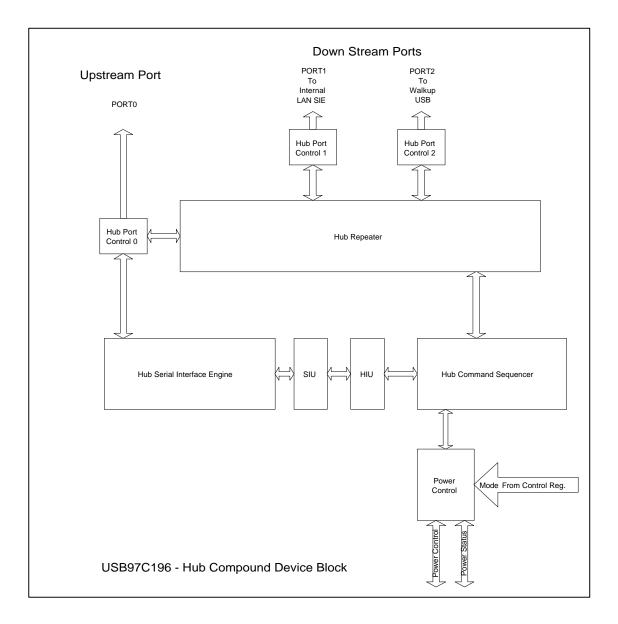

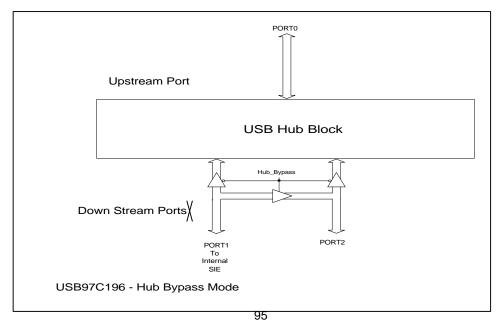

| USB HUB BLOCK                                              |     |

| SIU System Interface Unit                                  |     |

| HIU Hub Interface Unit                                     | 93  |

| HUB Block Register Summary                                 | 94  |

| Hub Control Register 1                                     | 95  |

| Hub Control Register 2                                     | 96  |

| DC PARAMETERS                                              | 97  |

| I/O16 Type Buffer                                          | 98  |

| I/O24 Type Buffer                                          |     |

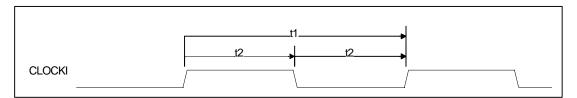

| INPUT CLOCK TIMING                                         |     |

| INPUT CLOCK TIMING                                         | 101 |

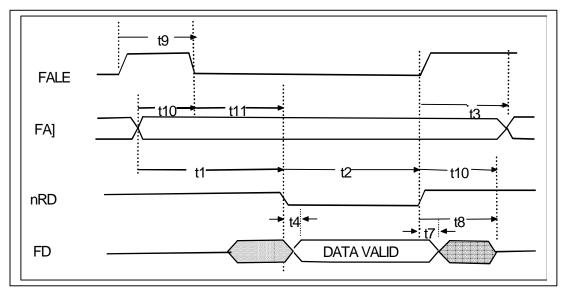

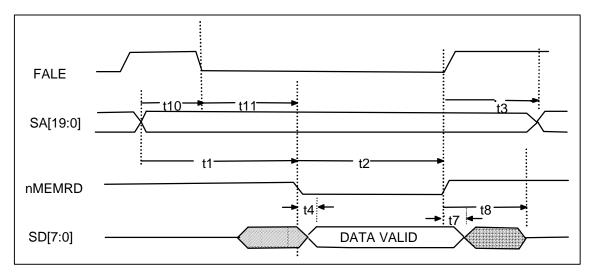

| 8051 FLASH MEMORY READ TIMING                              |     |

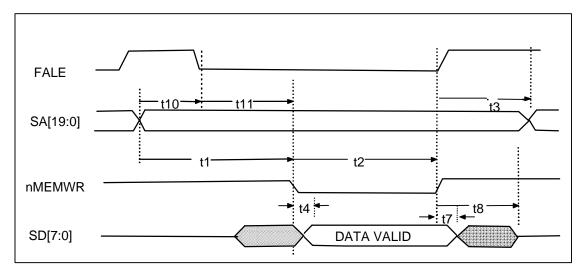

| 8051 FLASH MEMORY WRITE TIMING                             | 103 |

| RESET_IN TIMING                                            | 104 |

80 Arkay Drive Hauppauge, NY. 11788 (516) 435-6000 FAX (516) 273-3123

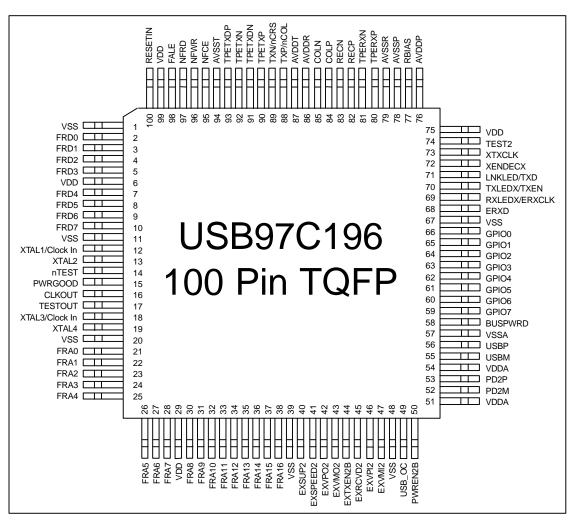

#### **PIN CONFIGURATION**

## **DESCRIPTION OF PIN FUNCTIONS**

# Table 1 - SMSC USB97C196 Pin Configuration

| TQFP<br>PINS | SYMBOL             | PIN DESCRIPTION                                                                                                                                                                                                        | BUFFER<br>TYPE |  |  |

|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

|              | Crystal INTERFACE  |                                                                                                                                                                                                                        |                |  |  |

| 12           | XTAL1/<br>Clock In | USB 24 MHz Crystal or Clock Input:<br>This pin can be connected to one terminal of the crystal or can<br>be connected to an external clock when a crystal is not used.                                                 | ICLKx          |  |  |

| 13           | XTAL2              | USB 24 MHz Crystal:<br>This is the other terminal of the crystal.                                                                                                                                                      |                |  |  |

| 18           | XTAL3/<br>Clock In | Ethernet 20 MHz Crystal or Clock Input:<br>This pin can be connected to one terminal of the crystal or can<br>be connected to an external clock when a crystal is not used.                                            | ICLKx          |  |  |

| 19           | XTAL4              | Ethernet 20 MHz Crystal:<br>This is the other terminal of the crystal.                                                                                                                                                 | OCLKx          |  |  |

|              |                    | USB INTERFACE                                                                                                                                                                                                          |                |  |  |

| 52,53        | PD2M, PD2P         | <b>USB Downstream Connection signals :</b> These are two point-<br>to-point signals and are driven differentially<br>PD2P, PD2M are used as a standard "Walk Up" USB Port.                                             | IOUSB          |  |  |

| 50           | PWREN2B            | <b>USB Power Enable</b> – A low signal on this pin applies power to the downstream USB port. This output signal is active Low.                                                                                         | O24            |  |  |

| 49           | USB_OC             | <b>USB Over-Current Sense.</b> Input to indicate an over-current condition for a bus powered USB device on the downstream port. This input signal is active Low.                                                       | I              |  |  |

| 55,56        | USBM,USBP          | USB Upstream Connection Signals<br>These are two point-to-point signals and driven differentially.                                                                                                                     | IOUSB          |  |  |

| 44           | EXTXEN2B           | <b>USB transceiver Output Enable</b> – This Pin which is active<br>low, enable the external transceiver to transmit data on the USB<br>bus. When this signal is not active (1), the transceiver is in<br>receive mode. | O8             |  |  |

| 41           | EXSPEED2           | <b>USB suspend</b> - Enables a low power state in the external transceiver while the USB is suspended.                                                                                                                 | O8             |  |  |

| TQFP  |                    |                                                                                                                                                                                     | BUFFER                                 |  |

|-------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| PINS  | SYMBOL             | PIN DESCRIPTION                                                                                                                                                                     |                                        |  |

| 42,43 | EXVPO2,<br>EXVMO2  | <b>Outputs to External Differential Driver</b> – This is the output from the SIE to the associated USB port external transceiver                                                    | O24                                    |  |

|       |                    | VPO VMO Result                                                                                                                                                                      |                                        |  |

|       |                    | 0 0 SE0                                                                                                                                                                             |                                        |  |

|       |                    | 0 1 Logic "0" on USB BUS                                                                                                                                                            |                                        |  |

|       |                    | 1 0 Logic "1" on USB BUS<br>1 1 Undefined                                                                                                                                           |                                        |  |

| 45    | EXRCVD2            | Receive Data from USB Transceiver differential input                                                                                                                                |                                        |  |

| 46,47 | EXVPI2,            | Inputs from External Differential Driver – These signals                                                                                                                            |                                        |  |

| 40,47 | EXVMI2             | are used to detect a single ended zero (SE0, error<br>conditions and interconnect speed from the associated<br>USB port external transceiver. (Inputs to internal USB SIE<br>block) | •                                      |  |

|       |                    | VP VM Result                                                                                                                                                                        |                                        |  |

|       |                    | 0 0 SE0                                                                                                                                                                             |                                        |  |

|       |                    | 0 1 Low Speed on USB BUS                                                                                                                                                            |                                        |  |

|       |                    | 1 0 High (Full) Speed on USB<br>BUS                                                                                                                                                 |                                        |  |

|       |                    | 1 1 ERROR                                                                                                                                                                           |                                        |  |

| 40    | EXSUP2             | <b>Suspend</b> – This input signal when active high (1) will force a low power state on the associated USB port logic.                                                              |                                        |  |

|       | ·                  | 10BASE-T interface                                                                                                                                                                  |                                        |  |

| 88,89 | TXP/nCOLL          | INTERNAL ENDEC - (nXENDEC pin open). In this mode                                                                                                                                   | Differ-                                |  |

|       | TXN/nCRS           | TXP and TXN are the AUI transmit differential outputs. They must be externally pulled up using 150 ohm resistors.                                                                   | ential<br>Output / I                   |  |

|       |                    | EXTERNAL ENDEC - (nXENDEC pin tied low). In this mode the pins are inputs used for collision and carrier sense functions.                                                           |                                        |  |

| 80,81 | TPERXP<br>TPERXN   | 10BASE-T receive differential inputs.                                                                                                                                               |                                        |  |

| 90,92 | TPETXP<br>TPETXN   | INTERNAL ENDEC - 10BASE-T transmit differential outputs.                                                                                                                            | Differ-<br>ential<br>Output<br>Differ- |  |

| 93,91 | TPETXDP<br>TPETXDN | 10BASE-T delayed transmit differential outputs. Used in combination with TPETXP and TPETXN to generate the 10BASE-T transmit pre-distortion.                                        |                                        |  |

| TQFP             |           |                                                                  | BUFFER   |

|------------------|-----------|------------------------------------------------------------------|----------|

| PINS             | SYMBOL    | PIN DESCRIPTION                                                  | TYPE     |

| 71               | nLNKLED/  | INTERNAL ENDEC - Link LED output.                                | OD16/    |

|                  | TXD       | EXTERNAL ENDEC - Transmit Data output.                           |          |

| 82,83            | RECP,RECN | AUI receive differential inputs.                                 |          |

| ,                | ,         | l e                                                              |          |

|                  |           |                                                                  | Input    |

| 84,85            | COLP,COLN | AUI collision differential inputs. A collision is indicated by a | Differ-  |

|                  |           | 10MHz signal at this input pair.                                 | ential   |

|                  |           |                                                                  | Input    |

| 70               | nTXLED/   | INTERNAL ENDEC - Transmit LED output.                            | OD16/    |

|                  | nTXEN     |                                                                  | O162     |

|                  |           | EXTERNAL ENDEC - Active low Transmit Enable output.              |          |

| 68               | ERXD      | INTERNAL ENDEC – This pin is not used when the Internal          |          |

|                  |           | ENDEC is enabled.                                                | I with   |

|                  |           | EXTERNAL ENDEC - NRZ receive data input.                         | pullup   |

| 73               | XTXCLK    | Transmit clock input from external ENDEC. Used, only when        | IP       |

|                  |           | External ENDEC is used.                                          |          |

| 69               | nRXLED/   | INTERNAL ENDEC - Receive LED output.                             | OD16/    |

|                  | RXCLK     |                                                                  | I with   |

|                  |           | EXTERNAL ENDEC - Receive clock input.                            | pullup   |

|                  |           | Ethernet Misc. and LEDs                                          |          |

| 77               | RBIAS     | A 22kohm 1% resistor should be connected between this pin        | N/A      |

|                  |           | and analog ground.                                               |          |

| 72               | NXENDEC   | When tied low the SMSC USB97C196 is configured for               | IP       |

|                  |           | EXTERNAL ENDEC. When tied high or left open the SMSC             |          |

|                  |           | USB97C196 will use its Internal ENDEC                            |          |

|                  |           | FLASH INTERFACE                                                  | 10-      |

| 10,9,8,          | FRD[7:0]  | Flash ROM Data Bus                                               | IO8      |

| 7,5,4,3          |           | These signals are used to transfer data between 8051 and         |          |

| ,2               |           | the external FLASH.                                              |          |

| 38,37,           | FRA[16:0] | 128K Flash ROM Address Bus                                       | O8       |

| 36,35,           |           | These signals address memory locations within the                |          |

| 34,33,           |           | FLASH.                                                           |          |

| 32,31,<br>30,28, |           |                                                                  |          |

| 30,28, 27,26,    |           |                                                                  |          |

| 27,26, 25,24,    |           |                                                                  |          |

| 23,24, 23,22,    |           |                                                                  |          |

| 23,22,           |           |                                                                  |          |

| 97               | NFRD      | Flash ROM Read; active low                                       | O8       |

| 96               | NFWR      | Flash ROM Write; active low                                      | 00<br>08 |

| 90               | INI VVIN  |                                                                  | 00       |

| TQFP                                 |                  |                                                                                                                                                                                                  | BUFFER |

|--------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| PINS                                 | SYMBOL           | PIN DESCRIPTION                                                                                                                                                                                  | TYPE   |

| 95                                   | NFCE             | Flash ROM Chip Select; active low                                                                                                                                                                |        |

| 98                                   | FALE             | Flash ROM address latch enable                                                                                                                                                                   | O8     |

|                                      | •                | POWER SIGNALS                                                                                                                                                                                    |        |

| 6,29,<br>75,99                       | VDD              | +3.3 V Power                                                                                                                                                                                     | NA     |

| 51,54                                | VDDA             | Digital 3.3V Power Reference for USB Ports                                                                                                                                                       | NA     |

| 87                                   | AVDDT            | Analog power for Ethernet Transmitter                                                                                                                                                            | NA     |

| 86                                   | AVDDR            | Analog power for Ethernet Receiver                                                                                                                                                               | NA     |

| 76                                   | AVDDP            | Analog power for PLL Circuit of Ethernet                                                                                                                                                         | NA     |

| 94                                   | AVSST            | Analog Ground Reference for Ethernet Transmitter                                                                                                                                                 | NA     |

| 79                                   | AVSSR            | Analog Ground Reference for Ethernet Receiver                                                                                                                                                    | NA     |

| 78                                   | AVSSP            | Analog Ground Reference for PLL Circuit                                                                                                                                                          | NA     |

| 1, 11,<br>20,<br>39,48,<br>67        | VSS              | Digital Ground Reference NA                                                                                                                                                                      |        |

| 57                                   | VSSA             | Digital Ground Reference for USB Ports                                                                                                                                                           | NA     |

|                                      | •                | MISCELLANEOUS                                                                                                                                                                                    |        |

| 59,60,,<br>61,62,<br>63,64,<br>65,66 | GPIO[7:0]        | General Purpose I/O.<br>These pins can be configured as inputs or outputs under<br>software control.                                                                                             | I/O16  |

| 58                                   | USB_Bus_<br>Pwrd | USB Power Selection<br>This pin is used to select the device to implement a USB<br>Bus Power or Self Powered mode.                                                                               | I      |

| 100                                  | RESET_IN         | Power on reset; active high<br>This signal is used by the system to reset the chip. It also<br>generates an internal POR.                                                                        | I      |

| 17                                   | TST_OUT          | XNOR chain output<br>This signal is used for testing the chip via an internal<br>XNOR Chain.<br>Output only when PWRGOOD is low, otherwise it is<br>Tri-state.                                   | O8     |

| 74                                   | TEST2            | Reserved for TEST                                                                                                                                                                                | 0      |

| 14                                   | NTEST            | Test input<br>This signal a manufacturing test pin. User can pull it high<br>or leave it unconnected.<br>When NTEST is low, it combines with PWRGOOD for 2<br>8051 modes, otherwise it is a NOP. | IP     |

| TQFP<br>PINS | SYMBOL  | PIN DESCRIPTION                                                                                                                                                                                                                                                                                    | BUFFER<br>TYPE |

|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 15           | PWRGOOD | Power good input. It keeps the SMSC USB97C196 in power down mode when low. Must be high for normal operation.                                                                                                                                                                                      | I              |

| 16           | CLKOUT  | <b>Clock output -</b> The clock frequency is the same as the 8051 running clock.<br>This clock is stopped when the 8051 is stopped. Peripherals should not use this clock when they are expected to run when the 8051 is stopped. This clock can be used to synchronize other devices to the 8051. | O8             |

## **BUFFER TYPE DESCRIPTIONS**

## Table 2 - SMSC USB97C196 Buffer Type Description

| BUFFER | DESCRIPTION                               |

|--------|-------------------------------------------|

| I      | Input (no pull-up)                        |

| IP     | Input 90µA with internal pull-up          |

| O8     | Output with 8mA drive                     |

| I/O8   | Input/output with 8mA drive               |

| I/O16  | Input/output with 16mA drive              |

| O24    | Output, 24mA sink, 12mA source.           |

| ICLKx  | XTAL clock input                          |

| OCLKx  | XTAL clock output                         |

| ICLK   | Clock input (TTL levels)                  |

| IOUSB  | Defined in USB specification; uses VDD3.3 |

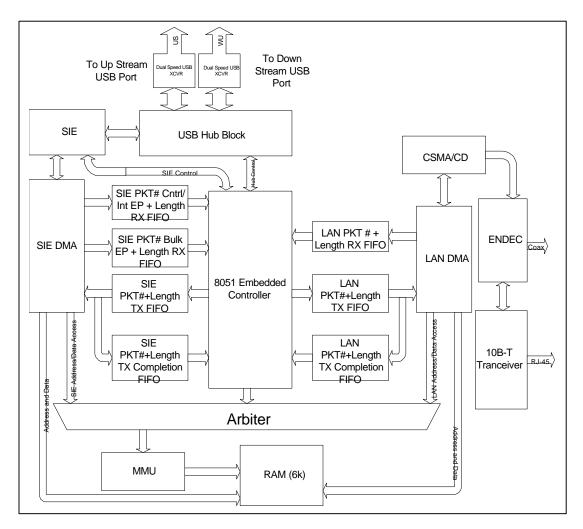

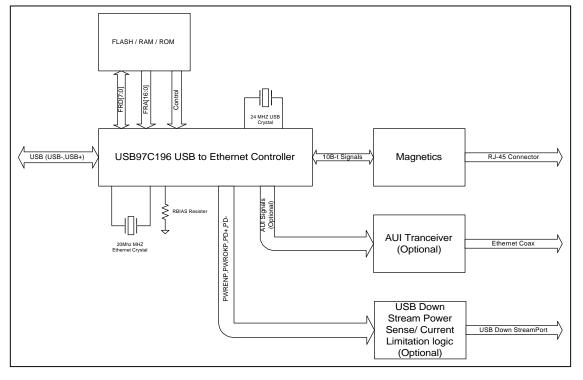

FIGURE 1 – USB97C196 BLOCK DIAGRAM

#### FUNCTIONAL DESCRIPTION

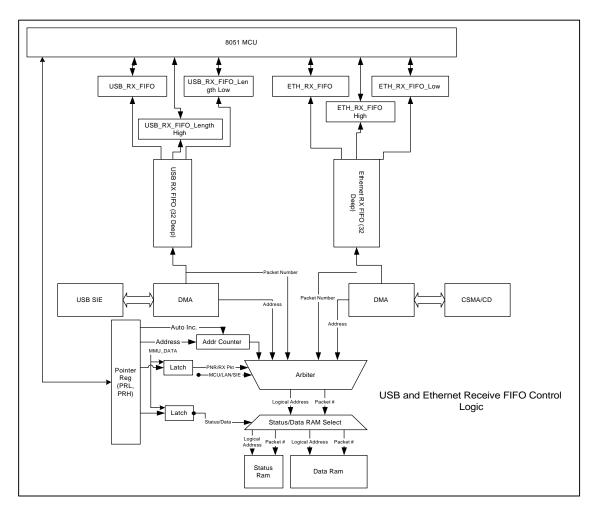

The SMSC USB97C196 incorporates a USB Serial Interface Engine (SIE), 8051 Microcontroller Unit (MCU), Serial Interface Engine DMA (SIEDMA), Ethernet EPH DMA engine and an Embedded 2 port (One Up Stream and one down stream) USB Hub. The device has 4096 bytes of internal SRAM for data stream buffering, and an MMU (Memory Management Unit) to dynamically manage buffer allocation. The semi-automatic nature of the SIEDMA, CSMA/CD engine and MMU blocks frees the MCU to provide enumeration, protocol and power management. A bus arbiter integrated into the MMU assures that transparent access between the SIEDMA, CSMA/CD, and MCU to the SRAM occurs.

#### Serial Interface Engine (SIE)

The SIE is a USB low-level protocol interpreter. The SIE controls the USB bus protocol, packet generation / extraction, parallel-to-serial / serialto-parallel conversion, CRC coding / decoding, bit stuffing, and NRZI coding / decoding.

The SIE can be dynamically configured as having any combination of five transmit, and five receive endpoints (EP2 is transmit only, and EP3 is receive only), for 1 or 2 independent addresses. The SIE can also "Receive All Addresses" for bus snooping.

#### Micro Controller Unit (MCU)

The 8051 embedded controller is a static CMOS MCU, which is fully software compatible with the industry standard Intel 80C51 micro-controller. All internal registers of the SMSC USB97C196 blocks are mapped into the external memory space of the MCU.

A detailed description of the micro-controller's internal registers and instruction set can be found in the "SMSC USB97C196 Programmer's Reference Guide".

#### SIEDMA

This is a simplified DMA engine, which automatically transfers data between SIE and SRAM via MMU control. The SIEDMA places a status block containing frame number, endpoint, and byte count to each incoming logical packet (an Ethernet packet consists of multiple USB packets) before notifying the MCU of its arrival. This block operation is transparent to the firmware.

# Memory Management Unit (MMU) Register Description

This MMU consists of a 4096 buffer RAM that consists of 32 pages of 128 bytes. Allocations can be done with up to 12 pages each (1536 bytes). The buffer can therefore concurrently hold up to 32 packets with a 64-byte payload. For isochronous pipes, it can hold 3 packets with a 1023-byte payload each, and still have room for two more 64-byte packets.

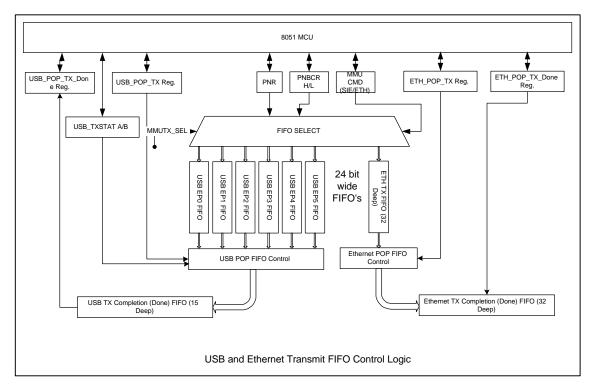

This block supports 6 independent transmit FIFO queues (one for each endpoint), and one receive queue. Each endpoint can have up to five transmit packets queued. The receive queue can accept 32 packets of any size combination before forcing the host to back off.

# Specific Support for USB Based SAR as Defined in the USB CDC Specification

This section will describe the additional Device class requirements associated with the specific features needed to implement a USB to Ethernet LAN Bridge.

# Data Transfer Management via a USB Bulk Endpoint Pair

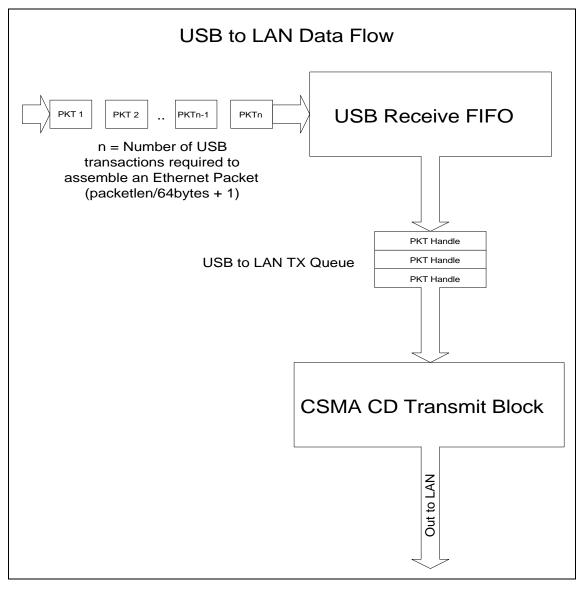

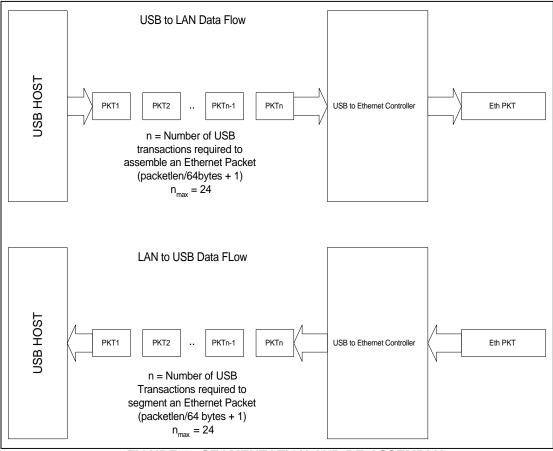

Below, shown in figures **FIGURE 2 – USB TO LAN DATA FLOW** through FIGURE 5 – SEGMENT DELINEATION, shows the data flow that would be required to implement a USB to Ethernet bridge device. If the implementation is based on the USB Communications Device Class Specification (USB CDC) that is currently under development in the USB Device Working Group, there are a number of methods that need to be implemented.

In the case of when the device is receiving a sequence of bulk transactions, the data flow shown in **FIGURE 2 – USB TO LAN DATA FLOW**, is depicted below. A set of receive FIFO's is required to store the sequence of

USB packets/transactions and upon completion, queue this buffer onto the USB RX FIFO to allow the embedded 8051 to eventually queue to send over the Ethernet LAN. The requirements for a device of this class as defined in the USB Device class specification are:

- 1. All USB transactions are received in order

- 2. The bulk endpoint pipe will only receive out bulk data transactions for data that will be sent over Ethernet.

- 1. If bulk packets / transactions are not transmitted successfully by the host, the host will retry or eventually clear the endpoint to reset the false condition.

- If the MMU runs out of memory while the USB bulk endpoint is receiving, ALL USB Bulk packets will be de-allocated (Lost).

FIGURE 2 – USB TO LAN DATA FLOW

USB-based Networking devices will use BULK transfers (Isochronous is also possible) to exchange data between a host and the USB device.

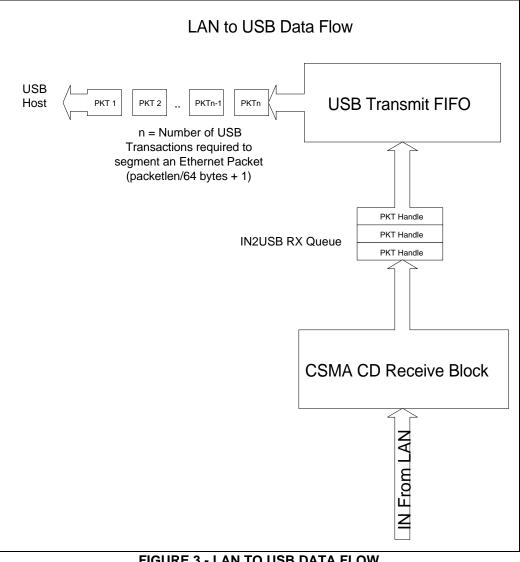

The Ethernet connection between the host computer and the Ethernet media will be "tunneled" through the USB channel. To do this, the host must formulate an Ethernet packet and provide it to a driver. The driver must then segment the Ethernet packet into multiple USB packets for transport via the USB bus. The USB receive SIE block in conjunction with the SIE DMA engine and MMU must assemble the Ethernet packet and send it out onto the LAN. When an Ethernet packet from the LAN arrives at the device it must be segmented into multiple USB packets by the device for transport over the USB to the host. The driver executing on the host must then reconstruct the original Ethernet packet from these fragments.

Both the driver and the device must be capable of segmenting Ethernet packets into USB packets as well as re-combining USB packets into Ethernet packets.

### Assembly of Multiple USB Bulk Packets into an Ethernet Frame

FIGURE 4 - SEGMENTATION AND RE-ASSEMBLY

Ethernet frames are sent from the host to the USB97C196 in 64 byte bulk packets over USB. See the diagram above. The USB97C196 will recognize / decode the start and ending of a logical Ethernet Packet by receiving an out USB packet that is less than 64 bytes or Zero (0) length in the case of the Ethernet packet being an exact multiple of 64 bytes.

Once the USB97C196 is synchronized, it must allocate sufficient memory to buffer the USB packets while the full Ethernet frame is reconstructed. Two possible techniques are: In the case that insufficient memory exists to reconstruct the complete Ethernet frame, the USB97C196 will employ flow control to restrict the host, or ignore the packet and stall the end point, causing the host to re-try.

Otherwise, the USB97C196 will continue accumulating USB bulk packets until the end of frame is detected. There are at least two methods for detecting the end of the frame.

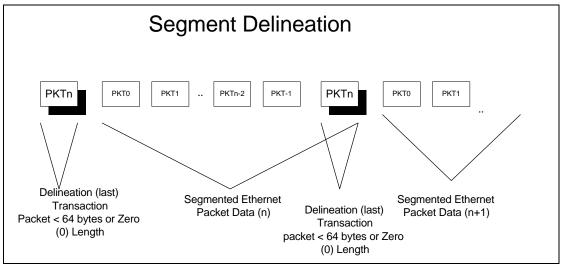

#### Segmentation of an Ethernet Frame into Multiple USB Bulk Packets

The Diagram below shows the method the USB97C196 USB to Ethernet Bridge controller determines the start and end of the Logical Ethernet packet as it is being transmitted over USB via a Bulk OUT or IN end point.

**FIGURE 5 – SEGMENT DELINEATION**

#### **Ethernet Packet Reception**

Ethernet frames being received from the LAN must be buffered. The received Ethernet packet is then segmented into USB packets as described above, and transported to the host via USB. The device detects the arrival of an inbound Ethernet frame and receives it into a buffer. The contents of that buffer are delivered on demand over the USB to the host via a bulk IN endpoint.

The MMU of the device is "multiplexed" such that it can be read or written too by an Ethernet frame buffer, or a USB packet buffer chain. Since buffer sizes are different for USB and Ethernet and some control and status information needs to be embedded into each memory buffer, an additional Status Queue is defined to store envelope encapsulation information.

#### **APPLICATIONS**

The USB97C196 allows the designer to implement a connectivity solution based on the USB data model from/to the standard 802.x Ethernet data flow medium. This USB97C196 allows a designer the ability to

utilize an embedded USB Hub to allow an additional USB port. This allows the "Use one – Get one back" paradigm, allowing the user the ability to gain an Ethernet connection while retaining the current USB port.

#### **TYPICAL SYSTEM IMPLEMENTATION**

This section will describe the requirements relating to the USB Communications device class specification relating to how Endpoint resources will be allocated. The next section titled "Specific Support for USB Based SAR as Defined in the USB CDC Specification" on page 24.

The Data-In/Data-Out pipe mechanism is the same for all networking device models supported by the CDC specification. It is independent of the media type (e.g., Cable, xDSL, Ethernet) or media data type (e.g. Ethernet frames). Typical USB-based Networking devices will support bulk transfers as the default configuration to exchange data between a host and the USB device. While each data packet of a bulk endpoint is limited to the maximum packet size defined in the associated endpoint descriptor, it should be noted that a host might request multiple bulk USB protocol packets within a single USB frame. The USB97C196 will support this requirement. For maximum throughput, a Networking device must be prepared to transfer multiple bulk packets within a single USB frame. Some USB-based Networking device implementations mav support isochronous data transfers in addition to (or instead of) bulk transfers as in the USB97C196. Isochronous transfers guarantee data throughput and bounded latency, consistent with the needs of real-time streams. Isochronous data errors are reported to receiver, but no data integrity (i.e., retransmission) is provided by the USB link. The Data Class Interface Descriptor protocol code for all Networking Control Models is 00h.

USB provides no inherent flow control mechanism for isochronous pipes, and the CDC specification defines no higher level mechanism for doing so. Instead, it is assumed that the host software is responsible for doing traffic shaping as necessary to match any end-to-end negotiation. If the networking device is

performing traffic shaping, then either a bulk endpoint should be used, or the flow control methods should be provided using vendorspecific methods. The Data Class interface of a networking device shall have a minimum of two interface settings. The first setting (the default interface setting) includes no endpoints and therefore no networking traffic is exchanged whenever the default interface setting is selected. One or more additional interface settings are used for normal operation, and therefore each includes a pair of endpoints (one IN, and one OUT) to exchange network traffic. The Firmware will select an alternate interface setting to initialize the network aspects of the device and to enable the exchange of network traffic. To recover the network aspects of a device to known states, select the default interface setting (with no endpoints) and then select the appropriate alternate interface setting. This action will flush device buffers, clear any filters or statistics counters and will cause NETWORK CONNECTION and CONNECTION\_SPEED\_CHANGE notifications to be sent to the host.

As stated previously for almost any type of USB attached networking device, a mechanism is needed where both the networking device and the Host can delineate the beginning and ending of a segment within the data stream delivered by an endpoint pipe. This positive delineation is done using a USB short packet mechanism. When a segment spans NUSB packets, the first packet through packet N-1 shall be the maximum packet size defined for the USB endpoint. If the Nth packet is less than maximum packet size the USB transfer of this short packet will identify the end of the segment. If the Nth packet is exactly maximum packet size, it shall be followed by a zero-length packet (which is a short packet) to assure the end of segment is properly identified. When transmitting data to the networking device, it is assumed that the client of the host USB driver

takes the appropriate actions to cause a short packet to be sent to the networking device. For segments with lengths that are an even multiple of the pipe's "max packet size", the ability to write a buffer of zero length is required to generate this short packet.

The host and the attached network device must negotiate to establish the maximum segment size. The upper limit for this is usually a function of the buffering capacity of the attached device, but there may be other factors involved as well. For networking devices that exchange Ethernet frames, the size of a segment is also negotiable. Typical Ethernet frames are 1514 bytes or less in length (not including the CRC), but this could be longer (e.g., 802.1Q VLAN tagging).

The Ethernet Networking Control Model is used for exchanging Ethernet framed data between the device and host. A Communication Class interface is used to configure and manage various Ethernet functions, where an "Ethernet Networking Control Model" SubClass code is indicated in the descriptor definition of its Communication Class interface. A Data Class interface is used to exchange Ethernet encapsulated frames sent over USB. These frames shall include everything from the Ethernet destination address (DA) up to the end of the data field. The CRC checksum must not be included for either send or receive data. It is the responsibility of the device hardware to generate and check CRC as required for the specific media. Receive frames that have a bad checksum must not be forwarded to the host. This implies that the device must be able to buffer at least one complete Ethernet frame.

Although a typical USB Networking device stays in an "always connected" state, some Networking device management requests are required to properly initialize both the device and the host networking stack. There also may be occasional changes of device configuration or state, e.g., adding multicast filters.

## USB TO ETHERNET CDC DEVICE CLASS ENDPOINT ALLOCATION

The SMSC USB97C196 is a specialized Device in the sense that its USB Endpoints have specific attributes that are unique to the USB to Ethernet bridge design paradigm. The USB97C100 USB endpoints of which it has 6, are not the same. The Endpoints and their functionality is shown in on page 24. The Table describes the USB97C196 Endpoint definition and usage relative to the section above Specific Support for USB Based SAR as Defined in the USB CDC Specification as defined starting on page 13.

| USB ENDPOINT |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER       | ENDPOINT ATTRIBUTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Endpoint 0   | Control Endpoint – This Endpoint corresponds to the Standard USB Common<br>Device Class definition of the "Control Endpoint." All of the requirements of the<br>"Control Endpoint" as defined in the USB 1.1 specification must be adhered too.<br>Please refer to the USB 1.1 Revision specification for additional details                                                                                                                                                                                |

| Endpoint 1   | Interrupt Endpoint – This Endpoint is a general purpose Endpoint that conforms to the standard protocols defined in the USB specification. Bulk, Isochronous and Interrupt options are available. This Endpoint however will be initialized as an "Interrupt Endpoint" based on the CDC Ethernet implementation standard. It is to the description of the Firmware Driver developer if the Endpoint is a bi-directional or single direction interrupt Endpoint.                                             |

| Endpoint 2   | CDC Compliant IN SAR (Segmentation and Re-assembly) Endpoint – This<br>Endpoint corresponds to the Host to USB to Ethernet Bridge LAN Bulk Data<br>Reception Pipe. This pipe is a special Pipe. The SIE adheres to the rules as<br>defined in the USB CDC Class specification relating to the rules regarding to the<br>delineation of logical Ethernet Packets as defined in the previous section tilted<br>"Specific Support for USB Based SAR as Defined in the USB CDC Specification"<br>on page 13     |

| Endpoint 3   | CDC Compliant OUT SAR (Segmentation and Re-assembly) Endpoint – This<br>Endpoint corresponds to the Host to USB to Ethernet Bridge LAN Bulk Data<br>transmission Pipe. This pipe is a special Pipe. The SIE adheres to the rules as<br>defined in the USB CDC Class specification relating to the rules regarding to the<br>delineation of logical Ethernet Packets as defined in the previous section tilted<br>"Specific Support for USB Based SAR as Defined in the USB CDC Specification"<br>on page 13 |

| Endpoint 4   | Generic USB Pipe – This Endpoint corresponds to a standard USB Pipe that has the ability to be a USB Bulk, Isochronous, Control, and Interrupt Pipe. This endpoint is optional for standard CDC Compliant applications. It is available for the system developer if the requirement is need to enhance feature support.                                                                                                                                                                                     |

| Endpoint 5   | Generic USB Pipe – This Endpoint corresponds to a standard USB Pipe that has<br>the ability to be a USB Bulk, Isochronous, Control, and Interrupt Pipe. This<br>endpoint is optional for standard CDC Compliant applications. It is available for<br>the system developer if the requirement is need to enhance feature support                                                                                                                                                                             |

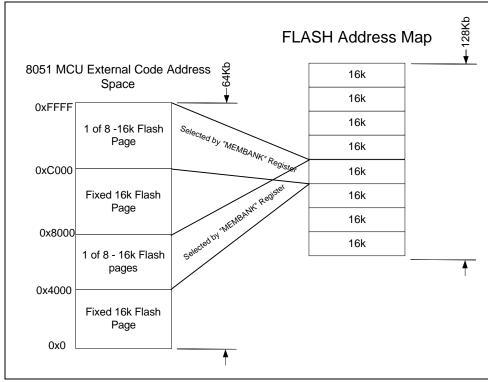

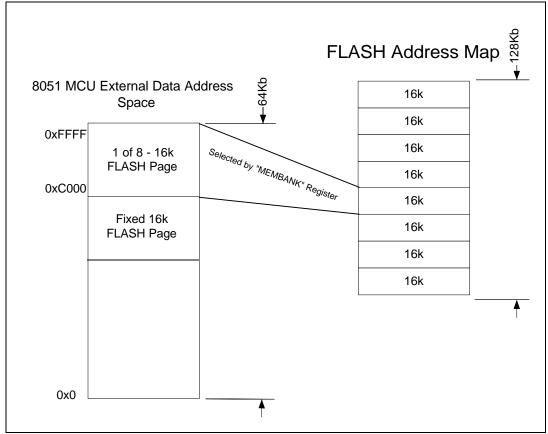

## **MCU Memory Map**

The 64K memory map is as follows from the 8051's viewpoint:

## Code Space

| Table 3 - MCU Code Memory Map |                                                      |                |  |

|-------------------------------|------------------------------------------------------|----------------|--|

| 8051 ADDRESS                  | CODE SPACE                                           | ACCESS         |  |

| 0xC000-0xFFFF                 | Movable 16k page Via MEM_BANK reg. Select            | External FLASH |  |

| 0x8000-0xBFFF                 | Fixed 16k page                                       | External FLASH |  |

|                               | 0x00000-0x03FFF FLASH                                |                |  |

| 0x4000-0x7FFF                 | Movable 16k FLASH page; 1 of 8 16k pages in External | External FLASH |  |

|                               | FLASH (0x00000-0x1FFFF) selected by MEM_BANK         | External FLASH |  |

|                               | Register Default: 0x04000-                           | External FLASH |  |

|                               | 0x07FFF FLASH Via MEM_BANK reg. Select               | External FLASH |  |

| 0x0000-0x3FFF                 | Fixed 16k FLASH Page<br>0x00000-0x03FFF FLASH        | External FLASH |  |

### Data Space

## Table 4 - MCU Data Memory Map

| 8051 ADDRESS  | DATA SPACE                                                                                                                                                                                                                  | ACCESS         |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 0xC000-0xFFFF | Movable 16k page<br>Default : 0x04000-0x07FFF FLASH<br>Select Via MEM_BANK reg.                                                                                                                                             | External FLASH |

| 0x8000-0xBFFF | Fixed 16k page<br>0x00000-0x03FFF FLASH                                                                                                                                                                                     | External FLASH |

| 0x7000-0x7FFF | 0x7FD0-0x7FEF Ethernet Register I/O Window<br>0x7F80-0x7F9F SIE Reg<br>0x7F70-0x7F7F ISA Reg<br>0x7F50-0x7F6F MMU Reg<br>0x7F20-0x7F2F Power Reg<br>0x7F10-0x7F1F Configuration Reg<br>0x7F00-0x7F0F Runtime Reg<br>Note 1. | Internal       |

| 0x6000-0x6FFF | 0x6000: MMU Data Register<br>0x6000-0x6FFF: entire MMU RAM is mapped here                                                                                                                                                   | Internal       |

| 0x5000-0x5FFF |                                                                                                                                                                                                                             | Not used       |

| 0x4000-0x4FFF |                                                                                                                                                                                                                             | Not used       |

| 0x3000-0x3FFF |                                                                                                                                                                                                                             | Not used       |

| 0x2000-0x2FFF |                                                                                                                                                                                                                             | Not used       |

| 0x0100-0x1FFF |                                                                                                                                                                                                                             | Not used       |

| 0x0000-0x00FF | Registers and SFR's                                                                                                                                                                                                         | Internal       |

Note 1: The MCU, MMU, and SIE block registers are external to the 8051, but internal to the SMSC USB97C196. These addresses will appear on the FLASH bus, but the read and write strobes will be inhibited.

#### Data Space and Code Space mappings

The diagrams shown in FIGURE 7 - MCU TO EXTERNAL CODE SPACE MAP DIAGRAM and FIGURE 8 - MCU TO EXTERNAL DATA MEMORY MAP DIAGRAM on pages 26 and 27 respectively, describe the Data Space and Code Space mappings between the External Flash and the internal 8051 MCU memory map.

FIGURE 7 - MCU TO EXTERNAL CODE SPACE MAP DIAGRAM

- Note 1: The USB97C196 presents a 17-bit address to the flash that is obtained by concatenating three bits with the lower 14 bits [13:0] of the address presented by the MCU. The three bits are Determined as follows:

- a. If the page is movable, then the upper three bits are copied from MEM\_BANK.

- b. If the page is fixed, then the upper three bits are set to zero.

The lower 14 bits [13:0] of the 16-bit MCU address represent the offset into the 16K page which is being referenced. The upper two bits [15:14] represent the page being accessed in the MCU's address space; replacing these two bits by (the larger) MEM\_BANK allows mappings to occur.

From the MCU's perspective though, it has one 64K-address space for code and one 64K-address space for data.

FIGURE 8 - MCU TO EXTERNAL DATA MEMORY MAP DIAGRAM

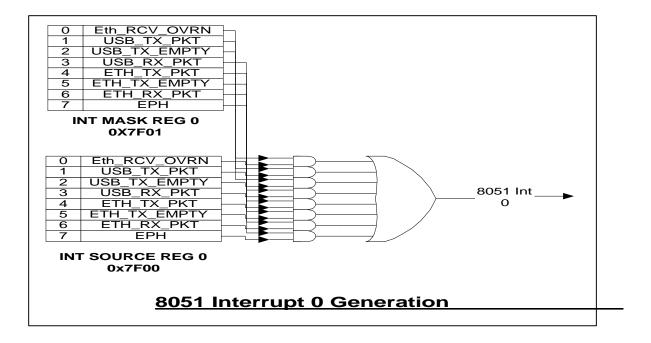

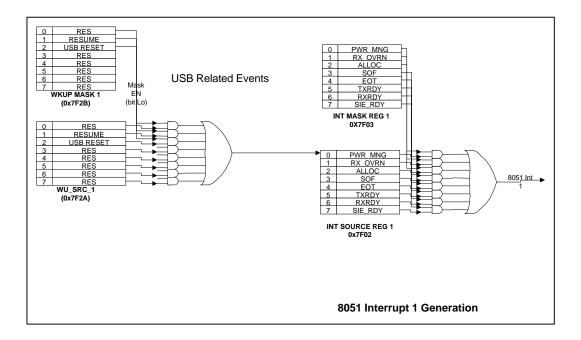

## MCU Block Register Summary

| ADDRESS                    |             |       |                                      |      |  |

|----------------------------|-------------|-------|--------------------------------------|------|--|

| (HEX)                      | NAME        | R/W   | DESCRIPTION                          | PAGE |  |

|                            | •           | RUNTI | ME REGISTERS                         | •    |  |

| 7F00                       | ISR_0       | R     | INT0 Source Register                 | 33   |  |

| 7F01                       | IMR_0       | R/W   | INT0 Mask Register                   | 36   |  |

| 7F02                       | ISR_1       | R     | INT1 Source Register                 | 37   |  |

| 7F03                       | IMR_1       | R/W   | INT1 Mask Register                   | 39   |  |

| 7F06                       | DEV_REV     | R     | Device Revision Register             | 39   |  |

| 7F07                       | DEV_ID      | R     | Device ID Register                   | 39   |  |

|                            |             | UTILI | TY REGISTERS                         |      |  |

| 7F18                       | GPIOA_DIR   | R/W   | GPIO Configuration Register          | 40   |  |

| 7F19                       | GPIOA_OUT   | R/W   | GPIO Data Output Register            | 41   |  |

| 7F1A                       | GPIOA_IN    | R     | GPIO Data Input Register             | 41   |  |

| 7F1B                       | UTIL_CONFIG | R/W   | Miscellaneous Configuration Register | 42   |  |

| POWER MANAGEMENT REGISTERS |             |       |                                      |      |  |

| 7F27                       | CLOCK_SEL   | R/W   | 8051 Clock Select Register           | 46   |  |

| 7F29                       | MEM_BANK    | R/W   | Flash Bank Select                    | 46   |  |

| 7F2A                       | WU_SRC_1    | R     | Wakeup Source                        | 47   |  |

| 7F2B                       | WU_MSK_1    | R/W   | Wakeup Mask                          | 47   |  |

| 7F2C                       | Reserved    | R     | Reserved                             |      |  |

| 7F2D                       | Reserved    | R     | Reserved                             |      |  |

| MCU TEST REGISTERS         |             |       |                                      |      |  |

| 7F7D                       | MCU_TEST3   | N/A   | Reserved for Test                    |      |  |

| 7F7E                       | MCU_TEST2   | N/A   | Reserved for Test                    |      |  |

| 7F7F                       | MCU_TEST1   | N/A   | Reserved for Test                    |      |  |

## Table 5 - MCU Block Register Summary

## MMU Block Register Summary

| ADDRESS       |                  |          |                                         |      |  |  |  |

|---------------|------------------|----------|-----------------------------------------|------|--|--|--|

| (HEX)         | NAME             | R/W      | DESCRIPTION                             | PAGE |  |  |  |

| MMU REGISTERS |                  |          |                                         |      |  |  |  |

| 6000          | MMU_DATA         | R/W      | 8051-MMU Data Window                    | 59   |  |  |  |

|               |                  |          | Register FIFO                           |      |  |  |  |

| 7F50          | PRL              | R/W      | 8051-MMU Pointer Register               | 60   |  |  |  |

|               |                  |          | (Low)                                   |      |  |  |  |

| 7F51          | PRH              | R/W      | 8051-MMU Pointer Register               | 60   |  |  |  |

|               |                  |          | (High) & R/W                            |      |  |  |  |

| 7F52          | MMUTX_SEL        | R/W      | 8051-MMU TX FIFO Select for             | 61   |  |  |  |

|               |                  |          | Commands                                |      |  |  |  |

| 7F53          | MMUCR            | W        | 8051-MMU Command Register               | 62   |  |  |  |

| 7F54          | ARR              | R        | 8051-MMU Allocation Result              | 65   |  |  |  |

|               |                  |          | Register                                |      |  |  |  |

| 7F55          | PNR              | R/W      | 8051-MMU Packet Number                  | 66   |  |  |  |

|               |                  | _        | Register                                |      |  |  |  |

| 7F56          | MIR              | R        | MEMORY INFORMATION                      | 71   |  |  |  |

| 7557          |                  | DAA      | REGISTER                                | 70   |  |  |  |

| 7F57          | TX/RX_MGMT       | R/W      | USB TX/RX Management                    | 76   |  |  |  |

| 7550          |                  | <b>_</b> | Register 1<br>USB Receive Packet Number | 72   |  |  |  |

| 7F58          | USB_RX_FIFO      | R        | FIFO Register                           | 72   |  |  |  |

| 7F59          | USB_RX_FIFO_     | R        | USB Receive FIFO Packet                 | 72   |  |  |  |

| 7539          | Length_Low       | ĸ        | Length Register Low                     | 12   |  |  |  |

| 7F5A          | USB RX FIFO      | R        | USB Receive FIFO Packet                 | 72   |  |  |  |

| 110/1         | Length_High      |          | Length Register High                    | 12   |  |  |  |

| 7F5B          | Ethernet_RX_FIFO | R        | ETHERNET Receive Packet                 | 73   |  |  |  |

| 1100          |                  |          | Number FIFO Register                    | 10   |  |  |  |

| R             | RX_FIFO_Length_  |          | ETHERNET Receive FIFO                   | 73   |  |  |  |

|               | Low              |          | Packet Length Register Low              | _    |  |  |  |

| 7F5D          | RX_FIFO_Length_  | R        | ETHERNET Receive FIFO                   | 73   |  |  |  |

|               | High             |          | Packet Length Register High             |      |  |  |  |

| 7F60          | USB_TXSTAT_A     | R/W      | USB TRANSMIT FIFO STATUS                | 74   |  |  |  |

|               |                  |          | REGISTER A                              |      |  |  |  |

| 7F61          | USB_TXSTAT_B     | R/W      | TRANSMIT FIFO STATUS                    | 75   |  |  |  |

|               |                  |          | REGISTER B                              |      |  |  |  |

| 7F62          | PNBCRL           | R/W      | PACKET NUMBER Byte Count                | 66   |  |  |  |

|               |                  |          | REGISTER Low                            |      |  |  |  |

| 7F63          | PNBCRH           | R/W      | PACKET NUMBER Byte Count                | 66   |  |  |  |

|               |                  |          | REGISTER High                           |      |  |  |  |

| 7F64          | USB_POP_TX       | R        | USB POP TX FIFO                         | 69   |  |  |  |

| ADDRESS<br>(HEX) | NAME                | R/W | DESCRIPTION                                 | PAGE |

|------------------|---------------------|-----|---------------------------------------------|------|

| 7F65             | USB_POP_TX_Don<br>e | R   | USB POP TX FIFO Done                        | 70   |

| 7F66             | ETH_TX              | R   | Ethernet TX FIFO                            | 70   |

| 7F67             | Eth_POP_TX_DON<br>E | R   | Ethernet POP Transmit FIFO<br>Done Register | 71   |

| 7F6C             | PNCRH               | R/W | Conversion Byte Count<br>REGISTER Low       | 68   |

| 7F6D             | PNCRL               | R/W | Conversion Byte Count<br>REGISTER High      | 68   |

| 7F6E             | MMU_TESTx           | N/A | Reserved for Test                           |      |

| 7F6F             | MMU_TESTx           | N/A | Reserved for Test                           |      |

## SIE Block Register Summary

| ADDRESS                     |                       |     |                              |      |  |  |  |

|-----------------------------|-----------------------|-----|------------------------------|------|--|--|--|

| (HEX)                       | NAME                  | R/W | DESCRIPTION                  | PAGE |  |  |  |

| SIE Control Registers       |                       |     |                              |      |  |  |  |

| 7F80                        | EP_CTRL0              | R/W | Endpoint 0 Control Register  | 82   |  |  |  |

| 7F81                        | EP_CTRL1              | R/W | Endpoint 1 Control Register  | 82   |  |  |  |

| 7F82                        | EP_CTRL2              | R/W | Endpoint 2 Control Register  | 82   |  |  |  |

| 7F83                        | EP_CTRL3              | R/W | Endpoint 3 Control Register  | 82   |  |  |  |

| 7F84                        | EP_CTRL4              | R/W | Endpoint 4 Control Register  | 82   |  |  |  |

| 7F85                        | EP_CTRL5              | R/W | Endpoint 5 Control Register  | 82   |  |  |  |

| 7F86-7F8F                   | RESERVED              | R   | RESERVED                     |      |  |  |  |

| 7F90                        | FRAMEL                | R   | USB Frame Count Low          | 87   |  |  |  |

| 7F91                        | FRAMEH                | R   | USB Frame Count High         | 87   |  |  |  |

| 7F92                        | SIE_ADDR              | R/W | USB Local Address Register   | 87   |  |  |  |

| 7F93                        | SIE_STAT              | R   | SIE Status Register          | 88   |  |  |  |

| 7F94                        | SIE_CTRL              | R/W | SIE Control Register         | 89   |  |  |  |

| 7F95                        | SIE_TST1              | R/W | Reserved Test Register       |      |  |  |  |

| 7F96                        | SIE_TST2              | R/W | Reserved Test Register       |      |  |  |  |

| 7F97                        | SIE_EP_TEST           | R/W | Reserved Test Register       |      |  |  |  |

| 7F98                        | SIE_CONFIG 1          | R/W | SIE Configuration Register 1 | 90   |  |  |  |

| 7F99                        | ALT_ADDR              | R/W | Secondary Local Address      | 88   |  |  |  |

|                             |                       |     | Register                     |      |  |  |  |

| 7F9A                        | SIE_TST               | R/W | Reserved Test Register       |      |  |  |  |

| 7F9B                        | SIE_TST               | R/W | Reserved Test Register       |      |  |  |  |

| 7F9C                        | SIE_TST               | R/W | Reserved Test Register       |      |  |  |  |

| 7F9D                        | SIE_TST               | R/W | Reserved Test Register       |      |  |  |  |

| 7F9E                        | ALT_ADDR2             | R/W | Reserved                     |      |  |  |  |

| 7F9F                        | ALT_ADDR3             | R/W | Reserved                     |      |  |  |  |

| 7FA9                        | SIE_CTRL2             | R/W | SIE Control Register 2       | 89   |  |  |  |

| 7FAA                        | EPCMD                 | W   | Endpoint Command Register    | 85   |  |  |  |

| 7FAC                        | NONCTRL_EP            | R/W | NonControl Endpoint Register | 84   |  |  |  |

| HUB BLOCK CONTROL REGISTERS |                       |     |                              |      |  |  |  |

| 7FA0                        | IdVendor-Low Byte     | R/W | Low byte Vendor ID           | 94   |  |  |  |

| 7FA1                        | IdVendor-High Byte    | R/W | High byte Vendor ID          | 94   |  |  |  |

| 7FA2                        | IdProduct-Low Byte    | R/W | Low byte Product ID          | 94   |  |  |  |

| 7FA3                        | IdProduct-High Byte   | R/W | High byte Product ID         | 94   |  |  |  |

| 7FA4                        | BcdDevice - Low Byte  | R/W | USB device release number    | 94   |  |  |  |

| 7FA5                        | BcdDevice - High Byte | R/W | USB device release number    | 94   |  |  |  |

| 7FA6                        | HubControl1           | R/W | Hub Control Register 1       | 95   |  |  |  |

| 7FA7                        | HubControl2           | R/W | Hub Control Register 2       | 96   |  |  |  |

## Table 7 - SIE Block Register Summary

## EPH (Ethernet) Block Register Summary

| ADDRESS |           |            |                                     |      |

|---------|-----------|------------|-------------------------------------|------|

| (HEX)   | NAME      | R/W        | DESCRIPTION                         | PAGE |

|         |           | Ethernet C | Control Registers                   |      |

| 7FD0    | ETCR1     | R/W        | Ethernet Transmit Control Register1 | 48   |

| 7FD1    | ETCR2     | R/W        | Ethernet Transmit Control Register2 | 48   |

| 7FD2    | EPH1      | R/W        | EPH STATUS REGISTER1                | 49   |

| 7FD3    | EPH2      | R/W        | EPH STATUS REGISTER2                | 50   |

| 7FD4    | RCR1      | R/W        | Ethernet Receive Control Register 1 | 51   |

| 7FD5    | RCR2      | R/W        | Ethernet Receive Control Register 2 | 52   |

| 7FD6    | ECR1      | R          | Ethernet counter Register 1         | 53   |

| 7FD7    | ECR2      | R          | Ethernet counter Register 2         | 53   |

| 7FD8    | EconfigR1 | R/W        | Ethernet CONFIGURATION REGISTER     | 54   |

| 7FD9    | EconfigR2 | R/W        | Ethernet CONFIGURATION REGISTER     | 55   |

| 7FDA    | IAR0      | R/W        | INDIVIDUAL ADDRESS REGISTER 0       | 55   |

| 7FDB    | IAR1      | R/W        | INDIVIDUAL ADDRESS REGISTER 1       | 55   |

| 7FDC    | IAR2      | R/W        | INDIVIDUAL ADDRESS REGISTER 2       | 56   |

| 7FDD    | IAR3      | R/W        | INDIVIDUAL ADDRESS REGISTER 3       | 56   |

| 7FDE    | IAR4      | R/W        | INDIVIDUAL ADDRESS REGISTER 4       | 56   |

| 7FDF    | IAR5      | R/W        | INDIVIDUAL ADDRESS REGISTER 5       | 56   |

| 7FE0    | MCT0      | R/W        | Multicast Table Register 0          | 56   |

| 7FE1    | MCT1      | R/W        | Multicast Table Register 1          | 56   |