### 8x931AA, 8x931HA Universal Serial Bus Peripheral Controller User's Manual

September 1997

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect IL 60056-764

or call 1-800-879-4683

Copyright © Intel Corporation 1997. Third-party brands and names are the property of their respective owners

### CONTENTS

#### **CHAPTER 1 GUIDE TO THIS MANUAL** 1.1 NOTATIONAL CONVENTIONS AND TERMINOLOGY ...... 1-3 1.2 RELATED DOCUMENTS ...... 1-6 1.3 Data Sheet ......1-6 1.3.1 Application Notes ......1-6 1.3.2 1.4 141 1.4.2 FaxBack Service ......1-7 Bulletin Board System (BBS) ......1-8 1.4.3

#### **CHAPTER 2**

#### ARCHITECTURAL OVERVIEW

| 2.1   | PRODUCT OVERVIEW                          | 2-2  |

|-------|-------------------------------------------|------|

| 2.1.1 | 8x931AA Features                          | 2-3  |

| 2.1.2 | 8x931HA Features                          | 2-3  |

| 2.1.3 | Keyboard Control Interface                | 2-4  |

| 2.1.4 | MCS <sup>®</sup> 51 Architecture Features | 2-5  |

| 2.2   | MICROCONTROLLER CORE                      | 2-6  |

| 2.2.1 | CPU                                       | 2-6  |

| 2.2.2 | Clock and Reset Unit                      |      |

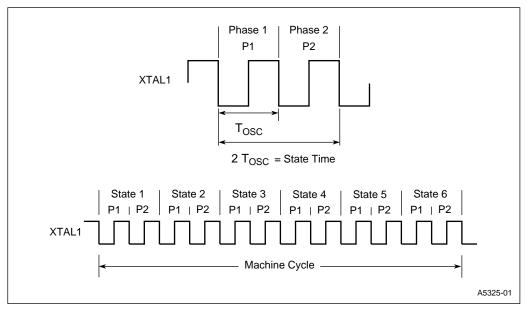

| 2.2.  | 2.1 State Time and Machine Cycles         | 2-8  |

| 2.2.  | 2.2 USB Operating Rate                    | 2-8  |

| 2.2.  |                                           | -    |

| 2.2.  |                                           |      |

| 2.2.3 | Interrupt Handler                         | 2-11 |

| 2.3   | 8x931 MEMORY                              | 2-11 |

| 2.4   | UNIVERSAL SERIAL BUS MODULE               | 2-11 |

| 2.4.1 | USB Operation                             | 2-12 |

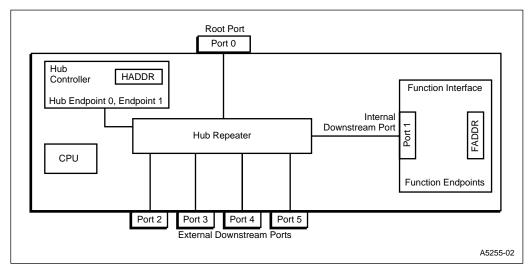

| 2.4.2 | Hub Interface                             | 2-13 |

| 2.4.3 | Hub Repeater                              | 2-13 |

| 2.4.4 | Serial Bus Interface Engine (SIE)         | 2-13 |

| 2.4.5 | Hub Interface Unit (HIU)                  | 2-13 |

| 2.4.6 | Hub FIFOs                                 | 2-13 |

| 2.5   | ON-CHIP PERIPHERALS                       | 2-14 |

| 2.5.1 | Timer/Counters                            | 2-14 |

| 2.5.2 | Serial I/O Port                           |      |

| 2.6   | OPERATING CONDITIONS                      | 2-14 |

####

#### **PROGRAMMING CONSIDERATIONS**

| 2 | 4.1 TH  | HE MCS <sup>®</sup> 51 INSTRUCTION SET | 4-1  |

|---|---------|----------------------------------------|------|

|   | 4.1.1   | Program Status Word                    |      |

|   | 4.1.2   | Addressing Modes                       |      |

|   | 4.1.2.1 |                                        | 4-3  |

|   | 4.1.2.2 | INDIRECT ADDRESSING                    | 4-3  |

|   | 4.1.2.3 |                                        |      |

|   | 4.1.2.4 |                                        |      |

|   | 4.1.2.5 | MMEDIATE CONSTANTS                     | 4-4  |

|   | 4.1.2.6 |                                        |      |

|   | 4.1.3   | Arithmetic Instructions                | 4-5  |

|   | 4.1.4   | Logical Instructions                   | 4-7  |

|   | 4.1.5   | Data Transfers                         | 4-8  |

|   | 4.1.5.1 | Internal RAM                           | 4-8  |

|   | 4.1.5.2 | 2 External RAM                         | 4-10 |

|   | 4.1.5.3 | Lookup Tables                          | 4-11 |

|   | 4.1.6   | Boolean Instructions                   |      |

|   | 4.1.6.1 | Relative Offset                        | 4-13 |

|   | 4.1.7   | Jump Instructions                      | 4-14 |

|   |         |                                        |      |

#### CHAPTER 5

#### INTERRUPT SYSTEM

| 5.1   | OVERVIEW                            | 5-1  |

|-------|-------------------------------------|------|

| 5.2   | INTERRUPT SOURCES                   |      |

| 5.2.1 | External Interrupts                 | 5-6  |

| 5.2.2 | Timer Interrupts                    |      |

| 5.2.3 | Keyboard Scan Interrupt             | 5-7  |

| 5.2.4 | Serial Port Interrupt               | 5-8  |

| 5.2.5 | USB Function Interrupt              | 5-8  |

| 5.2.6 | USB Start-of-frame Interrupt        | 5-11 |

| 5.2.7 | USB Hub Interrupt                   | 5-15 |

| 5.2.8 | USB Global Suspend/Resume Interrupt |      |

| 5.2.  |                                     | 5-17 |

| 5.2.  | 8.2 Global Resume                   | 5-17 |

| 5.2.  | 8.3 USB Remote Wake-up              | 5-17 |

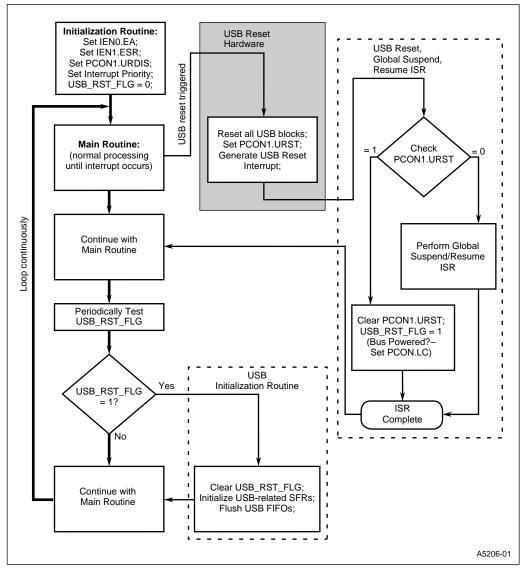

| 5.2.9 | USB Reset Separation                | 5-17 |

#### CONTENTS

### intel

| 5.2. | 9.1  | Initialization Required for USB Reset | 5-18 |

|------|------|---------------------------------------|------|

|      |      | USB Reset Hardware Operations         |      |

|      |      | USB Reset ISR                         |      |

| 5.2. | 9.4  | Main Routine Considerations           | 5-22 |

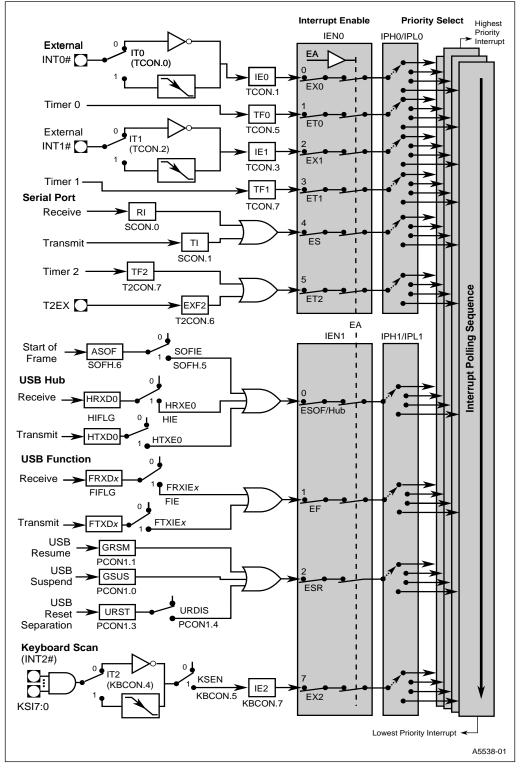

| 5.3  | INTE | RRUPT ENABLE                          | 5-24 |

| 5.4  | INTE | RRUPT PRIORITIES                      | 5-26 |

| 5.5  | INTE | RRUPT HANDLING                        | 5-30 |

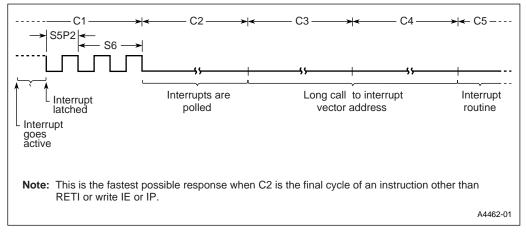

| 5.6  | RESF | PONSE TIME                            | 5-32 |

|      |      |                                       |      |

#### CHAPTER 6

#### **USB FUNCTION**

| 6.1   | FUNCTION INTERFACE                              | 6-1  |

|-------|-------------------------------------------------|------|

| 6.1.1 | Function Endpoint Pairs                         | 6-1  |

| 6.1.2 | Function FIFOs                                  | 6-1  |

| 6.1.3 |                                                 |      |

| 6.1.4 | Endpoint Selection                              | 6-5  |

| 6.2   | USB FUNCTION SFRS                               | 6-7  |

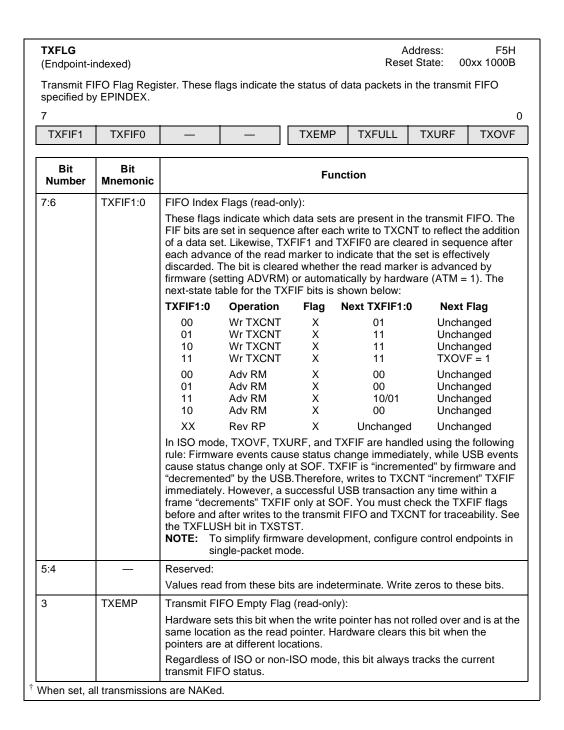

| 6.3   | TRANSMIT FIFOS                                  | 6-14 |

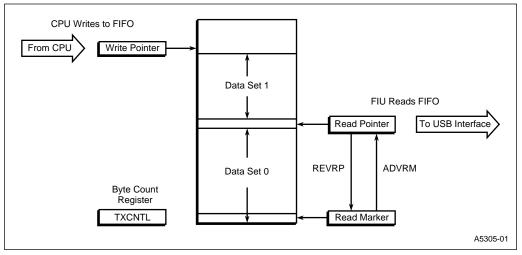

| 6.3.1 | Transmit FIFO Registers                         | 6-15 |

| 6.3.2 | Transmit FIFO Data Register (TXDAT)             | 6-16 |

| 6.3.3 | Transmit FIFO Byte Count Register (TXCNTL)      | 6-16 |

| 6.3.4 |                                                 |      |

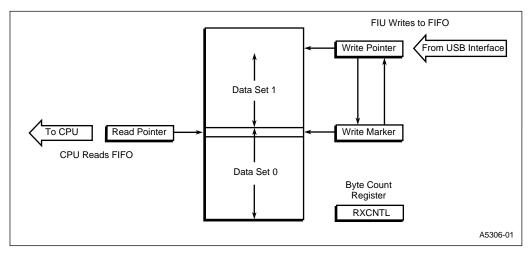

| 6.4   | RECEIVE FIFOs                                   | 6-24 |

| 6.4.1 | Receive FIFO Registers                          | 6-25 |

| 6.4.  |                                                 |      |

| 6.4.  | .1.2 Receive FIFO Byte Count Registers (RXCNTL) |      |

| 6.4.2 |                                                 |      |

| 6.5   | SIE DETAILS                                     | 6-34 |

| 6.6   | SETUP TOKEN RECEIVE FIFO HANDLING               | 6-34 |

| 6.7   | ISO DATA MANAGEMENT                             | 6-35 |

| 6.7.1 | Transmit FIFO ISO Data Management               | 6-35 |

| 6.7.2 | Receive FIFO ISO Data Management                | 6-36 |

#### CHAPTER 7

| USB H | UΒ |

|-------|----|

|-------|----|

| 7.1 HUB FUNCTIONAL OVERVIEW                                               | 7-1 |

|---------------------------------------------------------------------------|-----|

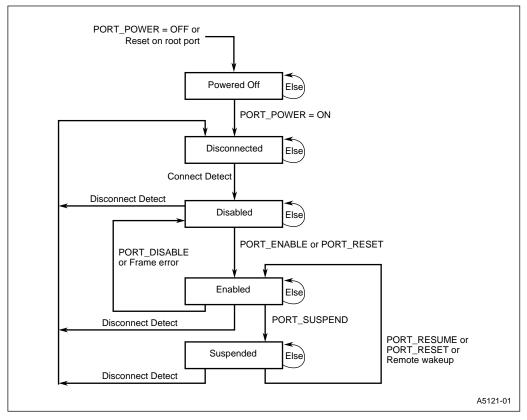

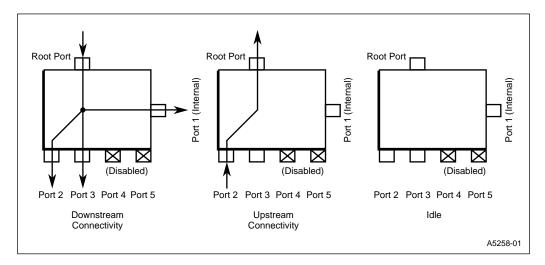

| 7.1.1 Port Connectivity States                                            |     |

| 7.1.2 Per-packet Signaling Connectivity                                   | 7-6 |

| 7.1.2.1 Connectivity to Downstream Ports Attached With Full-speed Devices | 7-6 |

| 7.1.2.2 Connectivity to Downstream Ports attached with Low-speed Devices  | 7-7 |

| 7.2 BUS ENUMERATION                                                       |     |

| 7.2.1 Hub Descriptors                                                     | 7-7 |

| 7.2.2 The Hub Address Register (HADDR)                                    | 7-8 |

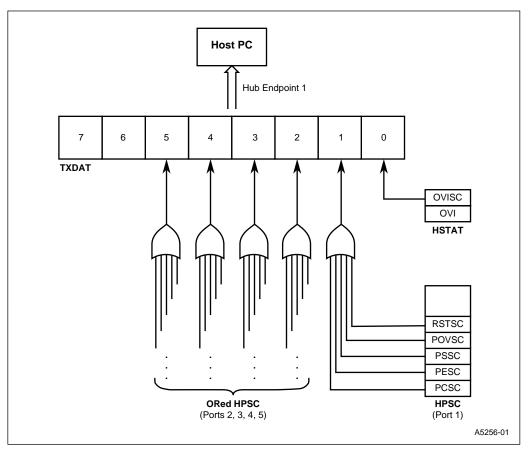

| 7.3   | HUB STATUS                                          |      |

|-------|-----------------------------------------------------|------|

| 7.4   | USB HUB ENDPOINTS                                   |      |

| 7.4.1 | Hub Endpoint Indexing Using EPINDEX                 | 7-11 |

| 7.4.2 | Hub Endpoint Control                                | 7-11 |

| 7.4.3 | Hub Endpoint Transmit and Receive Operations        | 7-12 |

| 7.5   | USB HUB PORTS                                       | 7-14 |

| 7.5.1 |                                                     |      |

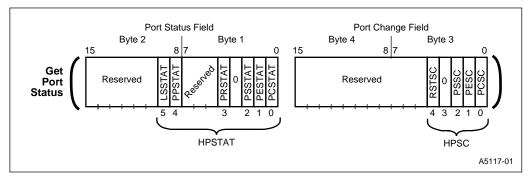

| 7.5.2 | Examining a Port's Status Using HPSTAT              | 7-17 |

| 7.5.3 | Monitoring Port Status Change Using HPSC            | 7-20 |

| 7.5.4 | Hub Port Indexing Using HPINDEX                     | 7-23 |

| 7.5.5 |                                                     |      |

| 7.5   |                                                     |      |

| 7.5   | 5.2 Embedded Function Remote Wake-up                | 7-25 |

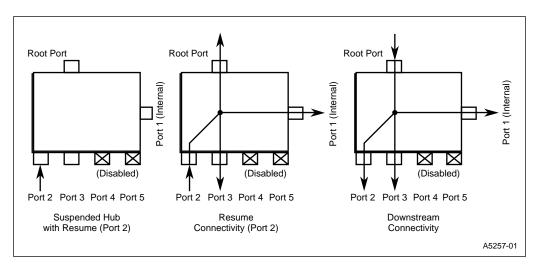

| 7.6   | SUSPEND AND RESUME                                  | 7-25 |

| 7.6.1 | Hub Global Suspend and Resume                       | 7-25 |

| 7.6.2 | Remote Connectivity                                 | 7-25 |

| 7.6   | 2.1 Resume Connectivity                             | 7-25 |

| 7.6   | 2.2 Connectivity Due to Physical Connect/Disconnect |      |

| 7.6   | 2.3 Embedded Function Suspend and Resume            | 7-26 |

| 7.7   | HUB POWER DISTRIBUTION                              | 7-27 |

| 7.7.1 | Port Power Switching                                | 7-27 |

| 7.7.2 | Overcurrent Detection                               | 7-29 |

| 7.7.3 | Ganged Power Enable                                 | 7-29 |

| 7.8   | HUB DEVICE SIGNALS                                  | 7-30 |

#### **CHAPTER 8**

#### **USB PROGRAMMING MODELS**

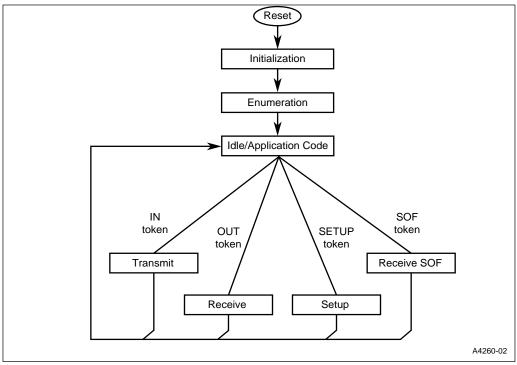

| 8.1   | OVERVIEW OF PROGRAMMING MODELS | 8-1  |

|-------|--------------------------------|------|

| 8.1.1 | Enumeration                    |      |

| 8.1.2 | Idle State                     | 8-3  |

| 8.1.3 | Transmit and Receive Routines  | 8-3  |

| 8.1.4 | USB Interrupts                 | 8-4  |

| 8.2   | TRANSMIT OPERATIONS            |      |

| 8.2.1 | Overview                       | 8-4  |

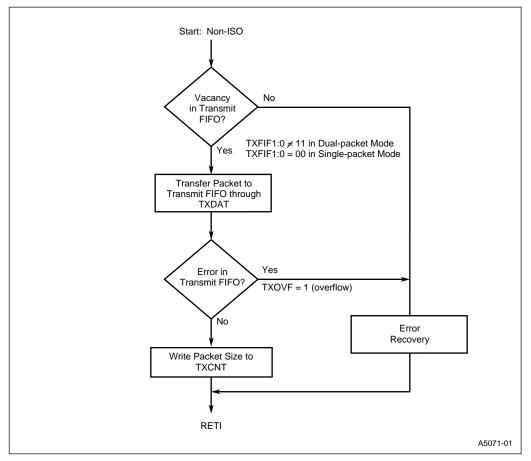

| 8.2.2 | Pre-transmit Operations        | 8-7  |

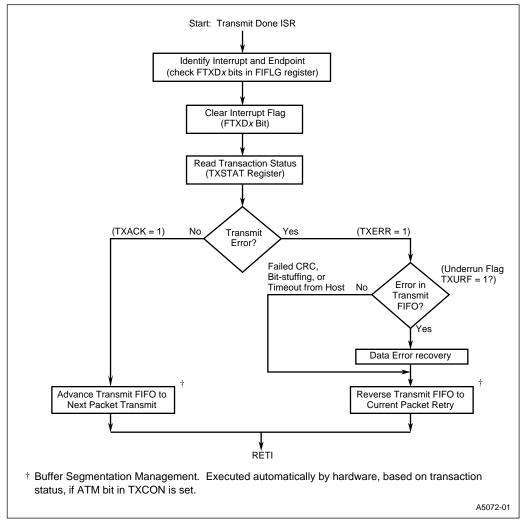

| 8.2.3 | Post-transmit Operations       | 8-8  |

| 8.3   | RECEIVE OPERATIONS             | 8-10 |

| 8.3.1 | Overview                       | 8-10 |

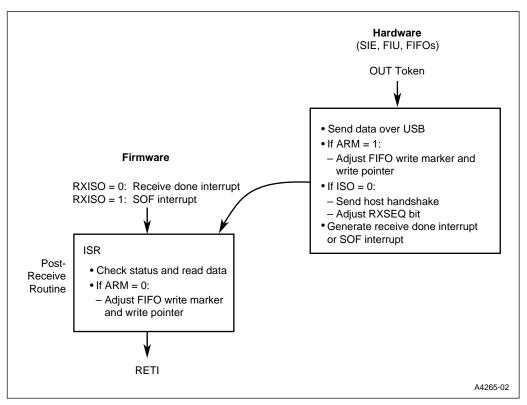

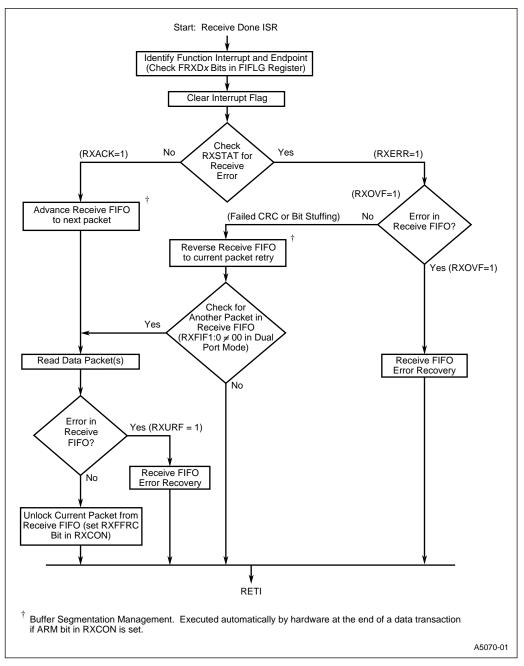

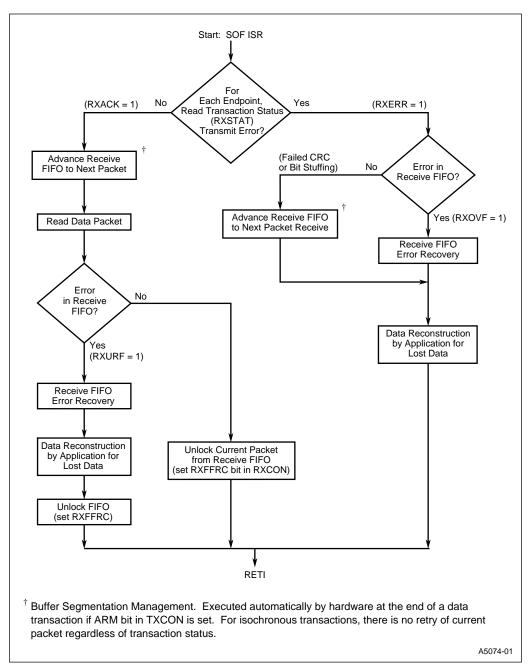

| 8.3.2 | Post-receive Operations        | 8-11 |

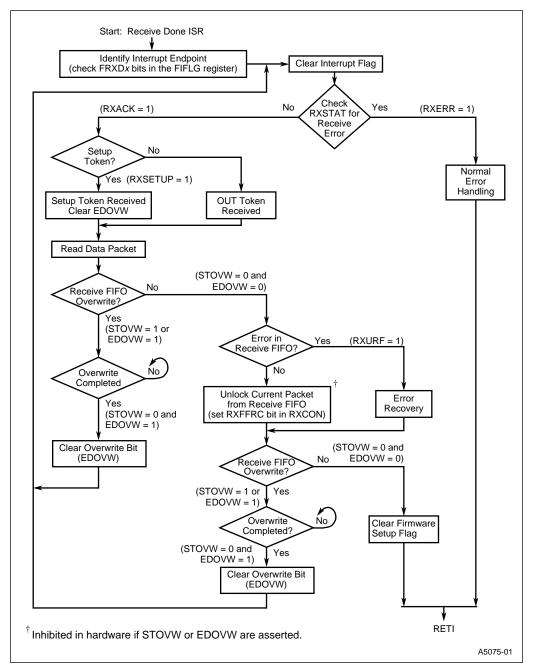

| 8.4   | SETUP TOKEN                    | 8-14 |

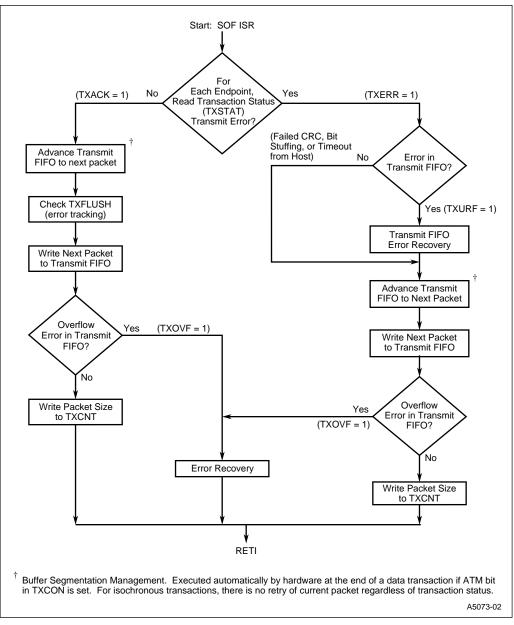

| 8.5   | START-OF-FRAME (SOF) TOKEN     | 8-16 |

| 8.6   | HUB OPERATION                  |      |

| 8.6.1 | Hub Status and Configuration   | 8-17 |

#### CONTENTS

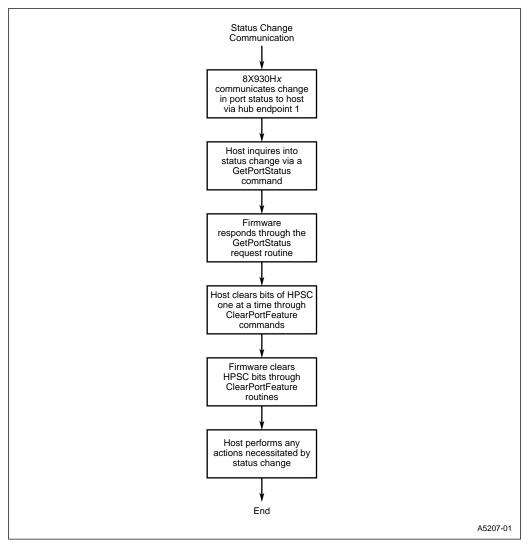

| 8.6.2 Port Status Change Communication         | 8-23 |

|------------------------------------------------|------|

| 8.6.3 Hub Firmware Examples                    | 8-24 |

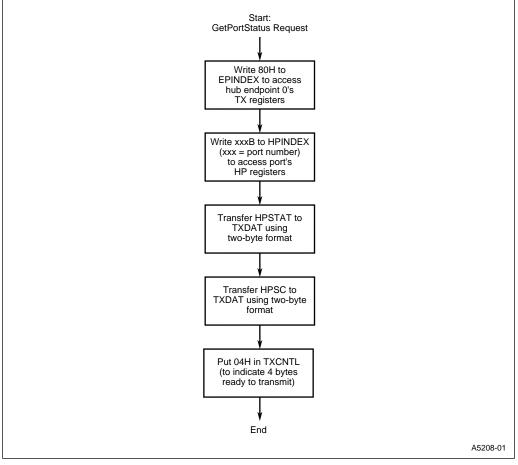

| 8.6.3.1 GetPortStatus Request Firmware         |      |

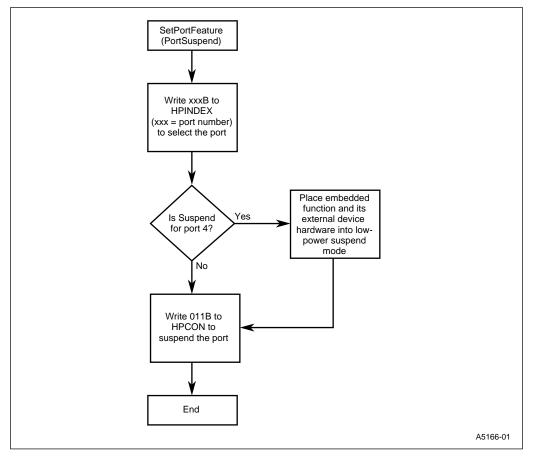

| 8.6.3.2 SetPortFeature (PORT_SUSPEND) Firmware | 8-26 |

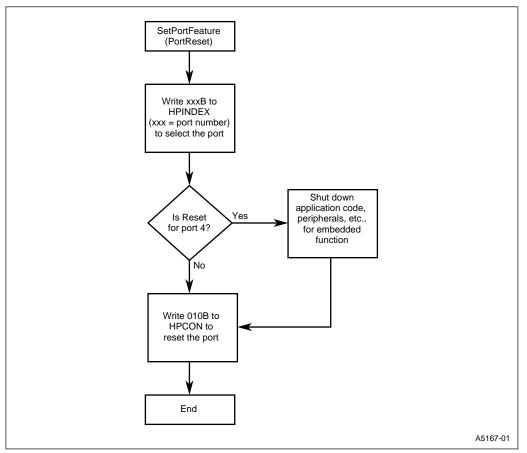

| 8.6.3.3 SetPortFeature (PORT_RESET) Firmware   | 8-27 |

#### CHAPTER 9

#### **INPUT/OUTPUT PORTS**

| 9.1 | INPUT/OUTPUT PORT OVERVIEW         | 9-1 |

|-----|------------------------------------|-----|

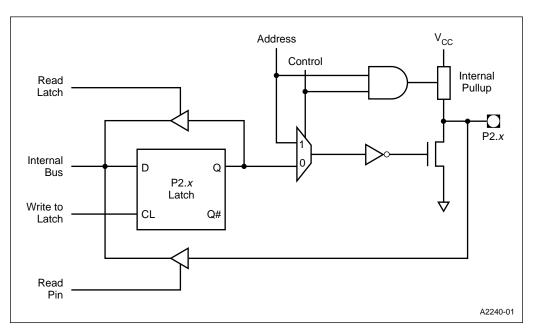

| 9.2 | I/O CONFIGURATIONS                 | 9-2 |

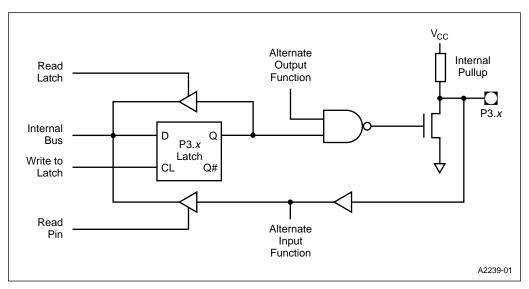

| 9.3 | PORT 1 AND PORT 3                  | 9-2 |

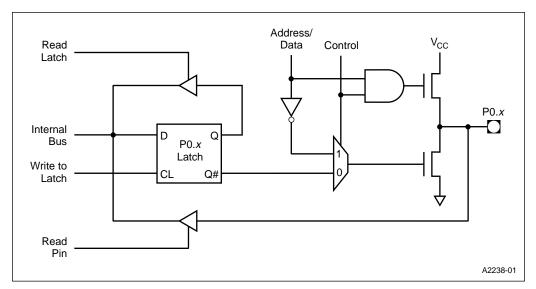

| 9.4 | PORT 0 AND PORT 2                  | 9-2 |

| 9.5 | READ-MODIFY-WRITE INSTRUCTIONS     | 9-5 |

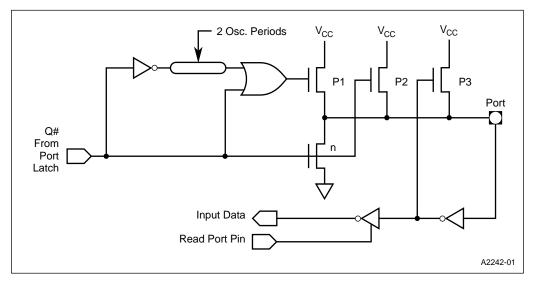

| 9.6 | QUASI-BIDIRECTIONAL PORT OPERATION | 9-6 |

| 9.7 | PORT LOADING                       | 9-7 |

| 9.8 | EXTERNAL MEMORY ACCESS             | 9-7 |

|     |                                    |     |

#### **CHAPTER 10**

#### TIMER/COUNTERS

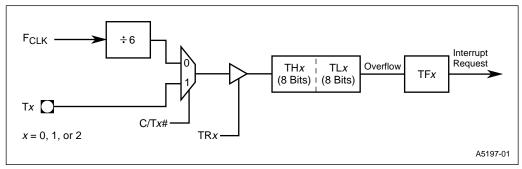

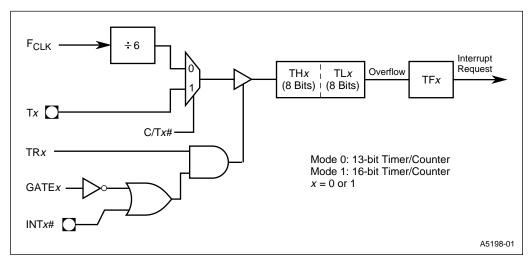

| 10.1   | TIMER/COUNTER OVERVIEW                  | 10-1  |

|--------|-----------------------------------------|-------|

| 10.2   | TIMER/COUNTER OPERATION                 | 10-1  |

| 10.3   | TIMER 0                                 | 10-4  |

| 10.3.  | 1 Mode 0 (13-bit Timer)                 | 10-4  |

| 10.3.2 |                                         |       |

| 10.3.3 | 3 Mode 2 (8-bit Timer With Auto-reload) | 10-5  |

| 10.3.4 | 4 Mode 3 (Two 8-bit Timers)             | 10-5  |

| 10.4   | TIMER 1                                 | 10-6  |

| 10.4.  |                                         |       |

| 10.4.2 |                                         |       |

| 10.4.3 | 3 Mode 2 (8-bit Timer with Auto-reload) | 10-9  |

| 10.4.4 | 4 Mode 3 (Halt)                         | 10-9  |

| 10.5   | TIMER 0/1 APPLICATIONS                  | 10-9  |

| 10.5.1 | 1 Auto-reload Setup Example             | 10-9  |

| 10.5.2 | 2 Pulse Width Measurements              | 10-10 |

| 10.6   | TIMER 2                                 | 10-10 |

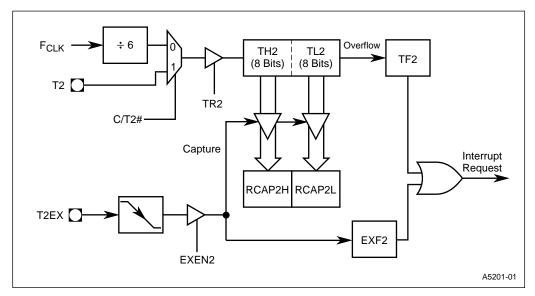

| 10.6.1 | 1 Capture Mode                          | 10-11 |

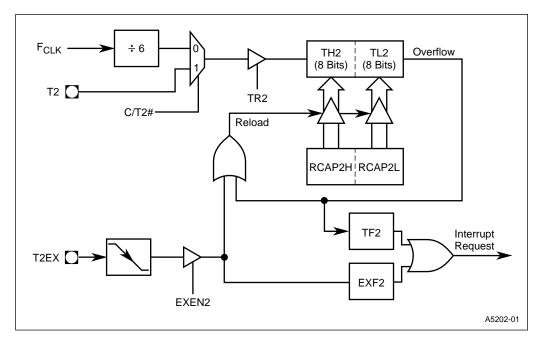

| 10.6.2 |                                         |       |

| 10.6   | 6.2.1 Up Counter Operation              |       |

| 10.6.3 | I''                                     |       |

| 10.6.4 |                                         |       |

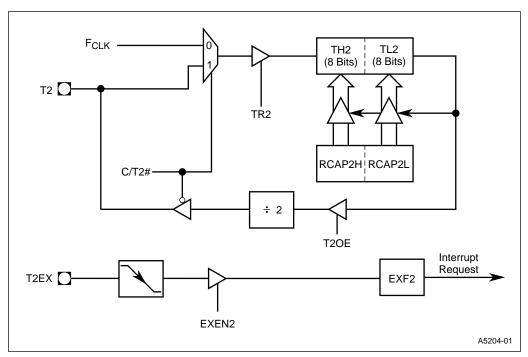

| 10.6.  | 5 Clock-out Mode                        | 10-14 |

#### CHAPTER 11 SERIAL I/O PORT

| 11.1   |      |                                              | 11 1  |

|--------|------|----------------------------------------------|-------|

|        |      | RVIEW                                        |       |

| 11.2   | MOD  | ES OF OPERATION                              | 11-2  |

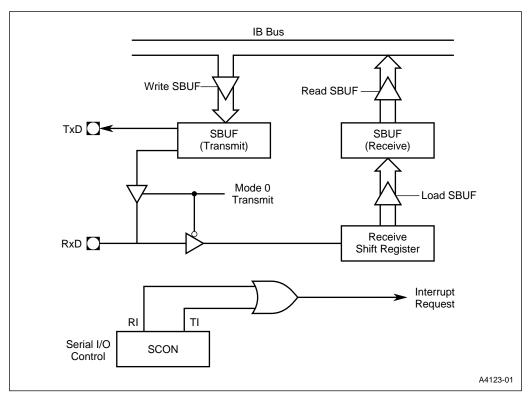

| 11.2.1 | l Sy | nchronous Mode (Mode 0)                      | 11-2  |

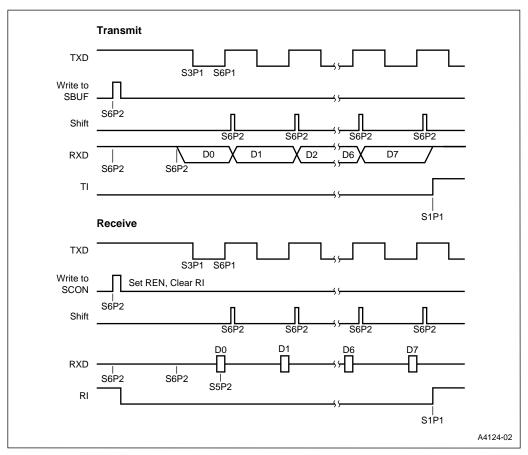

| 11.2   | .1.1 | Transmission (Mode 0)                        | 11-2  |

| 11.2   | .1.2 | Reception (Mode 0)                           |       |

|        |      | ynchronous Modes (Modes 1, 2, and 3)         |       |

| 11.2   |      | Transmission (Modes 1, 2, 3)                 |       |

| 11.2   |      | Reception (Modes 1, 2, 3)                    |       |

| 11.3   | FRAM | /ING BIT ERROR DETECTION (MODES 1, 2, AND 3) | 11-7  |

| 11.4   | MULT | FIPROCESSOR COMMUNICATION (MODES 2 AND 3)    | 11-8  |

| 11.5   | AUTO | DMATIC ADDRESS RECOGNITION                   | 11-8  |

| 11.5.1 | Gi   | ven Address                                  | 11-9  |

| 11.5.2 | 2 Br | oadcast Address                              | 11-9  |

| 11.5.3 | 8 Re | eset Addresses                               | 11-10 |

| 11.6   | BAUD | D RATES                                      | 11-10 |

| 11.6.1 | Ba   | aud Rate for Mode 0                          | 11-10 |

| 11.6.2 | 2 Ba | ud Rates for Mode 2                          |       |

| 11.6.3 | Ba   | aud Rates for Modes 1 and 3                  |       |

| 11.6   |      | Timer 1 Generated Baud Rates (Modes 1 and 3) |       |

| 11.6   | -    | Selecting Timer 1 as the Baud Rate Generator |       |

| 11.6   | -    | Timer 2 Generated Baud Rates (Modes 1 and 3) |       |

| 11.6   |      | Selecting Timer 2 as the Baud Rate Generator |       |

| 11.0   |      |                                              |       |

#### CHAPTER 12

#### **KEYBOARD CONTROL**

| 12.1  | OVERVIEW                     | 12-1 |

|-------|------------------------------|------|

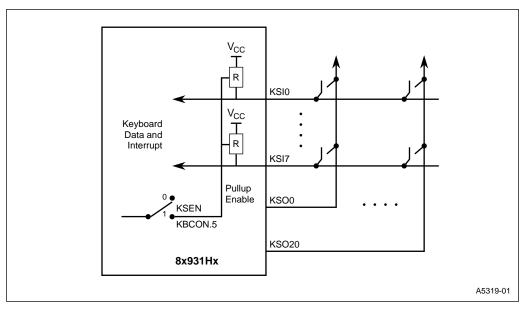

| 12.2  | KEYBOARD SCAN IMPLEMENTATION | 12-2 |

| 12.2. | 1 Keyboard Interrupt Logic   | 12-3 |

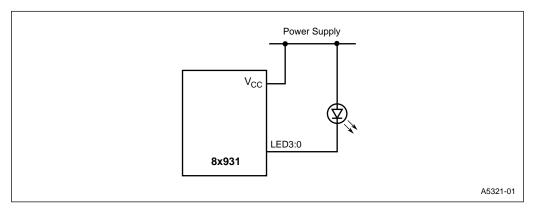

| 12.3  | LED DRIVERS                  | 12-4 |

#### **CHAPTER 13**

#### MINIMUM HARDWARE SETUP

| 13.1 N | INIMUM HARDWARE SETUP                  | 13-1 |

|--------|----------------------------------------|------|

| 13.2 E | ELECTRICAL ENVIRONMENT                 | 13-1 |

| 13.2.1 | Power and Ground Pins                  |      |

| 13.2.2 | Unused Pins                            | 13-2 |

| 13.2.3 | Noise Considerations                   | 13-2 |

| 13.3 C | CLOCK SOURCES                          | 13-2 |

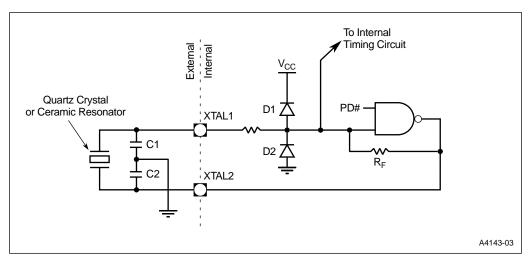

| 13.3.1 | On-chip Oscillator (Crystal)           | 13-2 |

| 13.3.2 | On-chip Oscillator (Ceramic Resonator) | 13-3 |

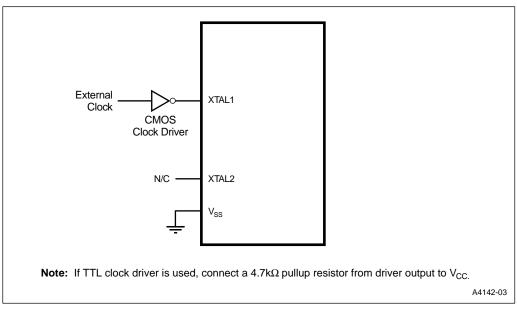

| 13.3.3 | External Clock                         | 13-3 |

| 13.4 F | RESET                                  | 13-5 |

#### CONTENTS

### intel

| 13.4.1 | Externally-initiated Resets | 13-5 |

|--------|-----------------------------|------|

| 13.4.2 | USB-initiated Resets        | 13-5 |

| 13.4.2 | 2.1 USB Reset Separation    | 13-6 |

| 13.4.3 | Reset Operation             | 13-6 |

|        | Power-on Reset              |      |

|        |                             |      |

#### CHAPTER 14

#### SPECIAL OPERATING MODES

| 4.1 OVERVIEW                                   |

|------------------------------------------------|

| 4.2 POWER CONTROL REGISTERS 14-1               |

| 14.2.1 Power Off Flag14-1                      |

| 4.3 IDLE MODE                                  |

| 14.3.1 Entering Idle Mode                      |

| 14.3.2 Exiting Idle Mode                       |

| 4.4 USB POWER CONTROL                          |

| 14.4.1 Global Suspend Mode14-7                 |

| 14.4.1.1 Powerdown (Suspend) Mode14-8          |

| 14.4.1.2 Entering Powerdown (Suspend) Mode14-8 |

| 14.4.1.3 Exiting Powerdown (Suspend) Mode14-8  |

| 14.4.2 Global Resume Mode                      |

| 14.4.3 USB Remote Wake-up                      |

| 4.5 LOW-CLOCK MODE                             |

| 14.5.1 Entering Low-clock Mode                 |

| 14.5.2 Exiting Low-clock Mode                  |

| 4.6 ON-CIRCUIT EMULATION (ONCE) MODE           |

| 14.6.1 Entering ONCE Mode                      |

| 14.6.2 Exiting ONCE Mode                       |

#### **CHAPTER 15**

#### EXTERNAL MEMORY INTERFACE

| OVERVIEW                                        | 15-1                                                                                                                                                                                                                        |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTERNAL BUS CYCLES                             |                                                                                                                                                                                                                             |

| Bus Cycle Definitions                           |                                                                                                                                                                                                                             |

| PORT 0 AND PORT 2 STATUS                        |                                                                                                                                                                                                                             |

| Port 0 and Port 2 Pin Status                    |                                                                                                                                                                                                                             |

| EXTERNAL MEMORY DESIGN EXAMPLES                 |                                                                                                                                                                                                                             |

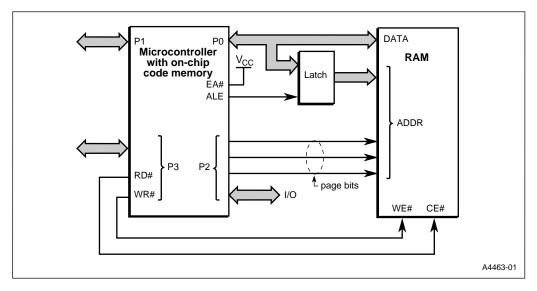

| Example 1: 11-bit Bus, External RAM             |                                                                                                                                                                                                                             |

| 2 Example 2: 16-bit Bus, External ROM           | 15-7                                                                                                                                                                                                                        |

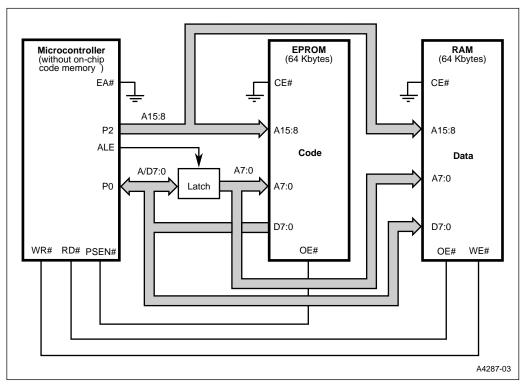

| B Example 3: 16-bit Bus, External EPROM and RAM | 15-8                                                                                                                                                                                                                        |

|                                                 | EXTERNAL BUS CYCLES<br>Bus Cycle Definitions<br>PORT 0 AND PORT 2 STATUS<br>Port 0 and Port 2 Pin Status<br>EXTERNAL MEMORY DESIGN EXAMPLES<br>Example 1: 11-bit Bus, External RAM<br>2 Example 2: 16-bit Bus, External ROM |

#### **CHAPTER 16**

| 16.1 | 83931 MEMORY | 16- | 1 |

|------|--------------|-----|---|

|------|--------------|-----|---|

| 16.2   | NONVOLATILE MEMORY                             | 16-1 |

|--------|------------------------------------------------|------|

| 16.3   | VERIFYING ON-CHIP NONVOLATILE MEMORY           | 16-1 |

| 16.3.1 | Verify Modes                                   | 16-2 |

| 16.3.2 | 2 General Setup                                |      |

| 16.3.3 | 3 Verify Algorithm                             |      |

| 16.3.4 | Verifying On-chip Program Memory               | 16-4 |

| 16.3.5 | 5 Verifying the Lock Bits                      |      |

| 16.3.6 | Verifying the Signature Bytes                  | 16-4 |

| 16.4   | ENCRYPTION ARRAY                               | 16-5 |

| 16.5   | CONSIDERATIONS FOR ON-CHIP PROGRAM CODE MEMORY | 16-5 |

#### APPENDIX A

#### **INSTRUCTION SET REFERENCE**

| A.1   | NOTATION FOR INSTRUCTION OPERANDS | A-2 |

|-------|-----------------------------------|-----|

| A.2   | OPCODE MAP                        | A-3 |

| A.3   | INSTRUCTION SET SUMMARY           | A-4 |

| A.3.1 | Instruction Summaries             | A-4 |

| A.4   | INSTRUCTION DESCRIPTIONS          | A-9 |

#### APPENDIX B

#### **PIN DESCRIPTIONS**

#### APPENDIX C

#### REGISTERS

| C.1 | SFRS BY FUNCTIONAL CATEGORY | C-3 |

|-----|-----------------------------|-----|

| C.2 | SFR DESCRIPTIONS            | C-6 |

#### APPENDIX D

#### DATA FLOW MODEL

#### APPENDIX E

#### 8X931AA DESIGN CONSIDERATIONS

| E.1 DIFFERENCES BETWEEN THE 8X931AA AND THE 8X931HA | E-1  |

|-----------------------------------------------------|------|

| E.2 8X931AA ENUMERATION PROCESS                     | E-2  |

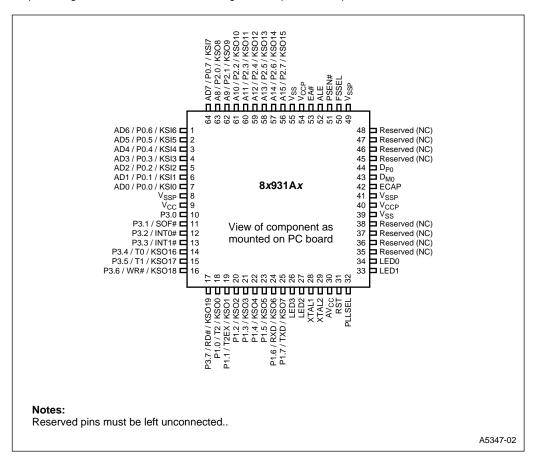

| E.3 8X931AA PIN DESCRIPTIONS                        | E-3  |

| E.4 8X931AA SIGNAL DESCRIPTIONS                     | E-6  |

| E.5 OPERATING FREQUENCIES                           | E-9  |

| E.6 8X931AA SFR MAP                                 | E-10 |

#### GLOSSARY

#### INDEX

#### FIGURES

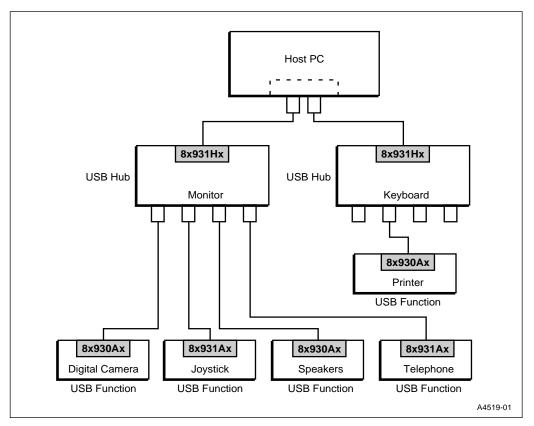

| 2-1  | 8x931 in a USB System                       | 2-1  |

|------|---------------------------------------------|------|

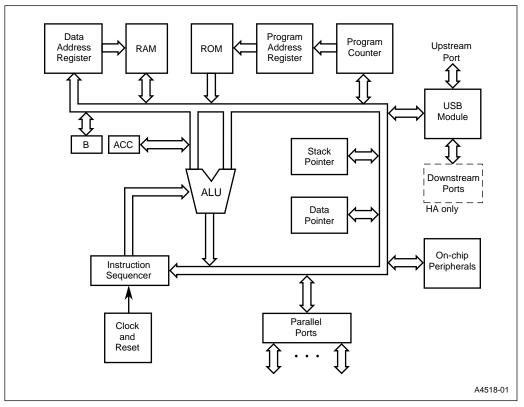

| 2-2  | Functional Block Diagram of the 8x931       | 2-2  |

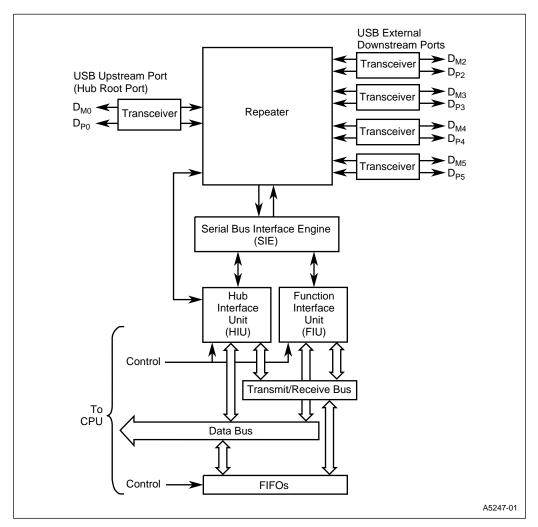

| 2-3  | 8x931HA USB Module Block Diagram            | 2-7  |

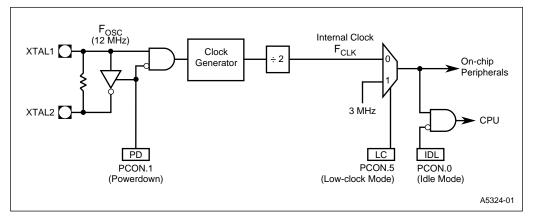

| 2-4  | 8x931 Clock Circuit                         |      |

| 2-5  | 8x931 Clocking Definitions                  | 2-10 |

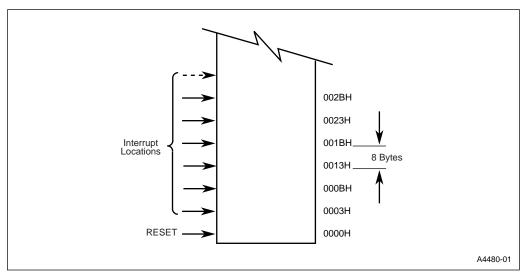

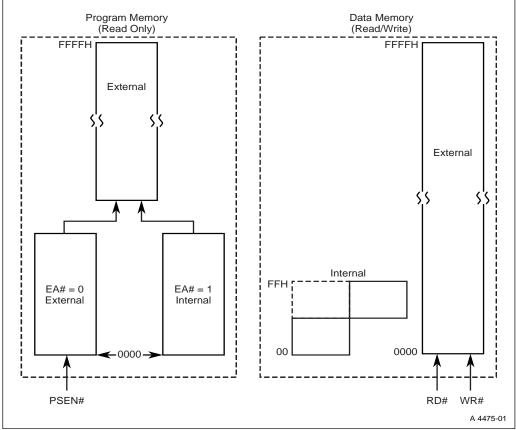

| 3-1  | MCS <sup>®</sup> 51 Program Memory          | 3-2  |

| 3-2  | 8x931 Memory Structure                      |      |

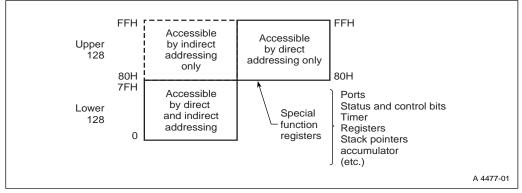

| 3-3  | Internal Data Memory                        | 3-4  |

| 3-4  | Upper and Lower 128 Bytes of Internal RAM   |      |

| 3-5  | SFR Space                                   | 3-5  |

| 4-1  | Program Status Word Register                | 4-2  |

| 4-2  | Shifting BCD Number Two Digits Right        | 4-9  |

| 4-3  | Shifting BCD Number One Digit Right         | 4-10 |

| 5-1  | Interrupt Control System                    | 5-3  |

| 5-2  | Bits of the Interrupt SFRs                  | 5-5  |

| 5-3  | FIE: USB Function Interrupt Enable Register |      |

| 5-4  | FIFLG: USB Function Interrupt Flag Register |      |

| 5-5  | SOFH: Start-of-frame High Register          | 5-12 |

| 5-6  | SOFL: Start-of-frame Low Register           |      |

| 5-7  | HIE: Hub Interrupt Enable Register          | 5-15 |

| 5-8  | HIFLG: Hub Interrupt Status Register        | 5-16 |

| 5-9  | USB Reset Separation Operating Model        | 5-20 |

| 5-10 | IEN0: USB Interrupt Enable Register 0       | 5-24 |

| 5-11 | IEN1: USB Interrupt Enable Register         | 5-25 |

| 5-12 | IPH0: Interrupt Priority High Register 0    | 5-27 |

| 5-13 | IPL0: Interrupt Priority Low Register 0     |      |

| 5-14 | IPH1: Interrupt Priority High Register 1    |      |

| 5-15 | IPL1: Interrupt Priority Low Register 1     |      |

| 5-16 | Interrupt Response Timing Diagram           |      |

| 6-1  | Bits of the USB Function SFRs               |      |

| 6-2  | EPINDEX: Endpoint Index Register            |      |

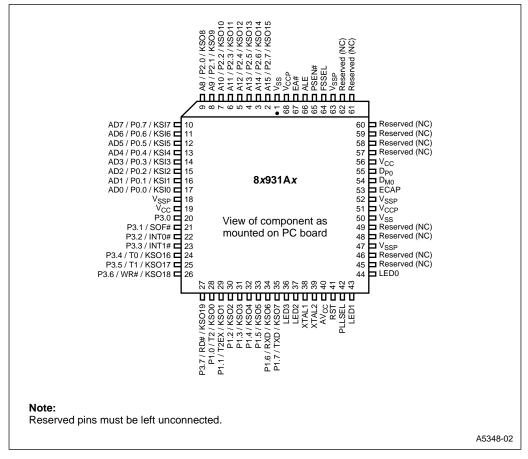

| 6-3  | EPCON: Endpoint Control Register            |      |

| 6-4  | TXSTAT: Transmit FIFO Status Register       |      |

| 6-5  | RXSTAT: Receive FIFO Status Register        |      |

| 6-6  | FADDR: Function Address Register            | 6-14 |

| 6-7  | Transmit FIFO Outline                       |      |

| 6-8  | TXDAT: Transmit FIFO Data Register          |      |

| 6-9  | TXCNTL: Transmit FIFO Byte Count Register   | 6-16 |

| 6-10 | TXCON: Transmit FIFO Control Register       |      |

| 6-11 | TXFLG: Transmit FIFO Flag Register          |      |

| 6-12 | Receive FIFO                                |      |

| 6-13 | RXDAT: Receive FIFO Data Register           |      |

| 6-14 | RXCNTL: Receive FIFO Byte Count Register    |      |

| 6-15 | RXCON: Receive FIFO Control Register        |      |

| 6-16 | RXFLG: Receive FIFO Flag Register           | 6-31 |

| 7-1   | 8x931HA Hub Functional Diagram               | 7-2  |

|-------|----------------------------------------------|------|

| 7-2   | Bits of the USB Hub SFRs                     | 7-3  |

| 7-3   | Hub State Flow                               | 7-5  |

| 7-4   | Packet Signaling Connectivity                | 7-6  |

| 7-5   | HADDR: Hub Address Register                  | 7-8  |

| 7-6   | HSTAT: Hub Status and Configuration Register |      |

| 7-7   | TXDAT: Hub Transmit Data Buffer (Endpoint 1) |      |

| 7-8   | Status Change Communication To Host          |      |

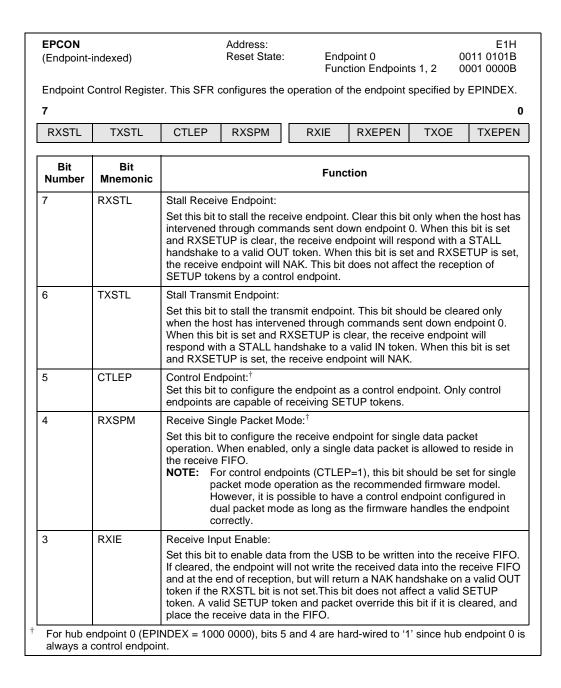

| 7-9   | HPCON: Hub Port Control Register             |      |

| 7-10  | HPSTAT: Hub Port Status Register             | 7-18 |

| 7-11  | HPSC: Hub Port Status Change Register        | 7-21 |

| 7-12  | HPINDEX: Hub Port Index Register             | 7-24 |

| 7-13  | Resume Connectivity                          | 7-26 |

| 7-14  | HPPWR: Hub Port Power Control                | 7-28 |

| 8-1   | Program Flow                                 | 8-1  |

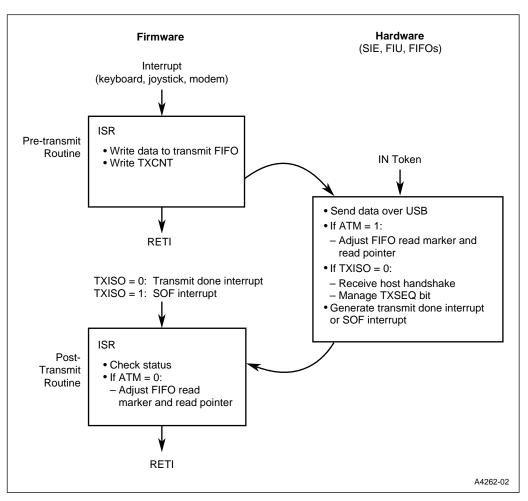

| 8-2   | High-level View of Transmit Operations       | 8-6  |

| 8-3   | Pre-transmit ISR (Non-Isochronous)           |      |

| 8-4   | Post-transmit ISR (Non-isochronous)          | 8-8  |

| 8-5   | Post-transmit ISR (Isochronous)              |      |

| 8-6   | High-level View of Receive Operations        |      |

| 8-7   | Post-receive ISR (Non-isochronous)           |      |

| 8-8   | Receive SOF ISR (Isochronous)                |      |

| 8-9   | Post-receive ISR (Control)                   | 8-15 |

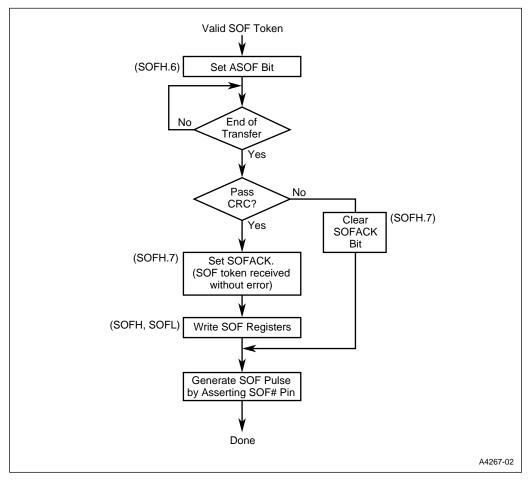

| 8-10  | Hardware Operations for SOF Token            | 8-16 |

| 8-11  | Hub-to-Host Port Status Communication        |      |

| 8-12  | GetPortStatus Request                        |      |

| 8-13  | Firmware Response to GetPortStatus           |      |

| 8-14  | SetPortFeature (PORT_SUSPEND) Routine        |      |

| 8-15  | SetPortFeature (PORT_RESET) Routine          |      |

| 9-1   | Port 1 and Port 3 Structure                  |      |

| 9-2   | Port 0 Structure                             |      |

| 9-3   | Port 2 Structure                             |      |

| 9-4   | Internal Pullup Configurations               |      |

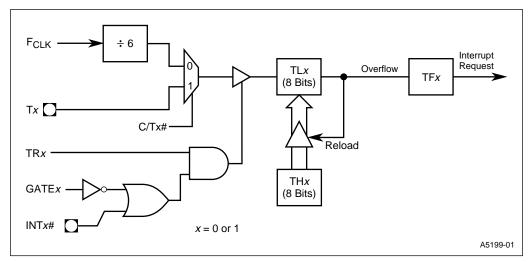

| 10-1  | Basic Logic of the Timer/Counters            |      |

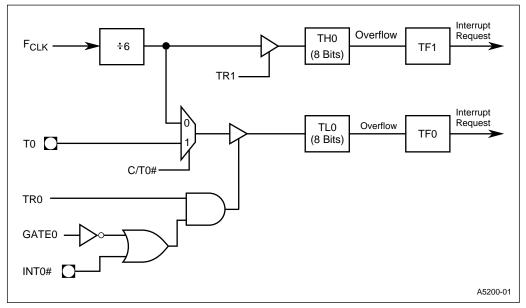

| 10-2  | Timer 0/1 in Mode 0 and Mode 1               |      |

| 10-3  | Timer 0/1 in Mode 2, Auto-reload             |      |

| 10-4  | Timer 0 in Mode 3, Two 8-bit Timers          |      |

| 10-5  | TMOD: Timer/Counter Mode Control Register    |      |

| 10-6  | TCON: Timer/Counter Control Register         |      |

| 10-7  | Timer 2: Capture Mode                        |      |

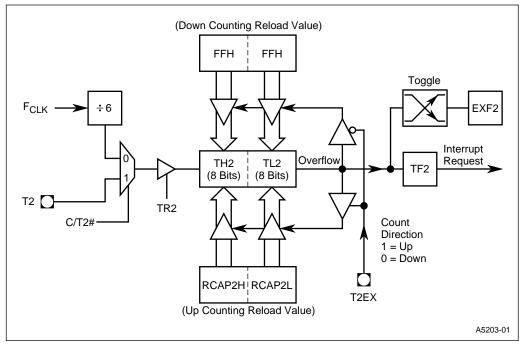

| 10-8  | Timer 2: Auto-reload Mode (DCEN = 0)         |      |

| 10-9  | Timer 2: Auto-reload Mode (DCEN = 1)         |      |

| 10-10 | Timer 2: Clock Out Mode                      |      |

| 10-11 | T2MOD: Timer 2 Mode Control Register         |      |

| 10-12 | T2CON: Timer 2 Control Register              |      |

| 11-1  | Serial Port Block Diagram                    |      |

| 11-2  | SCON: Serial Port Control Register           | 11-4 |

| 11-3 | Mode 0 Timing                                                  |       |

|------|----------------------------------------------------------------|-------|

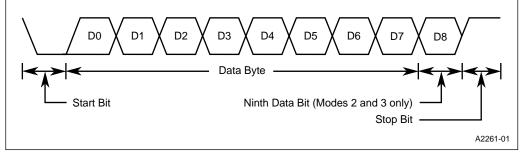

| 11-4 | Data Frame (Modes 1, 2, and 3)                                 |       |

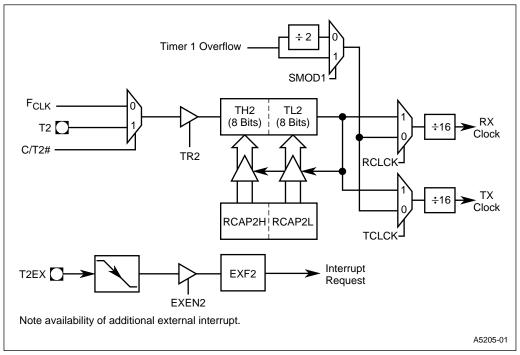

| 11-5 | Timer 2 in Baud Rate Generator Mode                            |       |

| 12-1 | KBCON: Keyboard Control Register                               | 12-1  |

| 12-2 | Keyboard Scan Matrix Application                               | 12-3  |

| 12-3 | LED Driver Application                                         | 12-4  |

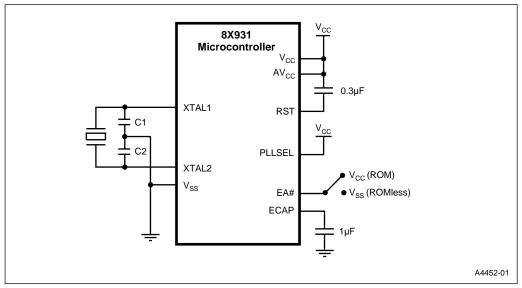

| 13-1 | Minimum Setup                                                  | 13-1  |

| 13-2 | CHMOS On-chip Oscillator                                       | 13-3  |

| 13-3 | External Clock Connection for the 8x931                        | 13-4  |

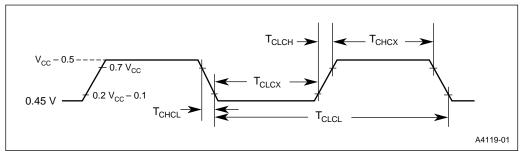

| 13-4 | External Clock Drive Waveforms                                 | 13-4  |

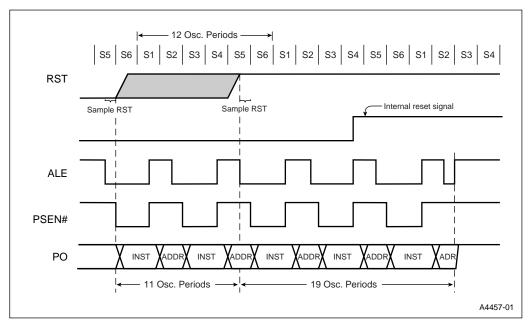

| 13-5 | Reset Timing Sequence                                          | 13-7  |

| 14-1 | PCON: Power Control Register                                   | 14-3  |

| 14-2 | PCON1: USB Power Control Register                              |       |

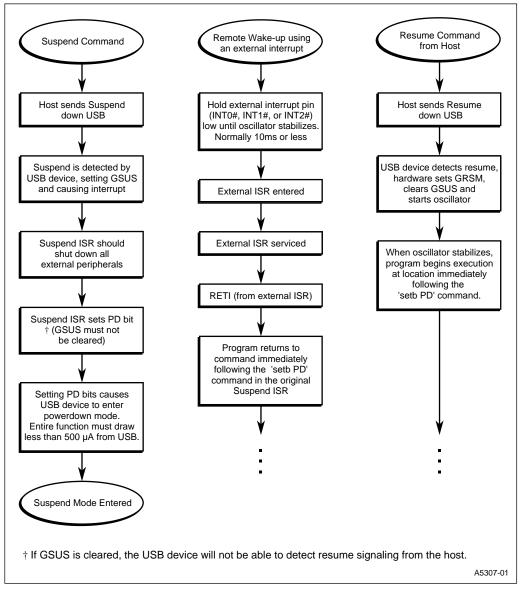

| 14-3 | Suspend/Resume Program with/without Remote Wake-up             | 14-11 |

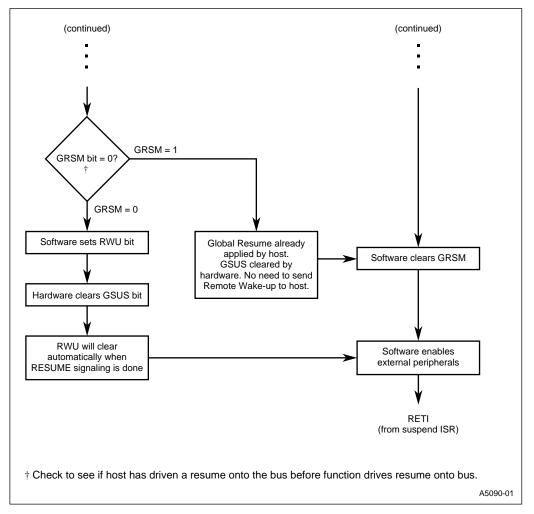

| 14-4 | Suspend/Resume Program with/without Remote Wake-up (Continued) | 14-12 |

| 15-1 | Bus Structure                                                  | 15-1  |

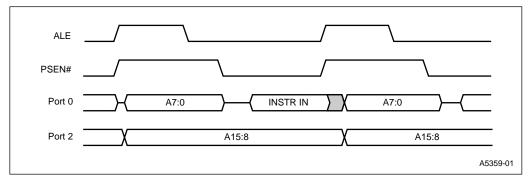

| 15-2 | External Code Fetch                                            | 15-3  |

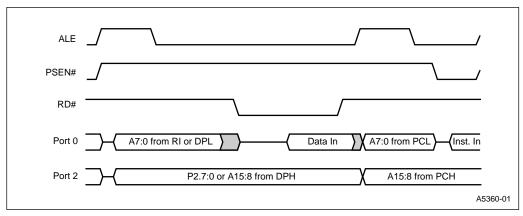

| 15-3 | External Data Read                                             | 15-4  |

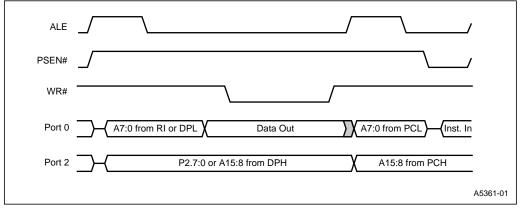

| 15-4 | External Data Write                                            | 15-4  |

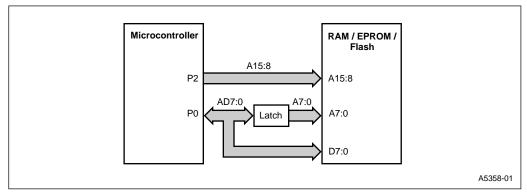

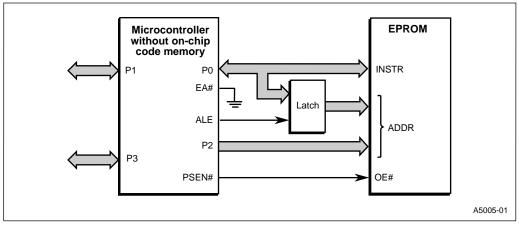

| 15-5 | Bus Diagram for Example 1: 8x931AA/HA                          | 15-6  |

| 15-6 | Bus Diagram for Example 2: 8x931AA/HA                          | 15-7  |

| 15-7 | Bus Diagram for Example 3: 8x931AA/HA                          | 15-8  |

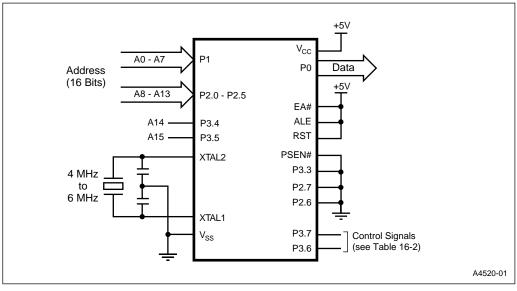

| 16-1 | Setup for Verifying Nonvolatile Memory                         |       |

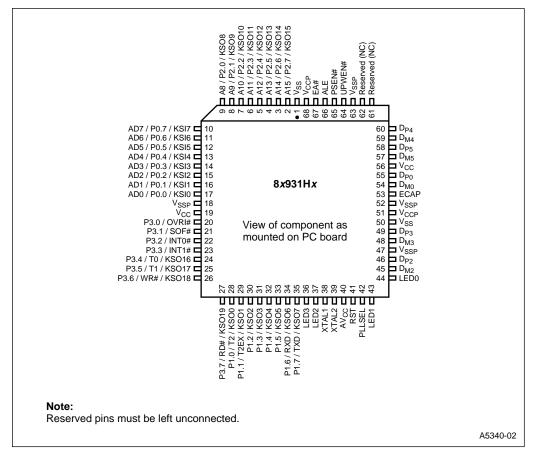

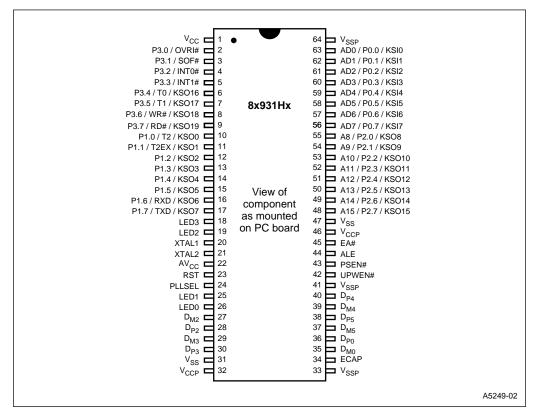

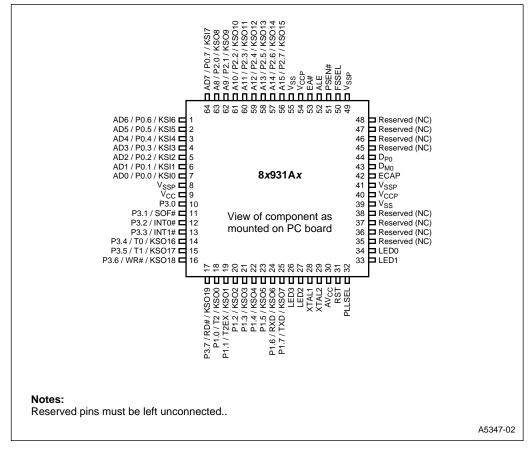

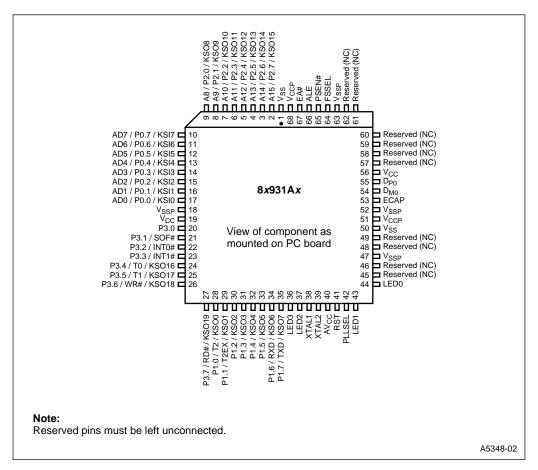

| B-1  | 8x931HA 68-pin PLCC Package                                    |       |

| B-2  | 8x931HA 64-pin SDIP Package                                    | B-2   |

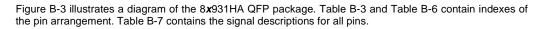

| B-3  | 8x931HA 64-pin QFP Package                                     | B-3   |

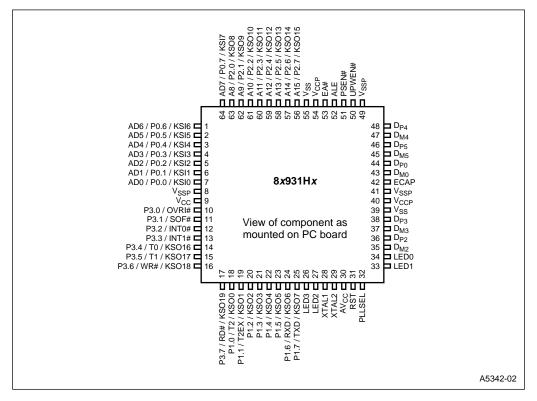

| B-4  | 8x931AA 64-pin QFP Package                                     |       |

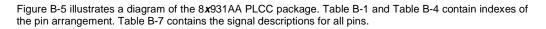

| B-5  | 8x931AA 68-pin PLCC Package                                    | B-5   |

| E-1  | 8x931AA 64-pin QFP Package                                     |       |

| E-2  | 8x931AA 68-pin PLCC                                            |       |

|      |                                                                |       |

#### TABLES

| 1-1  | Intel Application Support Services                                 | 1-7   |

|------|--------------------------------------------------------------------|-------|

| 2-1  | 8x931 Memory Options                                               | 2-3   |

| 2-2  | USB Peripheral Controller Feature Summary and Comparison           | 2-4   |

| 2-3  | 8x931HA Operating Frequency                                        |       |

| 2-4  | 8x931AA Operating Frequencies                                      | 2-10  |

| 2-5  | Endpoint Pairs for 8x931                                           | 2-12  |

| 4-1  | The Effects of Instructions on the PSW Flags                       | 4-3   |

| 4-2  | Addressing Modes for Data Instructions in the MCS® 51 Architecture | 4-4   |

| 4-3  | List of MCS <sup>®</sup> 51 Arithmetic Instructions                | 4-5   |

| 4-4  | List of MCS <sup>®</sup> 51 Logical Instructions                   | 4-6   |

| 4-5  | List of MCS <sup>®</sup> 51 Data Transfer Instructions             |       |

| 4-6  | Transfer Instructions for Accessing External Data Memory Space     | 4-11  |

| 4-7  | MCS <sup>®</sup> 51 Read Instructions                              |       |

| 4-8  | MCS <sup>®</sup> 51Boolean Instructions                            |       |

| 4-9  | Unconditional Jumps in MCS <sup>®</sup> 51 Devices                 |       |

| 4-10 | Conditional Jumps in MCS <sup>®</sup> 51 Devices                   |       |

| 5-1  | Interrupt System Input Signals                                     |       |

| 5-2  | Interrupt System Special Function Registers                        |       |

| 5-3  | 8x931AA/HA Interrupt Control Matrix                                |       |

| 5-4  | 8x931 USB/Hub Interrupt Control Matrix                             |       |

| 5-5  | Level of Priority                                                  |       |

| 5-6  | Interrupt Priority Within Level                                    |       |

| 6-1  | Function and Hub FIFO Configurations                               |       |

| 6-2  | Non-hub USB Signal Descriptions                                    |       |

| 6-3  | USB Function SFRs                                                  | 6-3   |

| 6-4  | Writing to the Byte Count Register                                 |       |

| 6-5  | Truth Table for Transmit FIFO Management                           | 6-18  |

| 6-6  | Status of the Receive FIFO Data Sets                               | 6-27  |

| 6-7  | Truth Table for Receive FIFO Management                            | 6-28  |

| 7-1  | USB Hub SFRs                                                       | 7-3   |

| 7-2  | 8x931 Descriptors                                                  | 7-7   |

| 7-3  | Hub Descriptors                                                    | 7-8   |

| 7-4  | Hub Endpoint Configuration                                         | 7-11  |

| 7-5  | USB Requests Ignored by Hardware (by Port State)                   | 7-14  |

| 7-6  | Encoded Hub Port Control Commands                                  | 7-16  |

| 7-7  | UPWEN# Pin State Truth Table                                       | 7-30  |

| 7-8  | Signal Descriptions                                                | 7-30  |

| 8-1  | Firmware Actions for USB Requests Sent to Hub                      | 8-17  |

| 8-2  | Firmware Action for Hub Class-Specific Requests                    | 8-20  |

| 9-1  | Input/Output Port Pin Descriptions                                 | 9-1   |

| 9-2  | Read-Modify-Write Instructions                                     |       |

| 9-3  | Instructions for External Data Moves                               | 9-7   |

| 10-1 | External Signals                                                   |       |

| 10-2 | Timer/Counter and Watchdog Timer SFRs                              |       |

| 10-3 | Timer 2 Modes of Operation.                                        | 10-15 |

#### CONTENTS

### intel

| 11-1 | Serial Port Signals                                                 | 11-1  |

|------|---------------------------------------------------------------------|-------|

| 11-2 | Serial Port Special Function Registers                              | 11-2  |

| 11-3 | Summary of Baud Rates                                               |       |

| 11-4 | Timer 1 Generated Baud Rates for Serial I/O Modes 1 and 3           | 11-12 |

| 11-5 | Selecting the Baud Rate Generator(s)                                | 11-13 |

| 11-6 | Timer 2 Generated Baud Rates                                        |       |

| 12-1 | Keyboard Control Signals                                            |       |

| 14-1 | Pin Conditions in Various Modes                                     | 14-6  |

| 15-1 | External Memory Interface Signals                                   |       |

| 15-2 | Port 0 and Port 2 Pin Status In Normal Operating Mode               | 15-5  |

| 16-1 | Signal Descriptions (Verify Mode)                                   |       |

| 16-2 | Verify Modes                                                        |       |

| 16-3 | Lock Bit Function                                                   |       |

| 16-4 | Contents of the Signature Bytes                                     | 16-4  |

| A-1  | Notation for Register Operands                                      | A-2   |

| A-2  | Notation for Direct Addresses                                       |       |

| A-3  | Notation for Immediate Addressing                                   | A-2   |

| A-4  | Notation for Bit Addressing                                         | A-2   |

| A-5  | Notation for Destinations in Control Instructions                   | A-2   |

| A-6  | Instructions for 8x931 Peripheral Controllers                       | A-3   |

| A-7  | Summary of Add and Subtract Instructions                            | A-4   |

| A-8  | Summary of Increment and Decrement Instructions                     | A-4   |

| A-9  | Summary of Multiply, Divide, and Decimal-adjust Instructions        | A-5   |

| A-10 | Summary of Logical Instructions                                     | A-5   |

| A-11 | Summary of Move Instructions                                        |       |

| A-12 | Summary of Exchange, Push, and Pop Instructions                     |       |

| A-13 | Summary of Bit Instructions                                         |       |

| A-14 | Summary of Control Instructions                                     |       |

| A-15 | Flag Symbols                                                        | A-9   |

| B-1  | 68-pin PLCC Pin Assignment                                          |       |

| B-2  | 64-pin SDIP Pin Assignment                                          |       |

| B-3  | 64-pin QFP Pin Assignment                                           |       |

| B-4  | 68-pin PLCC Signal Assignments Arranged by Functional Category      |       |

| B-5  | 64-pin SDIP Signal Assignments Arranged by Functional Category      |       |

| B-6  | 64-pin QFP Signal Assignments Arranged by Functional Category       |       |

| B-7  | Signal Description                                                  |       |

| C-1  | 8x931HA SFR Map                                                     |       |

| C-2  | Core SFRs                                                           |       |

| C-3  | Interrupt System SFRs                                               |       |

| C-4  | I/O Port SFRs                                                       |       |

| C-5  | Serial I/O SFRs                                                     |       |

| C-6  | USB Function SFRs                                                   |       |

| C-7  | USB Hub SFRs                                                        |       |

| C-8  | Timer/Counter SFRs                                                  |       |

| D-1  | Non-isochronous Transmit Data Flow                                  |       |

| D-2  | Isochronous Transmit Data Flow in Dual-packet Mode                  |       |

| D-3  | Non-isochronous Receive Data Flow in Single-packet Mode (RXSPM = 1) | D-8   |

#### 8x931AA, 8x931HA USER'S MANUAL

### intel

| Non-isochronous Receive Data Flow in Dual-packet Mode (RXSPM = 0) | D-11                                                          |

|-------------------------------------------------------------------|---------------------------------------------------------------|

| Isochronous Receive Data Flow in Dual-packet Mode (RXSPM = 0)     | D-18                                                          |

| 8x931AA Signals Arranged by Functional Category                   | E-5                                                           |

| 8x931AA Signal Descriptions                                       | E-6                                                           |

| 8x931AA Operating Frequencies                                     | E-9                                                           |

| 8x931AA SFR Map                                                   | E-10                                                          |

|                                                                   | Isochronous Receive Data Flow in Dual-packet Mode (RXSPM = 0) |

1

### **Guide to this Manual**

### CHAPTER 1 GUIDE TO THIS MANUAL

This manual describes the 8x931 microcontroller for universal serial bus (USB) applications. This manual is intended for use by both firmware and hardware designers familiar with the principles of microcontroller architecture.

#### 1.1 MANUAL CONTENTS

This chapter provides an overview of the manual with brief summaries of the chapters and appendices. It also explains the terminology and notational conventions used throughout the manual, provides references to related documentation, and tells how to contact Intel for additional information.

**Chapter 2, "Architectural Overview"**— provides an overview of device hardware. It covers core functions (CPU, clock and reset unit, and interrupts), I/O ports, on-chip memory, the USB module, and on-chip peripherals (timer/counters and serial I/O port).

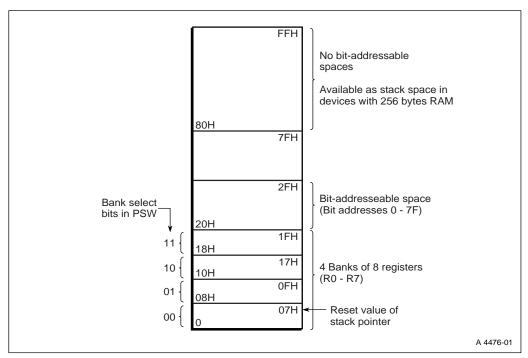

**Chapter 3, "Address Spaces"**— describes the three address spaces of the 8x931: memory address space, special function register (SFR) space, and the register file. It also provides a map of the SFR space showing the location of the SFRs and their reset values and explains the mapping of the address spaces relative to the MCS<sup>®</sup> 51 architecture into the address spaces of the 8x931.

**Chapter 4, "Programming Considerations"**— provides an overview of the instruction set. It describes each instruction type (control, arithmetic, logical, etc.) and lists the instructions in tabular form. This chapter also discusses the addressing modes, bit instructions, and the program status words. Appendix A, "Instruction Set Reference" provides a detailed description of each instruction.

**Chapter 5, "Interrupt System"**— describes the 8*x*931 interrupt circuitry which provides ten maskable interrupts: three external interrupts, three timer interrupts, a serial port interrupt, and three USB interrupts. This chapter also discusses the interrupt priority scheme, interrupt enable, interrupt processing, and interrupt response time.

**Chapter 6, "USB Function"**— describes the FIFOs and special function registers (SFRs) associated with the USB function interface. This chapter describes the operation of function interface on the 8x931 USB microcontrollers.

**Chapter 7, "USB Hub"**— describes the operation of the Intel Universal Serial Bus (USB) onchip hub. This chapter introduces on-chip hub operation and includes information on bus enumeration, hub endpoint status and configuration, hub port control, hub suspend and resume, and hub power control.

**Chapter 8, "USB Programming Models"**— describes the programming models of the 8x931 USB function interface. This chapter provides flow charts of suggested firmware routines for using the transmit and receive FIFOs to perform data transfers between the host PC and the embedded function and describes how the firmware interacts with the USB module hardware.

**Chapter 9, "Input/Output Ports"**— describes the four 8-bit I/O ports (ports 0–3) and discusses their configuration for general-purpose I/O. This chapter also discusses external memory accesses (ports 0, 2) and alternative special functions.

**Chapter 10, "Timer/Counters"**—describes the three on-chip timer/counters and discusses their application.

**Chapter 11, "Serial I/O Port"**—describes the full-duplex serial I/O and explains how to program it to communicate with external peripherals. This chapter also discusses baud rate generation, framing error detection, multiprocessor communications, and automatic address recognition.

**Chapter 12, "Keyboard Control"**— describes the 8x931 keyboard control interface, including the keyboard scan output lines, the keyboard scan input lines, and the LED drivers.

**Chapter 13, "Minimum Hardware Setup"**— describes the basic requirements for operating the 8x931 in a system. It also discusses on-chip and external clock sources.

**Chapter 14, "Special Operating Modes"**— provides an overview of the idle, powerdown, and on-circuit emulation (ONCE) modes and describes how to enter and exit each mode. This chapter also describes the power control (PCON) special function register and lists the status of the device pins during the special modes.

**Chapter 15, "External Memory Interface"**— describes the external memory signals and bus cycles and provides examples of external memory design. It also provides waveform diagrams for the bus cycles.

**Chapter 16, "Verifying Nonvolatile Memory"**— provides instructions for verifying on-chip program memory, signature bytes, and lock bits.

**Appendix A, "Instruction Set Reference"**— provides reference information for the instruction set. It describes each instruction; defines the bits in the program status word register (PSW); shows the relationships between instructions and PSW flags; and lists hexadecimal opcodes, instruction lengths, and execution times.

**Appendix B, "Pin Descriptions"**— describes the function(s) of each device pin. Descriptions are listed alphabetically by signal name. This appendix also provides a list of the signals grouped by functional category.

**Appendix C, "Registers"**— accumulates, for convenient reference, copies of the register definition figures that appear throughout the manual.

**Appendix D, "Data Flow Model"**— describes the data flow model for the 8*x*931 USB transactions.

**Appendix E, "8x931AA Design Considerations"**—describes the differences between the hubless 8x931AA and the 8x931HA.

**Glossary** — a glossary of terms has been provided for reference of technical terms.

Index — an index has been included for your convenience.

#### 1.2 NOTATIONAL CONVENTIONS AND TERMINOLOGY

The following notations and terminology are used in this manual. The Glossary defines other terms with special meanings.

| #                   | The pound symbol (#) has either of two meanings, depending on the context. When used with a signal name, the symbol means that the signal is active low. When used with an instruction mnemonic, the symbol prefixes an immediate value in immediate addressing mode.                                                                                                                                                                                   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italics             | Italics identify variables and introduce new terminology. The context<br>in which italics are used distinguishes between the two possible<br>meanings.                                                                                                                                                                                                                                                                                                  |

|                     | Variables in registers and signal names are commonly represented by $x$ and $y$ , where $x$ represents the first variable and $y$ represents the second variable. For example, in register Px.y, $x$ represents the variable [1–4] that identifies the specific port, and $y$ represents the register bit variable [7:0]. Variables must be replaced with the correct values when configuring or programming registers or identifying signals.          |

| XXXX, xxxx          | Uppercase X (no italics) and lowercase x (no italics) represent<br>unknown values or a "don't care" states or conditions. The value may<br>be either binary or hexadecimal, depending on the context. For<br>example, $2xAFH$ (hex) indicates that bits 11:8 are unknown; $10xx$ in<br>binary context indicates that the two LSBs are unknown.                                                                                                          |

| Assert and Deassert | The terms <i>assert</i> and <i>deassert</i> refer to the act of making a signal active (enabled) and inactive (disabled), respectively. The active polarity (high/low) is defined by the signal name. Active-low signals are designated by a pound symbol (#) suffix; active-high signals have no suffix. To assert RD# is to drive it low; to assert ALE is to drive it high; to deassert RD# is to drive it high; to deassert ALE is to drive it low. |

| Instructions        | Instruction mnemonics are shown in upper case to avoid confusion.<br>When writing code, either upper case or lower case may be used.                                                                                                                                                                                                                                                                                                                    |

| Logic 0 (Low)       | An input voltage level equal to or less than the maximum value of $V_{\rm IL}$ or an output voltage level equal to or less than the maximum value of $V_{\rm OL}$ . See data sheet for values.                                                                                                                                                                                                                                                          |

| Logic 1 (High)      | An input voltage level equal to or greater than the minimum value of $V_{IH}$ or an output voltage level equal to or greater than the minimum value of $V_{OH}$ . See data sheet for values.                                                                                                                                                                                                                                                            |

#### 8x931AA, 8x931HA USER'S MANUAL

| Numbers          | Hexadecimal numbers are represented by a string of hexadecimal digits followed by the character $H$ . Decimal and binary numbers are represented by their customary notations. That is, 255 is a decimal number and 1111 1111 is a binary number. In some cases, the letter $B$ is added for clarity.                                                                                                                                                                             |                      |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Register Access  | All register bits support read/write access unless noted otherwise in<br>the bit description. Other types of access include read-only, write-<br>only, read/conditional-write, etc.                                                                                                                                                                                                                                                                                               |                      |  |

| Register Bits    | Bit locations are indexed by 7:0 for byte registers, 15:0 for word registers, and 31:0 for double-word (dword) registers, where bit 0 is the least-significant bit and 7, 15, or 31 is the most-significant bit. An individual bit is represented by the register name, followed by a period and the bit number. For example, PCON.4 is bit 4 of the power control register. In some discussions, bit names are used. For example, the name of PCON.4 is POF, the power-off flag. |                      |  |

| Register Names   | Register names are shown in upper case. For example, PCON is the power control register. If a register name contains a lowercase character, it represents more than one register. For example, CCAPM <i>x</i> represents the five registers: CCAPM0 through CCAPM4.                                                                                                                                                                                                               |                      |  |

| Reserved Bits    | Some registers contain reserved bits. These bits are not used in this device, but they may be used in future implementations. Do not write a "1" to a reserved bit. The value read from a reserved bit is indeterminate.                                                                                                                                                                                                                                                          |                      |  |

| Set and Clear    | The terms <i>set</i> and <i>clear</i> refer to the value of a bit or the act of giving it a value. If a bit is <i>set</i> , its value is "1"; <i>setting</i> a bit gives it a "1" value. If a bit is <i>clear</i> , its value is "0"; <i>clearing</i> a bit gives it a "0" value.                                                                                                                                                                                                 |                      |  |

| Signal Names     | Signal names are shown in upper case. When several signals share a common name, an individual signal is represented by the signal name followed by a number. Port pins are represented by the port abbreviation, a period, and the pin number (e.g., P0.0, P0.1). A pound symbol (#) appended to a signal name identifies an active-low signal.                                                                                                                                   |                      |  |

| Units of Measure | The following abbreviations are used to represent units of measure:                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |

|                  | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | amps, amperes        |  |

|                  | DCV                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | direct current volts |  |

|                  | Kbyte                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | kilobytes            |  |

|                  | KΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | kilo-ohms            |  |

| mA    | milliamps, milliamperes |  |  |

|-------|-------------------------|--|--|

| Mbyte | megabytes               |  |  |

| MHz   | megahertz               |  |  |

| ms    | milliseconds            |  |  |

| mW    | milliwatts              |  |  |

| ns    | nanoseconds             |  |  |

| pF    | picofarads              |  |  |

| W     | watts                   |  |  |

| V     | volts                   |  |  |

| μΑ    | microamps, microamperes |  |  |

| μF    | microfarads             |  |  |

| μs    | microseconds            |  |  |

| μW    | microwatts              |  |  |

#### 1.3 RELATED DOCUMENTS

The following documents contain additional information that is useful in designing systems that incorporate the 8x931. To order documents, please call Intel Literature Fulfillment (1-800-548-4725 in the U.S. and Canada; +44(0) 793-431155 in Europe).

| Embedded Microcontrollers                                | Order Number 270646 |

|----------------------------------------------------------|---------------------|

| Embedded Processors                                      | Order Number 272396 |

| Embedded Applications                                    | Order Number 270648 |

| Packaging                                                | Order Number 240800 |

| Universal Serial Bus Specification                       | Order Number 272904 |

| MCS <sup>®</sup> 51 Microcontroller Family User's Manual | Order Number 272383 |

#### 1.3.1 Data Sheet

The data sheet is included in *Embedded Microcontrollers* and is also available individually.

| 8x931AA/8x931HA Universal Serial Bus Microcontroller | Order Number 273108 |

|------------------------------------------------------|---------------------|

|------------------------------------------------------|---------------------|

#### 1.3.2 Application Notes

The following MCS 51 microcontroller application notes also apply to the 8x931.

| AP-70, Using the Intel MCS <sup>®</sup> 51 Boolean Processing Capabilities                                         | Order Number 203830 |

|--------------------------------------------------------------------------------------------------------------------|---------------------|

| AP-223, 8051 Based CRT Terminal Controller                                                                         | Order Number 270032 |

| AP-252, Designing With the 80C51BH                                                                                 | Order Number 270068 |

| AP-425, Small DC Motor Control                                                                                     | Order Number 270622 |

| AP-410, Enhanced Serial Port on the 83C51FA                                                                        | Order Number 270490 |

| AP-476, How to Implement I <sup>2</sup> C Serial Communication<br>Using Intel MCS <sup>®</sup> 51 Microcontrollers | Order Number 272319 |

#### 1.4 APPLICATION SUPPORT SERVICES

You can get up-to-date technical information from a variety of electronic support systems: the World Wide Web, the FaxBack\* service, and Intel's Brand Products and Applications Support

bulletin board service (BBS). These systems are available 24 hours a day, 7 days a week, providing technical information whenever you need it.

In the U.S. and Canada, technical support representatives are available to answer your questions between 5 a.m. and 5 p.m. Pacific Standard Time (PST). Outside the U.S. and Canada, please contact your local distributor. You can order product literature from Intel literature centers and sales offices.

Table 1-1 lists the information you need to access these services.

| Service           | U.S. and Canada                          | Asia-Pacific and Japan                   | Europe                                                                                      |  |

|-------------------|------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------|--|

| World Wide<br>Web | URL:http://www.intel.com/                | URL:http://www.intel.com/                | URL:http://www.intel.com/                                                                   |  |

| World Wide<br>Web | URL:http://www.intel.com/<br>design/usb/ | URL:http://www.intel.com/<br>design/usb/ | URL:http://www.intel.com/<br>design/usb/                                                    |  |

| FaxBack*          | 800-525-3019                             | 503-264-6835<br>916-356-3105             | +44(0)1793-496646                                                                           |  |

| BBS               | 503-264-7999<br>916-356-3600             | 503-264-7999<br>916-356-3600             | +44(0)1793-432955                                                                           |  |

| Help Desk         | 800-628-8686<br>916-356-7999             | Please contact your local distributor.   | Please contact your local distributor.                                                      |  |

| Literature        | 800-548-4725                             | 708-296-9333<br>+81(0)120 47 88 32       | +44(0)1793-431155<br>England<br>+44(0)1793-421777<br>France<br>+44(0)1793-421333<br>Germany |  |

Table 1-1. Intel Application Support Services

#### 1.4.1 World Wide Web

We offer a variety of technical and product information through the World Wide Web (URL: ht-tp://www.intel.com/design/usb). Also visit Intel's Web site for financials, history, news and USB information at: www.intel.com/design/.

#### 1.4.2 FaxBack Service

The FaxBack service is an on-demand publishing system that sends documents to your fax machine. You can get product announcements, change notifications, product literature, device characteristics, design recommendations, and quality and reliability information from FaxBack 24 hours a day, 7 days a week.

Think of the FaxBack service as a library of technical documents that you can access with your phone. Just dial the telephone number and respond to the system prompts. After you select a document, the system sends a copy to your fax machine.

Each document is assigned an order number and is listed in a subject catalog. The first time you use FaxBack, you should order the appropriate subject catalogs to get a complete listing of document order numbers. Catalogs are updated twice monthly. In addition, daily update catalogs list the title, status, and order number of each document that has been added, revised, or deleted during the past eight weeks. The daily update catalogs are numbered with the subject catalog number followed by a zero. For example, for the complete microcontroller and flash catalog, request document number 2; for the daily update to the microcontroller and flash catalog, request document number 20.

The following catalogs and information are available at the time of publication:

- 1. Solutions OEM subscription form

- 2. Microcontroller and flash catalog

- 3. Development tools catalog

- 4. Systems catalog

- 5. Multimedia catalog

- 6. Multibus and iRMX<sup>®</sup> firmware catalog and BBS file listings

- 7. Microprocessor, PCI, and peripheral catalog

- 8. Quality and reliability and change notification catalog

- 9. iAL (Intel Architecture Labs) technology catalog

#### 1.4.3 Bulletin Board System (BBS)

Intel's Brand Products and Applications Support bulletin board system (BBS) lets you download files to your PC. The BBS has the latest *Ap*BUILDER firmware, hypertext manuals and datasheets, firmware drivers, firmware upgrades, application notes and utilities, and quality and reliability data.

Any customer with a PC and modem can access the BBS. The system provides automatic configuration support for 1200- through 19200-baud modems. Use these modem settings: no parity, 8 data bits, and 1 stop bit (N, 8, 1).

To access the BBS, just dial the telephone number (see Table 1-1 on page 1-7) and respond to the system prompts. During your first session, the system asks you to register with the system operator by entering your name and location. The system operator will set up your access account within 24 hours. At that time, you can access the files on the BBS.

#### NOTE

In the U.S. and Canada, you can get a BBS user's guide, a master list of BBS files, and lists of FaxBack documents by calling 1-800-525-3019. Use these modem settings: no parity, 8 data bits, and 1 stop bit (N, 8, 1).

2

Architectural Overview

### CHAPTER 2 ARCHITECTURAL OVERVIEW

The 8x931AA and 8x931HA are PC peripheral controllers for Universal Serial Bus (USB) applications. These peripheral controllers provide the means for connecting PC peripherals such as monitors, keyboards, joysticks, telephones, and modems to USB-equipped personal computers. For keyboard applications, both devices include an on-chip keyboard control interface. The USB material in this document relies heavily on the *Universal Serial Bus Specification* which provides a detailed description of the USB system.

In the language of the USB specification, the 8x931AA/HA is a *USB device*. A USB device can serve as a *function* by providing an interface for a PC peripheral, and it can serve as a *hub* by providing USB ports for additional PC peripherals.

The 8x931AA is a hubless USB peripheral controller which serves as a USB function. The 8x931HA serves as both a USB function and as a hub; it supports one embedded function and provides four external downstream ports. Figure 2-1 depicts the 8x931 in an example USB system.

Figure 2-1. 8x931 in a USB System

Figure 2-2. Functional Block Diagram of the 8x931

#### 2.1 PRODUCT OVERVIEW

The 8x931 employs the architecture of the MCS<sup>®</sup> 51 microcontroller family. Specifically, it is derived from the 8xC51Fx core which is optimized for control operations with extensive boolean processing capabilities. The 8x931 executes the standard instruction set of the MCS 51 architecture.

A functional block diagram of the 8x931 is shown in Figure 2-2. The 8x931 contains a microcontroller core, a USB module, a keyboard control interface, on-chip ROM (optional) and RAM, four 8-bit parallel ports, and on-chip peripherals (timer/counters and serial port). The USB module operates in conjunction with the CPU to provide the capabilities of a USB device. It supports all four types of USB data transfers: control, isochronous, interrupt, and bulk. Dedicated pinouts are provided for USB signals.

The 8x931 is available in ROMless and factory-programmed ROM versions in 64-pin S-DIP, 64-pin QFP, and 68-pin PLCC packages. See Appendix B for package diagrams, pin assignments, and signal descriptions. Table 2-1 lists the on-chip RAM and ROM memory options.

| 0-024 4 4                     | 0-024114                  | On-chip Memory  |                |  |

|-------------------------------|---------------------------|-----------------|----------------|--|

| 8 <i>x</i> 931AA<br>(Hubless) | 8 <i>x</i> 931HA<br>(Hub) | ROM<br>(Kbytes) | RAM<br>(Bytes) |  |

| 80931AA                       | 80931HA                   | 0               | 256            |  |

| 83931AA                       | 83931HA                   | 8               | 256            |  |

Table 2-1. 8x931 Memory Options

The 8x931 provides a rich set of microcontroller features. The following sections describe the major features. Table 2-2 on page 2-4 summarizes these features and provides an item-by-item comparison of the 8x930Hx and 8x931Hx and the 8x930Ax and 8x931Ax. The 8x931 is based on the MCS<sup>®</sup> 51 architecture, whereas the 8x930Hx is based on the MCS<sup>®</sup> 251 architecture.

For detailed description of the 8xC51Fx hardware, programmer's model, and instruction set, see the *MCS 51 Microcontroller Family User's Manual*, order number 272383.

For further information on the 8x931, see "Microcontroller Core" on page 2-6, and "Universal Serial Bus Module" on page 2-11.

#### 2.1.1 8x931AA Features

The 8x931AA provides a USB interface for one PC peripheral. The 8x931AA function interface provides three function endpoint pairs with corresponding transmit/receive FIFO pairs. Function endpoint 0 supports control data transfers only, while function endpoints 1 and 2 support control, interrupt, and bulk data transfers. Function endpoint 1, which has 16-byte FIFOs, also supports isochronous data transfers. See Table 2-5 on page 2-12 for endpoint pair information.

#### 2.1.2 8x931HA Features

The 8x931HA also provides a USB hub capability, permitting the connection of additional PC peripherals or hubs. In addition to an upstream port to the host PC (USB root port), the 8x931HA provides four external downstream ports (with ganged power switching), and an internal downstream port for the embedded function. The 8x931HA provides on-chip transceivers for each of the external USB ports.

The 8x931HA has two hub endpoint pairs: endpoint 0 which supports 8-byte control data transfers and endpoint 1 which transmits a status change byte to the host PC. See Table 2-2 for a summary of USB features and Table 2-5 on page 2-12 for endpoint pair information. See Figure 2-3 for the 8x931HA USB module block diagram.

#### NOTE

The 8x931AA microcontroller does not support hub operations. Specific details of the 8x931AA are covered in Appendix E, "8x931AA Design Considerations".

#### 2.1.3 Keyboard Control Interface

The 8x931 contains a keyboard control interface with a 20-bit by 8-bit scan capability and four LED drivers. Chapter 12, "Keyboard Control", describes this further.

|                                                                                | 8 <i>x</i> 931H <i>x</i> | 8 <i>x</i> 931A <i>x</i> | 8 <i>x</i> 930H <i>x</i> | 8 <i>x</i> 930A <i>x</i> |

|--------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| General Features                                                               |                          |                          |                          |                          |

| On-chip ROM                                                                    | 0, 8 Kbytes              | 0, 8 Kbytes              | 0, 8 or 16<br>Kbytes     | 0, 8 or 16<br>Kbytes     |

| On-chip RAM                                                                    | 256 bytes                | 256 bytes                | 1024 bytes               | 1024 bytes               |

| On-chip peripherals:                                                           |                          |                          |                          |                          |

| Timer/counters                                                                 | 3                        | 3                        | 3                        | 3                        |

| Serial I/O port                                                                | Yes                      | Yes                      | Yes                      | Yes                      |

| PCA, Hardware Watchdog Timer                                                   | No                       | No                       | Yes                      | Yes                      |

| Code compatible with MCS <sup>®</sup> 51 Microcontrollers                      | Yes                      | Yes                      | Yes                      | Yes                      |

| Code compatible with MCS <sup>®</sup> 251 Microcontrollers                     | No                       | No                       | Yes                      | Yes                      |

| Keyboard control interface                                                     | Yes                      | Yes                      | No                       | No                       |

| General USB Features                                                           |                          |                          |                          |                          |

| Complete <i>Universal Serial Bus Specification</i> ,<br>Rev. 1.0 compatibility | Yes                      | Yes                      | Yes                      | Yes                      |

| On-chip USB transceivers                                                       | Yes                      | Yes                      | Yes                      | Yes                      |

| Automatic transmit/receive FIFO management                                     | Yes                      | Yes                      | Yes                      | Yes                      |

| Time base (crystal/PLL)                                                        | 12 MHz                   | 12 MHz                   | 12 MHz                   | 12 MHz                   |

| USB rate (full speed)                                                          | 12 Mbps                  | 12 Mbps                  | 12 Mbps                  | 12 Mbps                  |

| Low-clock mode                                                                 | Yes                      | Yes                      | Yes                      | Yes                      |

| Suspend/resume                                                                 | Yes                      | Yes                      | Yes                      | Yes                      |

| USB interrupt vectors (hub, function, and<br>suspend/resume)                   | Yes                      | Yes                      | Yes                      | Yes                      |

| Reset Separation                                                               | Yes                      | Yes                      | No                       | Yes                      |

| 6 Endpoint Pair Option                                                         | No                       | No                       | No                       | Yes                      |

| JSB Function Features                                                          |                          |                          |                          |                          |