Technical Reference

# ScanLogic Corporation

4 Preston Court, Bedford, MA 01730 http://:www.scanlogic.com

©1996 - 1999 ScanLogic Corporation. All rights reserved. SL16 is a trademark of ScanLogic Corporation. The information and specifications contained in this document are subject to change without notice.

| 1.1       OVERVIEW       6         1.2       SL16 FEATURES       6         1.3       SL16 IN CREARAM       8         1.4       SL16 IN CREARAM       8         1.5       JKX16 MASK RÖM AND BIOS       8         1.6       INTERNAL RAM       9         1.7       CLOCK GENEEATOR       9         1.8       USB INTERFACE       9         1.9       PROCESSOR CONTROL REGISTERS       9         1.10       INTERFACE       9         1.11       UART INTERFACE       9         1.12       SERTERAL SKAMDORAM EPROM INTERFACE       9         1.13       EXTERNAL SKAMDORAM EPROM INTERFACE       9         1.14       GENERAL THARES AND WATCH DOG THERE       10         1.15       SECEAL OPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES       10         1.16       PROCRAMMABLE PULSEPPM INTERFACE       10         1.17       SL16 INTERFACE       10         1.18       REFERENCES       11         3.4       INTERFACE       13         4.1       INTERFACE       13         4.2       ENTERFACE       13         4.3       INTERFACE       13         4.4 <td< th=""><th>1.</th><th>INT</th><th>RODUCTION</th><th> 6</th></td<>                                                                                                                                                                                                                                               | 1. | INT  | RODUCTION                                | 6  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|------------------------------------------|----|

| 1.2       SL16 FEATURES       6         1.3       SL16 IG-BIT RISC PROCESSOR       8         1.4       SL16 IG-BIT RISC PROCESSOR       8         1.5       JRX16 MASK ROM AND BIOS       8         1.6       INTERNAL RAM       9         1.7       CLOCK GENERATOR       9         1.8       USB INTERFACE       9         1.9       PROCESSOR CONTROL REGISTERS       9         1.10       INTERRUPTS       9         1.11       UART INTERFACE       9         1.12       SERIAL FLASH EEPROM INTERFACE (I2C)       9         1.13       ENTERNAL SRAMORAMCER DOM INTERFACE       9         1.14       GENERAL TIMERS AND WATCH DOG TIMER       90         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES       10         1.16       PROCAMMABLE PULSE/PWM INTERFACE       10         1.17       SLIG INTERFACE       10         1.17       SLIG INTERFACE       10         1.10       REFERENCES       12         4.       INTERFACE       13         4.1       INTERFACE       13         4.2       ENTERNAL RAM: 0X0000-0X0FFFF       13         4.3       INTERNAL MASKED ROM: 0XEE00-0                                                                                                                                                                                                                                                                   |    | 1.1  | OVERVIEW                                 | 6  |

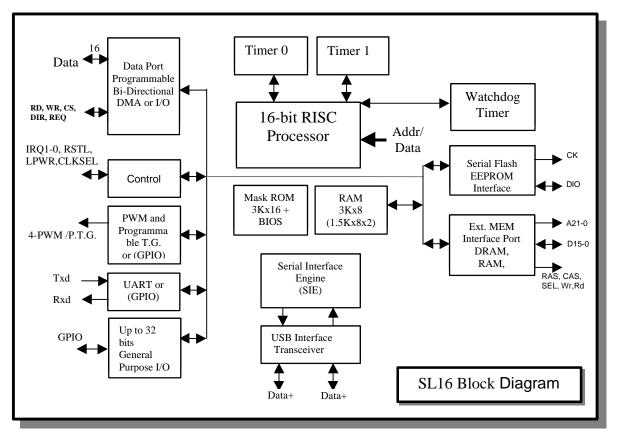

| 1.3       SL16 BLOCK DIAGRAM       8         1.4       SL16 IG-BIT RISC PROCESSOR       8         1.5       JKX16 MASK ROM AND BIOS       8         1.6       INTERNAL RAM       9         1.7       CLOCK GENERATOR       9         1.8       USB INTERACE       9         1.9       PROCESSOR CONTROL REGISTERS       9         1.10       INTERRUTS       9         1.11       UART INTERACE       9         1.12       SERIAL PLASH EFPROM INTERFACE (I2C)       9         1.13       EXTERNAL BRAM/DRAM/EPROM INTERFACE       9         1.14       GENERAL TIMES AND WATCH DOG TIMER       10         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RUSUME AND LOW POWER MODES       10         1.16       PROGRAMMABLE PULSP/WM INTERFACE       10         1.17       SL16 INTERFACE       10         1.18       REFERENCES       10         2.17       SL16 INTERFACE       10         3.18       INTERNAL RAM: COMO: 0XE800-0XFFFF       13         4.1       INTERNAL RAM: COMO: 0XCE800-0XFFFF       13         4.2       EXTERNAL RAM: COMO: 0XCE800-0XFFFF       13         4.3       INTERNAL RAM: COMO: 0XCE000-0XOFFFF       13                                                                                                                                                                                                                                               |    |      |                                          |    |

| 1.4       SL16 16-BIT RISC PROCESSOR.       8         1.5       3Kx16 MASK ROM AND BIOS.       8         1.6       INTERNAL RAM       9         1.7       CLOCK GENERATOR.       9         1.8       USB INTERACE.       9         1.9       PROCESSOR CONTROL REGISTERS.       9         1.10       INTERRUTTS.       9         1.11       UART INTERFACE.       9         1.12       SERIAL PLASH EEPROM INTERFACE (12C).       9         1.13       ENTERNAL SRAMDRAM/EPROM INTERFACE.       9         1.14       GENERAL TIMERS AND WATCH DOG TIMER.       10         1.15       SPECIAL GPIO PUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES.       10         1.16       PROGRAMMABLE PULSE/PWM INTERFACE.       10         1.17       SL16 INTERFACES.       10         1.18       INTERNAL MASKED ROM: 0XEB00-0XFFTF       13         4.1       INTERNAL MASKED ROM: 0XEB00-0XFFTF       13         4.2       EXTERNAL ROM: 0XC100-0XEB00       13         4.3       INTERNAL RAM: 0X0000-0XDFFTF       13         4.4       CLOCK GENERATOR       15         4.5.1       USB Formon Mone NO: 0XC100-0XEB00       13         4.5.1       USB Formon Mone Regi                                                                                                                                                                                                                       |    | 1.3  |                                          |    |

| 16       INTERNAL RAM.       9         17       CLOCK GENERATOR.       9         18       USB INTERACE.       9         19       PROCESSOR CONTROL REGISTERS.       9         10       INTERRUPTS.       9         111       UART INTERACE.       9         112       SERIAL FLASH EEPROM INTERFACE (12C).       9         113       EXTERNAL SRAM/DRAM/EPROM INTERFACE.       9         114       GENERAL TIMERS AND WATCH DOG TIMER.       10         115       SPECIAL GPIO FUNCTION FOR SUSPEND, RISUME AND LOW POWER MODES.       10         116       PROGRAMMABLE PULSE/PWM INTERFACE.       10         117       SLI6 INTERFACES.       10         12.       DEFINITIONS.       11         3.       REFERENCES       12         4.       INTERNAL MASKED ROM: 0XEB00-0XFFFF       13         4.1       INTERNAL MASKED ROM: 0XEB00-0XFFFF       13         4.2       EXTERNAL ROM: 0XC100-0XEB00       13         4.3       INTERNAL RAM: 0X0000-0XDFFF       13         4.4       CLOCK GENERATOR.       15         4.5.1       USB INTERFACE       15         4.5.1       USB INTERFACE.       15         4.5.4                                                                                                                                                                                                                                                                    |    | 1.4  | SL16 16-BIT RISC PROCESSOR               | 8  |

| 1.7       CLOCK GENERATOR       9         1.8       USB INTERPACE       9         1.9       PROCESSOR CONTROL REGISTERS       9         1.10       INTERRUPTS.       9         1.11       UART INTERRACE       9         1.12       SERIAL FLASH EEPROM INTERFACE (12C).       9         1.13       EXTERNAL SRAM/DRAM/EPROM INTERFACE       9         1.14       GENERAL TIMERS AND WATCH DOG TIMER       10         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES.       10         1.16       PROCEAMMABLE PULSE/PWIN INTERFACE       10         1.17       SL16 INTERFACES: SL16 MODE AND GPIO MODE       10         2.       DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 1.5  | 3Kx16 MASK ROM AND BIOS                  | 8  |

| 1.8       USB INTERFACE       9         1.9       PROCESSOR CONTROL REGISTERS       9         1.10       INTERRUTTS       9         1.11       UART INTERACE       9         1.12       SERIAL FLASH EEPROM INTERFACE (12C).       9         1.13       EXTERNAL SRAM/DRAM/EPROM INTERFACE.       9         1.14       GENERAL TIMERS AND WATCH DOG TIMER.       10         1.15       SPECIAL GPIO FUNCTOR FOR SUSPEND, RESUME AND LOW POWER MODES.       10         1.16       PROGRAMMABLE PULSE/PWM INTERFACE.       10         1.17       SL16 INTERFACES: SL16 MODE AND GPIO MODE       10         2.       DEFINITIONS       11         3.       REFERENCES       12         4.       INTERNAL RAM: 0X0000-0XEB00.       13         4.1       INTERNAL RAM: 0X0000-0XEB00.       13         4.2       EXTERNAL RAM: 0X0000-0XDDFF       14         4.4       CLOCK GENERATION       15         4.5.1       USB Global Control & Status Register (0XC080: R/W).       16         4.5.2       USB Address Register (0XC081: R/W).       16         4.5.4       USB Address Register (0XC081: R/W).       17         4.5.5       USB Endpoint 0 Control & Status Register (0XC090: R/W).       17 <td></td> <td>1.6</td> <td>INTERNAL RAM</td> <td> 9</td>                                                                                                                               |    | 1.6  | INTERNAL RAM                             | 9  |

| 1.9       PROCESSOR CONTROL REGISTERS       9         1.10       INTERRUPTS       9         1.11       UART INTERFACE       9         1.12       SERIAL FLASH EEPROM INTERFACE (12C)       9         1.13       EXTERNAL SRAM/DRAM/EPROM INTERFACE       9         1.14       GENERAL TIMERS AND WATCH DOG TIMER       10         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RISUME AND LOW POWER MODES       10         1.16       PROGRAMMABLE PULSEP/WM INTERFACE       10         1.17       SLI6 INTERFACES: SLI6 MODE AND GPIO MODE       10         2.       DEFINITIONS       11         3.       REFERENCES       12         4.1       INTERNAL MASKED ROM: 0XE800-0XFFFF       13         4.2       EXTERNAL ROM: 0XC100-0XE800-0XFFFF       13         4.3       INTERNAL RAM: 0X0000-0XDFFF       14         4.4       CLOCK GENERATOR       15         4.5       USB INTERFACE       15         4.5.1       USB Global Control & Status Register (0xC080: R/W)       16         4.5.3       USB LODOL Control & Status Register (0xC080: R/W)       16         4.5.4       USB Endpoint 1 Control & Status Register (0xC090: R/W)       17         4.5.4       USB Endpoint 2 Control & Status Reg                                                                                                                                                                           |    | 1.7  | CLOCK GENERATOR                          | 9  |

| 1.10       INTERRATE       9         1.11       UART INTERFACE       9         1.12       SERIAL FLASH EEPROM INTERFACE (I2C).       9         1.13       EXTERNAL, SRAM/DRAM/EPROM INTERFACE.       9         1.14       GENERAL TIMERS AND WATCH DOG TIMER.       10         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES.       10         1.16       PROGRAMMABLE PULSE/PWM INTERFACE.       10         1.17       SLI6 INTERFACES: SLI6 MODE AND GPIO MODE       10         2.       DEFINITIONS.       11         3.       REFERENCES       12         4.       INTERNAL MASKED ROM: 0XE800-0XFFFF       13         4.1       INTERNAL RAM: 0X0000-0X0DFF.       14         4.4       CLOCK GENRATOR       15         4.5.1       USB INTERFACE       15         4.5.1       USB INTERFACE       15         4.5.1       USB INTERFACE       16         4.5.2       USB INTERFACE       15         4.5.3       USB Address Register (0XC080: RW)       16         4.5.4       USB Command Dome Register (0XC080: RW)       16         4.5.4       USB Endpoint 1 Control & Status Register (0XC092: RW)       17         4.5.4 <tdu< td=""><td></td><td>1.8</td><td>USB INTERFACE</td><td> 9</td></tdu<>                                                                                                                                                    |    | 1.8  | USB INTERFACE                            | 9  |

| 1.11       UART INTERFACE       9         1.12       SERIAL FLASH EEPROM INTERFACE (I2C)       9         1.13       EXTERNAL SRAMDRAM/EPROM INTERFACE       9         1.14       GENERAL TIMERS AND WATCH DOG TIMER       10         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES       10         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES       10         1.17       SL16 INTERFACES: SL16 MODE AND GPIO MODE       10         2.       DEFINITIONS       11         3.       REFERENCES       12         4.       INTERFACE       13         4.1       INTERNAL MASKED ROM: 0XE800-0XFFFF       13         4.2       EXTERNAL RAM: 0X0000-0X0DFF       14         4.3       INTERNAL RAM: 0X0000-0X0DFF       14         4.4       CLOCK GENERATOR       15         4.5.1       USB INTERFACE       15         4.5.1       USB Global Control & Status Register (0XC080: RW)       16         4.5.3       USB Address Register (0XC082: Read Only)       16         4.5.3       USB Address Register (0XC080: Write Only)       17         4.5.4       USB Control & Status Register (0XC090: RW)       17         4.5.5       USB Endpoint 1 Cont                                                                                                                                                                           |    | 1.9  | PROCESSOR CONTROL REGISTERS              | 9  |

| 1.12       SERIAL FLASH EEPROM INTERFACE (12C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 1.10 | INTERRUPTS                               | 9  |

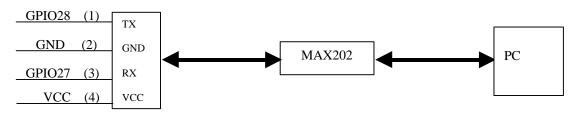

| 1.13       EXTERNAL SRAM/DRAM/EPROM INTERFACE.       9         1.14       GENERAL TIMEES AND WATCH DOG TIMER.       10         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES.       10         1.16       PROGRAMMABLE PULSE/PWM INTERFACE.       10         1.17       SL16 INTERFACES: SL16 MODE AND GPIO MODE       10         2.       DEFINITIONS.       11         3.       REFERENCES       12         4.       INTERFACE       13         4.1       INTERFACE       13         4.2       EXTERNAL ROM: 0XE800-0XFFFF       13         4.3       INTERNAL RAM 0X00000-0x0DFF       14         4.4       CLOCK GENERATOR       15         4.5.1       USB INTERFACE       15         4.5.1       USB Control & Status Register (0xC080: RW)       16         4.5.2       USB INTERFACE       15         4.5.1       USB Control & Status Register (0xC080: RW)       16         4.5.2       USB B Indopini 0 Control & Status Register (0xC090: RW)       16         4.5.4       USB Control & Status Register (0xC090: RW)       17         4.5.5       USB Endpoini 1 Control & Status Register (0xC090: RW)       17         4.5.5       USB Endpoini 2 Control & Status Regis                                                                                                                                                                           |    | 1.11 |                                          |    |

| 1.14       GENERAL TIMERS AND WATCH DOG TIMER.       10         1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES.       10         1.16       PROGRAMMABLE PULSE/PWM INTERFACE.       10         1.17       SL16 INTERFACES: SL16 MODE AND GPIO MODE.       10         2.       DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 1.12 |                                          |    |

| 1.15       SPECIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES       10         1.16       PROGRAMMABLE PULSE/PWM INTERFACE       10         1.17       SL16 INTERFACES: SL16 MODE AND GPIO MODE       10         2.       DEFINITIONS       11         3.       REFERENCES       12         4.       INTERFACE       13         4.1       INTERFACE       13         4.2       EXTERNAL ROM: 0xC100-0xE800.       13         4.3       INTERNAL RAM: 0x0000-0xDFFF.       14         4.4       CLOCK GENERATOR       15         4.5       USB INTERFACE       15         4.5.1       USB Global Control & Status Register (0xC080: R/W).       16         4.5.2       USB B Global Control & Status Register (0xC080: R/W).       16         4.5.3       USB Address Register (0xC082: Read Only)       16         4.5.4       USB Command Done Register (0xC080: R/W).       17         4.5.5       USB Endpoint 1 Control & Status Register (0xC090: R/W).       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC090: R/W).       17         4.5.7       USB Endpoint 1 Control & Status Register (0xC090: R/W).       17         4.5.9       USB Endpoint 1 Control & Status Register (0xC090: R/W).       17                                                                                                                                              |    | 1.13 |                                          |    |

| 1.16       PROGRAMMABLE PULSE/PWM INTERFACE.       10         1.17       SL16 INTERFACES: SL16 MODE AND GPIO MODE       10         2.       DEFINITIONS.       11         3.       REFERENCES       12         4.       INTERFACE       13         4.1       INTERFACE       13         4.2       EXTERNAL ROM: 0XC100-0XE800.       13         4.3       INTERNAL RAM: 0X0000-0XDFFF       13         4.4       CLOCK GENERATOR.       15         4.5       USB INTERFACE       15         4.5       USB Global Control & Status Register (0xC080: R/W).       16         4.5.1       USB Cobal Control & Status Register (0xC080: R/W).       16         4.5.2       USB Fadpoint 0 Control & Status Register (0xC090: R/W).       17         4.5.4       USB Command Done Register (0xC082: Read Only)       16         4.5.5       USB Endpoint 1 Control & Status Register (0xC090: R/W).       17         4.5.6       USB Endpoint 2 Control & Status Register (0xC092: R/W).       17         4.5.7       USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.8       USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.9       USB Endpoint 0 Address Register (0xC092: R/W).       17 <td></td> <td>1.14</td> <td></td> <td></td>                                                                                               |    | 1.14 |                                          |    |

| 1.17       SL16 INTERFACES: SL16 MODE AND GPIO MODE       10         2.       DEFINITIONS       11         3.       REFERENCES       12         4.       INTERFACE       13         4.1       INTERFACE       13         4.2       EXTERNAL ROM: 0XE800-0XFFFF       13         4.3       INTERNAL RAM: 0X0000-0XE800       13         4.4       CLOCK GENERATOR       14         4.4       CLOCK GENERATOR       15         4.5.1       USB INTERFACE       15         4.5.1       USB INTERFACE       16         4.5.2       USB Frame Number Register (0xC080: RW)       16         4.5.2       USB Address Register (0xC084: RW)       16         4.5.2       USB Endpoint 0 Control & Status Register (0xC090: RW)       17         4.5.5       USB Endpoint 1 Control & Status Register (0xC090: RW)       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC090: RW)       17         4.5.7       USB Endpoint 3 Control & Status Register (0xC092: RW)       17         4.5.8       USB Endpoint 3 Control & Status Register (0xC092: RW)       17         4.5.9       USB Endpoint 3 Control & Status Register (0xC092: RW)       17         4.5.10       USB Endpoint 1 Address Regist                                                                                                                                                                           |    | 1.15 |                                          |    |

| 2. DEFINITIONS.       11         3. REFERENCES.       12         4. INTERFACE       13         4.1 INTERNAL MASKED ROM: 0XE800-0XFFFF.       13         4.2 EXTERNAL ROM: 0XC100-0XE800.       13         4.3 INTERNAL RAM: 0X0000-0XDFF.       14         4.4 CLOCK GENERATOR.       15         4.5.1 USB Global Control & Status Register (0XC080: RW).       16         4.5.2 USB Frame Number Register (0XC080: RW).       16         4.5.3 USB Address Register (0XC080: RW).       16         4.5.4 USB Forme Number Register (0XC080: Write Only).       17         4.5.5 USB Endpoint 0 Control & Status Register (0XC090: RW).       17         4.5.5 USB Endpoint 2 Control & Status Register (0XC092: RW).       17         4.5.6 USB Endpoint 2 Control & Status Register (0XC092: RW).       17         4.5.7 USB Endpoint 2 Control & Status Register (0XC092: RW).       17         4.5.8 USB Endpoint 3 Control & Status Register (0XC092: RW).       17         4.5.8 USB Endpoint 3 Control & Status Register (0XC092: RW).       17         4.5.10 USB Endpoint 1 Address Register (0X0120: RW).       18         4.5.11 USB Endpoint 1 Address Register (0X0122: RW).       19         4.5.13 USB Endpoint 1 Count Register (0X0122: RW).       19         4.5.14 USB Endpoint 1 Count Register (0X0122: RW).       19                                                   |    | 1.16 |                                          |    |

| 3. REFERENCES       12         4. INTERFACE       13         4.1 INTERNAL MASKED ROM: 0xE800-0xFFFF       13         4.2 EXTERNAL ROM: 0xC100-0xE800.       13         4.3 INTERNAL RAM: 0x0000-0x0DFF.       14         4.4 CLOCK GENERATOR.       15         4.5 USB INTERFACE.       15         4.5 USB Frame Number Register (0xC080: R/W).       16         4.5.2 USB Frame Number Register (0xC082: Read Only).       16         4.5.3 USB Address Register (0xC084: R/W).       16         4.5.4 USB Command Done Register (0xC080: Write Only).       17         4.5.5 USB Endpoint 0 Control & Status Register (0xC090: R/W).       17         4.5.6 USB Endpoint 1 Control & Status Register (0xC090: R/W).       17         4.5.7 USB Endpoint 1 Control & Status Register (0xC090: R/W).       17         4.5.7 USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.8 USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.9 USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.9 USB Endpoint 1 Control & Status Register (0xC020: R/W).       17         4.5.9 USB Endpoint 1 Control & Status Register (0x0122: R/W).       18         4.5.11 USB Endpoint 1 Address Register (0x0122: R/W).       18         4.5.13 USB Endpoint 1 Count Register (0x0122: R/W).                                  |    | 1.17 | SL16 INTERFACES: SL16 MODE AND GPIO MODE | 10 |

| 3. REFERENCES       12         4. INTERFACE       13         4.1 INTERNAL MASKED ROM: 0xE800-0xFFFF       13         4.2 EXTERNAL ROM: 0xC100-0xE800.       13         4.3 INTERNAL RAM: 0x0000-0x0DFF.       14         4.4 CLOCK GENERATOR.       15         4.5 USB INTERFACE.       15         4.5 USB Frame Number Register (0xC080: R/W).       16         4.5.2 USB Frame Number Register (0xC082: Read Only).       16         4.5.3 USB Address Register (0xC084: R/W).       16         4.5.4 USB Command Done Register (0xC080: Write Only).       17         4.5.5 USB Endpoint 0 Control & Status Register (0xC090: R/W).       17         4.5.6 USB Endpoint 1 Control & Status Register (0xC090: R/W).       17         4.5.7 USB Endpoint 1 Control & Status Register (0xC090: R/W).       17         4.5.7 USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.8 USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.9 USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.9 USB Endpoint 1 Control & Status Register (0xC020: R/W).       17         4.5.9 USB Endpoint 1 Control & Status Register (0x0122: R/W).       18         4.5.11 USB Endpoint 1 Address Register (0x0122: R/W).       18         4.5.13 USB Endpoint 1 Count Register (0x0122: R/W).                                  | 2  | DFI  | TINITIONS                                | 11 |

| 4. INTERFACE       13         4.1 INTERNAL MASKED ROM: 0xE800-0xFFFF       13         4.2 EXTERNAL ROM: 0xC100-0xE800.       13         4.3 INTERNAL RAM: 0x0000-0x0DFF.       14         4.4 CLOCK GENERATOR.       15         4.5 USB INTERFACE       15         4.5 USB INTERFACE       16         4.5.1 USB Global Control & Status Register (0xC080: R/W).       16         4.5.2 USB Frame Number Register (0xC082: Read Only)       16         4.5.3 USB Address Register (0xC084: R/W).       16         4.5.4 USB Command Done Register (0xC086: Write Only)       17         4.5.5 USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.6 USB Endpoint 2 Control & Status Register (0xC092: R/W).       17         4.5.7 USB Endpoint 2 Control & Status Register (0xC092: R/W).       17         4.5.8 USB Endpoint 2 Control & Status Register (0xC092: R/W).       17         4.5.9 USB Endpoint 2 Control & Status Register (0xC096: R/W).       17         4.5.10 USB Endpoint 2 Control & Status Register (0xC092: R/W).       18         4.5.11 USB Endpoint 1 Address Register (0x0126: R/W).       18         4.5.10 USB Endpoint 1 Count Register (0x0126: R/W).       19         4.5.13 USB Endpoint 1 Address Register (0x0126: R/W).       19         4.5.14 USB Endpoint 1 Count Register (0x0126: R/W).                                     | 4. | DEI  |                                          | 11 |

| 4. INTERFACE       13         4.1 INTERNAL MASKED ROM: 0xE800-0xFFFF       13         4.2 EXTERNAL ROM: 0xC100-0xE800.       13         4.3 INTERNAL RAM: 0x0000-0x0DFF.       14         4.4 CLOCK GENERATOR.       15         4.5 USB INTERFACE       15         4.5 USB INTERFACE       16         4.5.1 USB Global Control & Status Register (0xC080: R/W).       16         4.5.2 USB Frame Number Register (0xC082: Read Only)       16         4.5.3 USB Address Register (0xC084: R/W).       16         4.5.4 USB Command Done Register (0xC086: Write Only)       17         4.5.5 USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.6 USB Endpoint 2 Control & Status Register (0xC092: R/W).       17         4.5.7 USB Endpoint 2 Control & Status Register (0xC092: R/W).       17         4.5.8 USB Endpoint 2 Control & Status Register (0xC092: R/W).       17         4.5.9 USB Endpoint 2 Control & Status Register (0xC096: R/W).       17         4.5.10 USB Endpoint 2 Control & Status Register (0xC092: R/W).       18         4.5.11 USB Endpoint 1 Address Register (0x0126: R/W).       18         4.5.10 USB Endpoint 1 Count Register (0x0126: R/W).       19         4.5.13 USB Endpoint 1 Address Register (0x0126: R/W).       19         4.5.14 USB Endpoint 1 Count Register (0x0126: R/W).                                     | 3  | REF  | TERENCES                                 | 12 |

| 4.1       INTERNAL MASKED ROM: 0xE800-0xFFFF       13         4.2       EXTERNAL ROM: 0xC100-0xE800       13         4.3       INTERNAL RAM: 0x0000-0x0DFF       14         4.4       CLOCK GENERATOR       15         4.5       USB INTERFACE       15         4.5       USB Global Control & Status Register (0xC080: R/W)       16         4.5.2       USB Frame Number Register (0xC082: Read Only)       16         4.5.3       USB Address Register (0xC084: R/W)       16         4.5.4       USB Control & Status Register (0xC090: R/W)       16         4.5.5       USB Endpoint 0 Control & Status Register (0xC090: R/W)       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC090: R/W)       17         4.5.7       USB Endpoint 2 Control & Status Register (0xC090: R/W)       17         4.5.8       USB Endpoint 1 Control & Status Register (0xC090: R/W)       17         4.5.9       USB Endpoint 1 Address Register (0x0120: R/W)       18         4.5.10       USB Endpoint 1 Address Register (0x0124: R/W)       18         4.5.11       USB Endpoint 1 Address Register (0x0122: R/W)       19         4.5.14       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.15       USB Endpoint 1 Count Register (0x0122: R/W)       19<                                                                                            | 5. | NL1  |                                          | 14 |

| 4.1       INTERNAL MASKED ROM: 0xE800-0xFFFF       13         4.2       EXTERNAL ROM: 0xC100-0xE800       13         4.3       INTERNAL RAM: 0x0000-0x0DFF       14         4.4       CLOCK GENERATOR       15         4.5       USB INTERFACE       15         4.5       USB Global Control & Status Register (0xC080: R/W)       16         4.5.2       USB Frame Number Register (0xC082: Read Only)       16         4.5.3       USB Address Register (0xC084: R/W)       16         4.5.4       USB Control & Status Register (0xC090: R/W)       16         4.5.5       USB Endpoint 0 Control & Status Register (0xC090: R/W)       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC090: R/W)       17         4.5.7       USB Endpoint 2 Control & Status Register (0xC090: R/W)       17         4.5.8       USB Endpoint 1 Control & Status Register (0xC090: R/W)       17         4.5.9       USB Endpoint 1 Address Register (0x0120: R/W)       18         4.5.10       USB Endpoint 1 Address Register (0x0124: R/W)       18         4.5.11       USB Endpoint 1 Address Register (0x0122: R/W)       19         4.5.14       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.15       USB Endpoint 1 Count Register (0x0122: R/W)       19<                                                                                            | 4  | INT  | FRFACE                                   | 13 |

| 4.2       EXTERNAL ROM: 0xC100-0xE800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |      |                                          |    |

| 4.3       INTERNAL RAM: 0x0000-0x0DFF.       14         4.4       CLOCK GENERATOR.       15         4.5       USB INTERFACE.       15         4.5.1       USB Global Control & Status Register (0xC080: R/W).       16         4.5.2       USB Frame Number Register (0xC082: Read Only)       16         4.5.3       USB Address Register (0xC084: R/W).       16         4.5.4       USB Command Done Register (0xC086: Write Only)       17         4.5.5       USB Endpoint 0 Control & Status Register (0xC090: R/W).       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC092: R/W).       17         4.5.7       USB Endpoint 2 Control & Status Register (0xC094: R/W).       17         4.5.8       USB Endpoint 3 Control & Status Register (0xC094: R/W).       17         4.5.8       USB Endpoint 1 Control & Status Register (0xC094: R/W).       17         4.5.8       USB Endpoint 1 Address Register (0x0120: R/W).       18         4.5.10       USB Endpoint 1 Address Register (0x0122: R/W).       18         4.5.11       USB Endpoint 1 Address Register (0x0122: R/W).       19         4.5.13       USB Endpoint 1 Count Register (0x0122: R/W).       19         4.5.14       USB Endpoint 1 Count Register (0x0122: R/W).       19         4.5.15       U                                                                                   |    |      |                                          | -  |

| 4.4       CLOCK GENERATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |                                          |    |

| 4.5       USB INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |      |                                          |    |

| 4.5.1       USB Global Control & Status Register (0xC080: R/W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      |                                          |    |

| 4.5.2       USB Frame Number Register (0xC082: Read Only)       16         4.5.3       USB Address Register (0xC084: R/W)       16         4.5.4       USB Command Done Register (0xC086: Write Only)       17         4.5.5       USB Endpoint 0 Control & Status Register (0xC090: R/W)       17         4.5.5       USB Endpoint 1 Control & Status Register (0xC090: R/W)       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC092: R/W)       17         4.5.7       USB Endpoint 2 Control & Status Register (0xC090: R/W)       17         4.5.8       USB Endpoint 3 Control & Status Register (0xC090: R/W)       17         4.5.9       USB Endpoint 1 Address Register (0x0120: R/W)       18         4.5.10       USB Endpoint 1 Address Register (0x0128: R/W)       18         4.5.11       USB Endpoint 3 Address Register (0x0122: R/W)       19         4.5.12       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.14       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.15       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.15       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.15       USB Endpoint 1 Count Register (0x0126: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x0026: R/W) <t< td=""><td></td><td></td><td></td><td></td></t<> |    |      |                                          |    |

| 4.5.3       USB Address Register (0xC084: R/W)       16         4.5.4       USB Command Done Register (0xC086: Write Only)       17         4.5.5       USB Endpoint 0 Control & Status Register (0xC090: R/W)       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC092: R/W)       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC092: R/W)       17         4.5.7       USB Endpoint 2 Control & Status Register (0xC094: R/W)       17         4.5.8       USB Endpoint 3 Control & Status Register (0xC096: R/W)       17         4.5.9       USB Endpoint 1 Address Register (0x0120: R/W)       18         4.5.10       USB Endpoint 1 Address Register (0x0122: R/W)       18         4.5.11       USB Endpoint 2 Address Register (0x0122: R/W)       19         4.5.12       USB Endpoint 3 Address Register (0x0122: R/W)       19         4.5.13       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.14       USB Endpoint 1 Count Register (0x0126: R/W)       19         4.5.15       USB Endpoint 2 Count Register (0x0122: R/W)       19         4.5.16       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.15       USB Endpoint 3 Count Register (0x004: Read Only)       19         4.6.1       Version Address Register (0xC004: Read Only)                                               |    |      |                                          |    |

| 4.5.4       USB Command Done Register (0xC086: Write Only)       17         4.5.5       USB Endpoint 0 Control & Status Register (0xC090: R/W)       17         4.5.6       USB Endpoint 1 Control & Status Register (0xC092: R/W)       17         4.5.7       USB Endpoint 2 Control & Status Register (0xC094: R/W)       17         4.5.7       USB Endpoint 2 Control & Status Register (0xC096: R/W)       17         4.5.8       USB Endpoint 3 Control & Status Register (0xC096: R/W)       17         4.5.9       USB Endpoint 1 Address Register (0x0120: R/W)       18         4.5.10       USB Endpoint 2 Address Register (0x0124: R/W)       18         4.5.11       USB Endpoint 3 Address Register (0x0122: R/W)       19         4.5.12       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.14       USB Endpoint 1 Count Register (0x0126: R/W)       19         4.5.15       USB Endpoint 2 Count Register (0x0126: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W)       19         4.6.1       Version Address Register (0xC004: Read Only)       19         4.6.1       Version Address Register (0xC006: R/W)       20         4.6.3       Speed Control Register (0xC006: R/W)       20<                                                |    |      |                                          |    |

| 4.5.5       USB Endpoint 0 Control & Status Register (0xC090: R/W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |                                          |    |

| 4.5.6       USB Endpoint 1 Control & Status Register (0xC092: R/W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |                                          |    |

| 4.5.7       USB Endpoint 2 Control & Status Register (0xC094: R/W).       17         4.5.8       USB Endpoint 3 Control & Status Register (0xC096: R/W).       17         4.5.9       USB Endpoint 0 Address Register (0x0120: R/W).       18         4.5.10       USB Endpoint 1 Address Register (0x0124: R/W).       18         4.5.11       USB Endpoint 2 Address Register (0x0128: R/W).       19         4.5.12       USB Endpoint 3 Address Register (0x0120: R/W).       19         4.5.13       USB Endpoint 1 Count Register (0x0122: R/W).       19         4.5.14       USB Endpoint 1 Count Register (0x0126: R/W).       19         4.5.15       USB Endpoint 2 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W).       19         4.6.1       Version Address Register (0xC004: Read Only).       19         4.6.1       Version Address Register (0xC006: R/W).       20         4.6.3       Speed Control Register (0xC008: R/W).       21         4.6.4       Power Down Control Register (0xC008: R/W).       22                                                                 |    |      | 1                                        |    |

| 4.5.8       USB Endpoint 3 Control & Status Register (0xC096: R/W).       17         4.5.9       USB Endpoint 0 Address Register (0x0120: R/W).       18         4.5.10       USB Endpoint 1 Address Register (0x0124: R/W).       18         4.5.11       USB Endpoint 2 Address Register (0x0128: R/W).       19         4.5.12       USB Endpoint 3 Address Register (0x0122: R/W).       19         4.5.13       USB Endpoint 0 Count Register (0x0122: R/W).       19         4.5.14       USB Endpoint 1 Count Register (0x0126: R/W).       19         4.5.15       USB Endpoint 2 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0126: R/W).       19         4.6.1       Version Address Register (0x004: Read Only).       19         4.6.1       Version Address Register (0xC004: Read Only).       19         4.6.3       Speed Control Register (0xC008: R/W).       20         4.6.4       Power Down Control Register (0xC008: R/W).       22         4.6.5       Breakpoint Register (0xC014: R/W).       22 <t< td=""><td></td><td></td><td></td><td></td></t<>                             |    |      |                                          |    |

| 4.5.9       USB Endpoint 0 Address Register (0x0120: R/W)       18         4.5.10       USB Endpoint 1 Address Register (0x0124: R/W)       18         4.5.11       USB Endpoint 2 Address Register (0x0128: R/W)       19         4.5.12       USB Endpoint 3 Address Register (0x012C: R/W)       19         4.5.13       USB Endpoint 0 Count Register (0x012C: R/W)       19         4.5.14       USB Endpoint 1 Count Register (0x0126: R/W)       19         4.5.15       USB Endpoint 2 Count Register (0x012A: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x012E: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x012E: R/W)       19         4.6.1       Version Address Register (0xC004: Read Only)       19         4.6.1       Version Address Register (0xC006: R/W)       20         4.6.3       Speed Control Register (0xC008: R/W)       21         4.6.4       Power Down Control Register (0xC008: R/W)       22         4.6.5       Breakpoint Register (0xC014: R/W)       22         4.6.5       Breakpoint Register (0xC014: R/W)       22         4.6.7       INTERRUPTS       23         4.7.1       Hardware Interrupts       23                                                                                                                                                                                       |    |      |                                          |    |

| 4.5.10       USB Endpoint 1 Address Register (0x0124: R/W)       18         4.5.11       USB Endpoint 2 Address Register (0x0128: R/W)       19         4.5.12       USB Endpoint 3 Address Register (0x012C: R/W)       19         4.5.13       USB Endpoint 0 Count Register (0x0122: R/W)       19         4.5.14       USB Endpoint 1 Count Register (0x0122: R/W)       19         4.5.15       USB Endpoint 1 Count Register (0x0126: R/W)       19         4.5.16       USB Endpoint 2 Count Register (0x0128: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x0128: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x0128: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x0128: R/W)       19         4.6.1       Version Address Register (0x004: Read Only)       19         4.6.1       Version Address Register (0xC004: Read Only)       19         4.6.2       Configuration Register (0xC006: R/W)       20         4.6.3       Speed Control Register (0xC008: R/W)       21         4.6.4       Power Down Control Register (0xC008: R/W)       22         4.6.5       Breakpoint Register (0xC014: R/W)       22         4.7       INTERRUPTS       23         4.7.1       Hardware Interrupts       23 </td <td></td> <td></td> <td></td> <td></td>                                                           |    |      |                                          |    |

| 4.5.11       USB Endpoint 2 Address Register (0x0128: R/W).       19         4.5.12       USB Endpoint 3 Address Register (0x012C: R/W).       19         4.5.13       USB Endpoint 0 Count Register (0x0122: R/W).       19         4.5.14       USB Endpoint 1 Count Register (0x0126: R/W).       19         4.5.15       USB Endpoint 2 Count Register (0x0126: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x0124: R/W).       19         4.5.16       USB Endpoint 3 Count Register (0x012E: R/W).       19         4.6       PROCESSOR CONTROL REGISTERS       19         4.6.1       Version Address Register (0xC004: Read Only).       19         4.6.2       Configuration Register (0xC006: R/W).       20         4.6.3       Speed Control Register (0xC008: R/W).       21         4.6.4       Power Down Control Register (0xC00A: R/W).       22         4.6.5       Breakpoint Register (0xC014: R/W).       22         4.6.5       Breakpoint Register (0xC014: R/W).       22         4.6.5       Breakpoint Register (0xC014: R/W).       22         4.7       INTERRUPTS.       23         4.7.1       Hardware Interrupts.       23                                                                                                                                                                                                            |    |      |                                          |    |

| 4.5.12       USB Endpoint 3 Address Register (0x012C: R/W)       19         4.5.13       USB Endpoint 0 Count Register (0x0122: R/W)       19         4.5.14       USB Endpoint 1 Count Register (0x0126: R/W)       19         4.5.15       USB Endpoint 2 Count Register (0x012A: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x012E: R/W)       19         4.6       PROCESSOR CONTROL REGISTERS       19         4.6.1       Version Address Register (0xC004: Read Only)       19         4.6.2       Configuration Register (0xC006: R/W)       20         4.6.3       Speed Control Register (0xC008: R/W)       21         4.6.4       Power Down Control Register (0xC004: R/W)       22         4.6.5       Breakpoint Register (0xC014: R/W)       22         4.7       INTERRUPTS       23         4.7.1       Hardware Interrupts       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      |                                          |    |

| 4.5.13       USB Endpoint 0 Count Register (0x0122: R/W).       19         4.5.14       USB Endpoint 1 Count Register (0x0126: R/W).       19         4.5.15       USB Endpoint 2 Count Register (0x012A: R/W)       19         4.5.16       USB Endpoint 3 Count Register (0x012E: R/W)       19         4.6       PROCESSOR CONTROL REGISTERS       19         4.6.1       Version Address Register (0xC004: Read Only)       19         4.6.2       Configuration Register (0xC006: R/W).       20         4.6.3       Speed Control Register (0xC008: R/W)       21         4.6.4       Power Down Control Register (0xC004: R/W)       22         4.6.5       Breakpoint Register (0xC014: R/W)       22         4.6.7       INTERRUPTS.       23         4.7.1       Hardware Interrupts.       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |      |                                          |    |

| 4.5.14       USB Endpoint 1 Count Register (0x0126: R/W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |      |                                          |    |

| 4.5.15USB Endpoint 2 Count Register (0x012A: R/W)194.5.16USB Endpoint 3 Count Register (0x012E: R/W)194.6PROCESSOR CONTROL REGISTERS194.6.1Version Address Register (0xC004: Read Only)194.6.2Configuration Register (0xC006: R/W)204.6.3Speed Control Register (0xC008: R/W)214.6.4Power Down Control Register (0xC004: R/W)224.6.5Breakpoint Register (0xC014: R/W)224.7INTERRUPTS234.7.1Hardware Interrupts23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |      |                                          |    |

| 4.5.16USB Endpoint 3 Count Register (0x012E: R/W)194.6PROCESSOR CONTROL REGISTERS194.6.1Version Address Register (0xC004: Read Only)194.6.2Configuration Register (0xC006: R/W)204.6.3Speed Control Register (0xC008: R/W)214.6.4Power Down Control Register (0xC00A: R/W)224.6.5Breakpoint Register (0xC014: R/W)224.7INTERRUPTS234.7.1Hardware Interrupts23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      |                                          |    |

| 4.6       PROCESSOR CONTROL REGISTERS       19         4.6.1       Version Address Register (0xC004: Read Only)       19         4.6.2       Configuration Register (0xC006: R/W)       20         4.6.3       Speed Control Register (0xC008: R/W)       21         4.6.4       Power Down Control Register (0xC00A: R/W)       22         4.6.5       Breakpoint Register (0xC014: R/W)       22         4.7       INTERRUPTS       23         4.7.1       Hardware Interrupts       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |                                          |    |

| 4.6.1       Version Address Register (0xC004: Read Only)       19         4.6.2       Configuration Register (0xC006: R/W)       20         4.6.3       Speed Control Register (0xC008: R/W)       21         4.6.4       Power Down Control Register (0xC00A: R/W)       22         4.6.5       Breakpoint Register (0xC014: R/W)       22         4.7       INTERRUPTS       23         4.7.1       Hardware Interrupts       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |                                          |    |

| 4.6.2Configuration Register (0xC006: R/W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |                                          |    |

| 4.6.3       Speed Control Register (0xC008: R/W)       21         4.6.4       Power Down Control Register (0xC00A: R/W)       22         4.6.5       Breakpoint Register (0xC014: R/W)       22         4.7       INTERRUPTS       23         4.7.1       Hardware Interrupts       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      |                                          |    |

| 4.6.4Power Down Control Register (0xC00A: R/W)224.6.5Breakpoint Register (0xC014: R/W)224.7INTERRUPTS234.7.1Hardware Interrupts23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |      |                                          |    |

| 4.6.5       Breakpoint Register (0xC014: R/W)       22         4.7       INTERRUPTS       23         4.7.1       Hardware Interrupts       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      |                                          |    |

| 4.7       INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |      |                                          |    |

| 4.7.1 Hardware Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |                                          |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |      |                                          |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ര  |      | A                                        |    |

ScanLogic Corporation. All rights reserved. SL16 is a trademark of ScanLogic Corporation. The information and specifications contained in this document are subject to change without notice.

**Revision: 1.20 Page:** 2

|     | 4.7.2          | Interrupt Enable Register (0xC00E: R/W)                    | 21 |

|-----|----------------|------------------------------------------------------------|----|

|     | 4.7.2          | GPIO Interrupt Control Register (0xC00E. R/W)              |    |

|     | 4.7.4          | Software Interrupts                                        |    |

|     |                | RT INTERFACE.                                              |    |

|     | 4.8.1          | UART Control Register (0xC0E0: R/W)                        |    |

|     | 4.8.2          | UART Status Register (0xC0E2: Read Only)                   |    |

|     | 4.8.2<br>4.8.3 | UART Transmit Data Register (0xC0E4: Write Only)           |    |

|     | 4.8.3<br>4.8.4 | UART Receive Data Register (0xC0E4: Write Only)            |    |

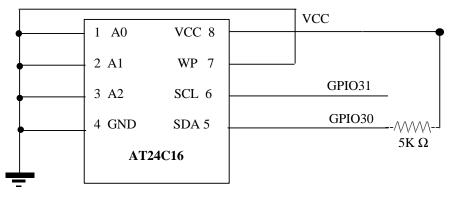

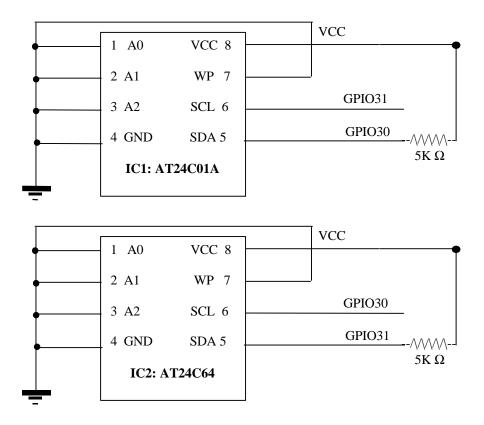

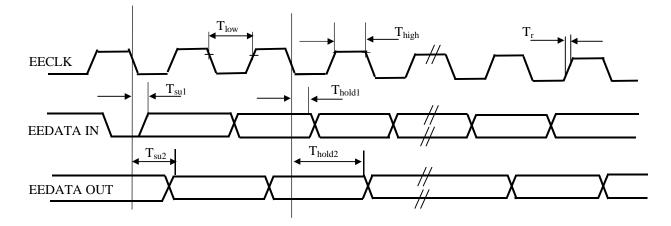

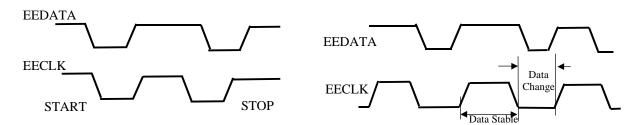

| 4.9 |                | IAL FLASH EEPROM INTERFACE (I2C)                           |    |

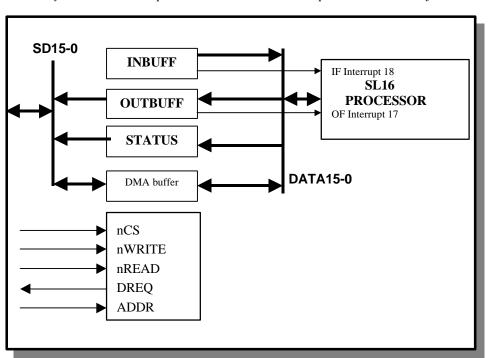

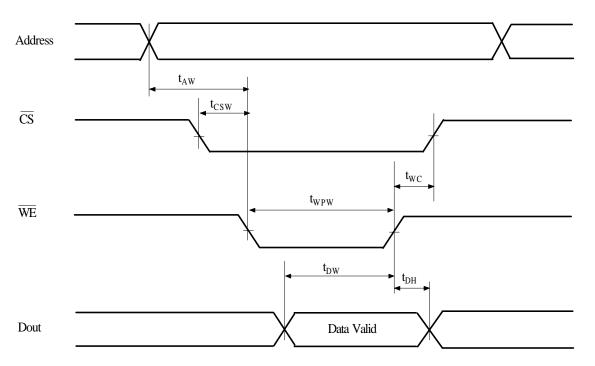

|     |                | ERNAL SRAM, EPROM, DRAM                                    |    |

|     | 4.10.1         | Memory Control Register (0xC03E: R/W)                      |    |

|     | 4.10.1         | Extended Memory Control Register (0xC03E: R/W)             |    |

|     |                |                                                            |    |

|     | 4.10.3         | Extended Page 1 Map Register (0xC018: R/W)                 |    |

|     | 4.10.4         | Extended Page 2 Map Register (0xC01A: R/W)                 |    |

|     | 4.10.5         | DRAM Control Register (0xC038: R/W)                        |    |

|     | 4.10.6         | Memory Map                                                 |    |

| 4.  |                | IERAL TIMERS AND WATCH DOG TIMER.                          |    |

|     | 4.11.1         | Timer 0 Count Register (0xC010: R/W)                       |    |

|     | 4.11.2         | Timer 1 Count Register (0xC012: R/W)                       |    |

|     | 4.11.3         | Watchdog Timer Count & Control Register (0xC00C: R/W)      |    |

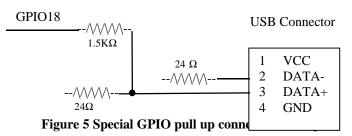

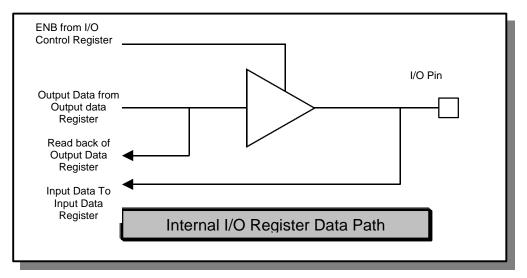

| 4.  |                | CIAL GPIO FUNCTION FOR SUSPEND, RESUME AND LOW POWER MODES |    |

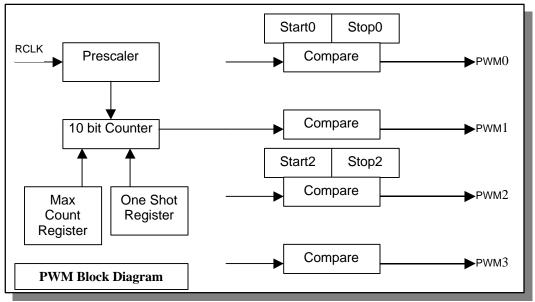

| 4.  |                | GRAMMABLE PULSE/PWM INTERFACE                              |    |

|     | 4.13.1         | PWM Control Register (0xC0E6: R/W)                         |    |

|     | 4.13.2         | PWM Maximum Count Register (0xC0E8: R/W)                   |    |

|     | 4.13.3         | PWM Channel 0 Start Register (0xC0EA: R/W)                 |    |

|     | 4.13.4         | PWM Channel 0 Stop Register (0xC0EC: R/W)                  |    |

|     | 4.13.5         | PWM Channel 1 Start Register (0xC0EE: R/W)                 |    |

|     | 4.13.6         | PWM Channel 1 Stop Register (0xC0F0: R/W)                  |    |

|     | 4.13.7         | PWM Channel 2 Start Register (0xC0F2: R/W)                 |    |

|     | 4.13.8         | PWM Channel 2 Stop Register (0xC0F4: R/W)                  |    |

|     | 4.13.9         | PWM Channel 3 Start Register (0xC0F6: R/W)                 |    |

|     | 4.13.10        | PWM Channel 3 Stop Register (0xC0F8: R/W)                  |    |