Technology, Inc. 335 Pioneer Way Mt View, California 94041 (650) 526-1490 Fax (650) 526-1494 e-mail: sales@netchip.com Internet: www.netchip.com

# NET1031 USB Scanner Controller PRELIMINARY SPECIFICATION

# **ADVANCE INFORMATION**

Doc #: 605-0073-0011 Revision: 1.0 Date: 3 / 19 / 99 This document contains material that is confidential to NetChip. Reproduction without the express written consent of NetChip is prohibited. All reasonable attempts were made to ensure the contents of this document are accurate; however no liability, expressed or implied is guaranteed. NetChip reserves the right to modify this document, without notification, at any time.

# **Revision History**

| Revision | Issue Date       | Comments                                                        |  |

|----------|------------------|-----------------------------------------------------------------|--|

| 0.1      | October 17, 1997 | NET1031 Initial Draft Specification Proposal                    |  |

| 0.2      | March 30, 1998   | 16-Bit Register initial draft                                   |  |

| 0.3      | July 22, 1998    | Move Applications information to AppNote.                       |  |

|          |                  | Update Register layout                                          |  |

| 0.4      | July 23, 1998    | Re-organize the endpoint structure                              |  |

| 0.5      | Aug 27, 1998     | Re-organize registers; add new SRAM and initialization features |  |

| 0.6      | Sept 11, 1998    | Add some new registers                                          |  |

| 0.7      | Oct 7, 1998      | Add some more new registers                                     |  |

| 0.8      | Nov 9, 1998      | Clarify some text. Modify some registers                        |  |

| 0.9      | Jan 4, 1999      | Modify some registers                                           |  |

| 0.10     | Jan 8, 1999      | Change pinouts, modify some defaults                            |  |

| 0.11     | Jan 17, 1999     | Modify some defaults                                            |  |

| 1.0      | Mar 19, 1999     | Modify some defaults, remove references to PRNU and B/W         |  |

|          |                  | threshold                                                       |  |

# NET1031 USB Scanner Controller

| 1 | Highlig   | hts                                                   | 7    |

|---|-----------|-------------------------------------------------------|------|

|   | 1.1 Intro | duction                                               | 7    |

|   | 1.2 Feat  | ures                                                  | 7    |

|   | 1.2.1     | General Features                                      | 7    |

|   | 1.2.2     | Scanner Features                                      | 7    |

|   | 1.2.3     | USB Features                                          | 7    |

|   | 1.3 Over  | view                                                  | 7    |

|   | 1.4 NET   | 1031 Block Diagram                                    | 9    |

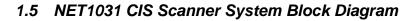

|   | NET1031   | CIS Scanner System Block Diagram                      | . 10 |

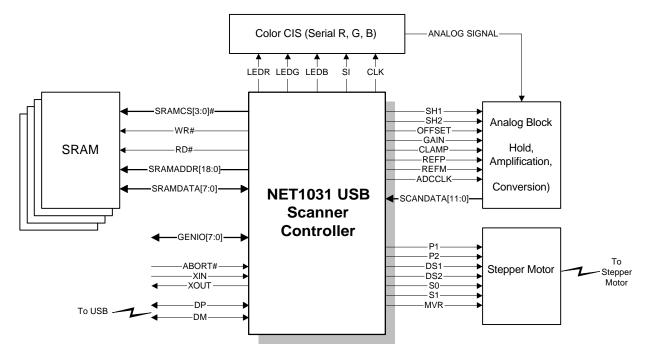

|   | NET1031   | CCD Scanner System Block Diagram                      | . 10 |

| 2 |           | nnection Diagram                                      |      |

| 3 |           | scription                                             |      |

| 4 |           | onal Description                                      |      |

|   | 4.1 Start | -Up                                                   |      |

|   | 4.1.1     | Reading from Initialization Device                    |      |

|   | 4.1.2     | Enumeration by the Host PC                            |      |

|   | 4.1.3     | Configuration by the Scanner Driver                   |      |

|   | 4.1.4     | Global Calibration                                    |      |

|   |           | alization Interface                                   |      |

|   | 4.2.1     | E <sup>2</sup> PROMs (93CS06, 93CS46, 93CS56, 93CS66) |      |

|   | 4.2.2     | IDSEL Pin Initialization                              |      |

|   |           | ner Functions                                         |      |

|   | 4.3.1     | CCD/CIS Control                                       |      |

|   | 4.3.2     | General Data Flow                                     |      |

|   | 4.3.3     | Analog Block Interface                                |      |

|   | 4.3.4     | Stepper Motor Control                                 |      |

|   | 4.3.5     | Image Buffering in SRAM                               |      |

|   | 4.3.6     | General I/O Pins                                      |      |

|   | 4.3.7     | Abort# Pin                                            |      |

|   |           | Interface                                             |      |

|   | 4.4.1     | Default Control Pipe (Endpoint 0x00)                  |      |

|   | 4.4.2     | SRAM Write Pipe (Endpoint 0x01)                       |      |

|   | 4.4.3     | SRAM/Image Data Read Pipe (Endpoint 0x81)             |      |

|   | 4.4.4     | Status Input Pipe (Endpoint 0x82)                     |      |

|   |           | Space Access                                          |      |

|   | -         | end Mode                                              |      |

|   | 4.6.1     | The Suspend Sequence                                  |      |

|   | 4.6.2     | Host-Initiated Wake-Up.                               |      |

|   | 4.6.3     | Device-Remote Wake-Up                                 |      |

|   |           | Port Reset.                                           |      |

|   |           | 1031 Power Configuration                              |      |

|   | 4.8.1     | Bus-Powered Device                                    |      |

| = | 4.8.2     | Self-Powered Device                                   |      |

| 5 | -         | r Descriptions                                        |      |

|   | 5.1 Com   | Control Registers Summary                             |      |

|   | 5.1.1     | (Address 00h; MASTERCTL) Master Control               |      |

|   | 5.1.2     | (Address 00h, MASTERCTE) Master Control               |      |

|   | 5.1.5     | (Address 02h; PIXCTL) Pixel Control                   |      |

|   | 5.1.5     | (Address 03h; IOCFG) I/O Pin Configuration            |      |

|   |           |                                                       |      |

| 5.1.6            | (Address 04h; SCANSTAT) Scanner Status                                      |      |

|------------------|-----------------------------------------------------------------------------|------|

| 5.1.7            | (Address 05h; IOSTAT) I/O Pin Status                                        |      |

| 5.1.8            | (Address 06h; SCANCHG) Scanner Status Change Register                       |      |

| 5.1.9            | (Address 07h; IOCHG) I/O Pin Status Change Register                         |      |

| 5.1.10           | (Address 08h; SRAMADDR1) SRAM Address, Most-Significant Word                |      |

| 5.1.11           | (Address 09h; SRAMADDR0) SRAM Address, Least-Significant Word               |      |

| 5.1.12           | (Address 0Ah - 0Fh; RESERVED) Reserved for future use                       |      |

| 5.1.13           | (Address 10h; SRAMBASE1) SRAM FIFO Address Base, Most-Significant Word      |      |

| 5.1.14           | (Address 11h; SRAMBASE0) SRAM FIFO Address Base, Least-Significant Word     |      |

| 5.1.15           | (Address 12h; SRAMTOP1) SRAM FIFO Address Top, Most-Significant Word        |      |

| 5.1.16           | (Address 13h; SRAMTOP0) SRAM FIFO Address Top, Least-Significant Word       |      |

| 5.1.17           | (Address 14h; FIFOFSTHR1) FIFO Full-Speed Threshold, Most-Significant Word  | . 32 |

| 5.1.18           | (Address 15h; FIFOFSTHR0) FIFO Full-Speed Threshold, Least-Significant Word | . 32 |

| 5.1.19           | (Address 16h; FIFOHSTHR1) FIFO Half-Speed Threshold, Most-Significant Word  | . 32 |

| 5.1.20           | (Address 17h; FIFOHSTHR0) FIFO Half-Speed Threshold, Least-Significant Word | . 33 |

| 5.1.21           | (Address 18h; FIFOSTOPTHR1) FIFO Stop Threshold, Most-Significant Word      | . 33 |

| 5.1.22           | (Address 19h; FIFOSTOPTHR0) FIFO Stop Threshold, Least-Significant Word     | . 33 |

| 5.1.23           | (Address 1Ah; FIFOCOUNT1) FIFO Byte Count, Most-Significant Word            | . 33 |

| 5.1.24           | (Address 1Bh; FIFOCOUNT0) FIFO Byte Count, Least-Significant Word           | . 33 |

| 5.1.25           | (Address 1Ch; FIFOSTAT) FIFO Status.                                        |      |

| 5.1.26           | (Address 1Dh - 1Fh; RESERVED) Reserved for future use                       | . 34 |

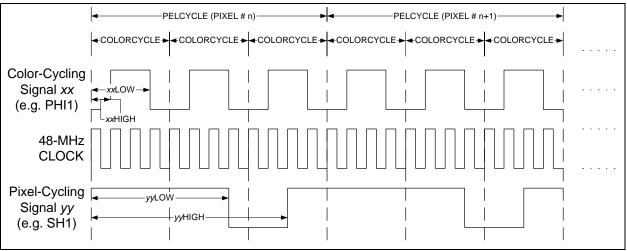

| 5.1.27           | (Address 20h; COLORCYCLE) Color Cycle Time Period                           |      |

| 5.1.28           | (Address 21h; PELCYCLE) Pixel Cycle Time Period                             |      |

| 5.1.29           | (Address 22h; LINECYCLE) Line Cycle Time Period                             |      |

| 5.1.30           | (Address 23h; STEPCYCLE) Stepper Cycle Time Period                          |      |

| 5.1.31           | (Address 25h; PELSTROBE) Pixel Strobe                                       |      |

| 5.1.32           | (Address 26h; COLORSTART) Color Cycle Start Offset                          |      |

| 5.1.33           | (Address 27h; PELSTART) Pixel Cycle Start Offset                            |      |

| 5.1.34           | (Address 28h; FIRSTPEL) First Active Pixel.                                 |      |

| 5.1.35           | (Address 29h; LASTPEL) Last Active Pixel                                    |      |

| 5.1.36           | (Address 2Ah; FIRSTLINE) First Scan Line                                    |      |

| 5.1.37           | (Address 2Bh; LASTLINE) Last Scan Line                                      |      |

|                  | -based Waveform Register Description                                        |      |

| 5.2.1            | Pixel-based Waveform Register Summary                                       |      |

| 5.2.2            | (xxxxHIGH) Pixel-based Waveform High Offset                                 |      |

| 5.2.3            | (xxxxLOW) Pixel-based Waveform Low Offset                                   |      |

| 5.2.4            | (xxxxCTL) Pixel-based Waveform Control                                      |      |

|                  | -based Waveform Register Description                                        |      |

| 5.3.1            | Line-based Waveform Register Summary                                        |      |

| 5.3.2            | (xxxxHIGH) Line-based Waveform High Offset                                  |      |

| 5.3.3            | (xxxxLOW) Line-based Waveform Low Offset                                    |      |

| 5.3.4            | (xxxxCTL) Line-based Waveform Control                                       |      |

|                  | per-based Waveform Register Description                                     |      |

| 5.4.1            | Stepper-based Waveform Register Summary                                     |      |

| 5.4.2            | (xxxxHIGH) Stepper-based Waveform High Offset                               |      |

| 5.4.3            | (xxxxLOW) Stepper-based Waveform Low Offset                                 |      |

| 5.4.4            | (xxxxCTL) Stepper-based Waveform Control                                    |      |

|                  | Register Description                                                        |      |

| 5.5 USB<br>5.5.1 | USB Register Summary                                                        |      |

| 5.5.2            | (Address F0h; VID) Vendor ID                                                |      |

| 5.5.2            | (Address F0h, VID) Vendor ID                                                |      |

| 5.5.5<br>5.5.4   | (Address F2h; REL) Release Number                                           |      |

| 5.5.4            | (Auuros 1211, NEL) Release Inullioel                                        | . 43 |

|   | 5.5.5     | (Address F3h; MAXPWR) Maximum Power                      |      |

|---|-----------|----------------------------------------------------------|------|

|   | 5.5.6     | (Address F4h; USBCTL1) USB Control Register 1            |      |

|   | 5.5.7     | (Address F5h; USBCTL2) USB Control Register 2            |      |

|   | 5.5.8     | (Address F6h; STRINDEX1) String Index 1                  |      |

|   | 5.5.9     | (Address F7h; STRINDEX2) String Index 2                  |      |

|   | 5.5.10    | (Address F8h - FBh; RESERVED) Reserved for future use    |      |

|   | 5.5.11    | (Address FCh; EECTL) EEPROM Control                      |      |

|   | 5.5.12    | (Address FDh; EEADDR) EEPROM Address                     |      |

|   | 5.5.13    | (Address FEh; EEDATA) EEPROM Data                        |      |

|   | 5.5.14    | (Address FFh; REVISION) NET1031 Silicon Revision         |      |

| 6 |           | endor-Specific Device Requests (Endpoint 0)              |      |

|   | U         | ster Write                                               |      |

|   | U         | ster Read                                                |      |

|   |           | Write                                                    |      |

|   |           | Read                                                     |      |

|   |           | ufacturer Test Mode                                      |      |

|   | 6.5.1     | 6.5.1 Device Clear Feature (Timing Test Mode)            |      |

| _ | 6.5.2     | 6.5.2 Device Set Feature (Timing Test Mode)              |      |

| 7 | USB St    | andard Device Requests (Endpoint 0)                      | . 51 |

|   |           | rol 'IN' Transactions                                    |      |

|   | 7.1.1     | Get Device Status                                        |      |

|   | 7.1.2     | Get Interface Status                                     |      |

|   | 7.1.3     | Get Endpoint 0x00, 0x01, 0x81, 0x82 Status               |      |

|   | 7.1.4     | Get Device Descriptor (18 Bytes)                         |      |

|   | 7.1.5     | Get Configuration Descriptor (39 bytes)                  |      |

|   | 7.1.6     | Get String Descriptor 0                                  |      |

|   | 7.1.7     | Get String Descriptor 1                                  |      |

|   | 7.1.8     | Get String Descriptor 2                                  |      |

|   | 7.1.9     | Get String Descriptor 3                                  |      |

|   | 7.1.10    | Get Configuration                                        |      |

|   | 7.1.11    | Get Interface                                            |      |

|   |           | rol 'OUT' Transactions                                   |      |

|   | 7.2.1     | Set Address                                              |      |

|   | 7.2.2     | Set Configuration                                        |      |

|   | 7.2.3     | Set Interface                                            |      |

|   | 7.2.4     | Device Clear Feature                                     |      |

|   | 7.2.5     | Device Set Feature                                       |      |

|   | 7.2.6     | Endpoint Clear Feature                                   |      |

| ~ | 7.2.7     | Endpoint Set Feature                                     |      |

| 8 |           | id Interrupt Endpoints                                   |      |

|   |           | boint 0x01 'OUT' Transactions (SRAM Write Pipe)          |      |

|   |           | boint 0x81 'IN' Transactions (SRAM/Image Data Read Pipe) |      |

| • | -         | point 0x82 'IN' Transactions (Status Input Pipe)         |      |

| 9 | 0         | Fiming                                                   |      |

|   | U         | al Timing                                                |      |

|   | 9.1.1     | Color- and Pixel-Based Signal Timing                     |      |

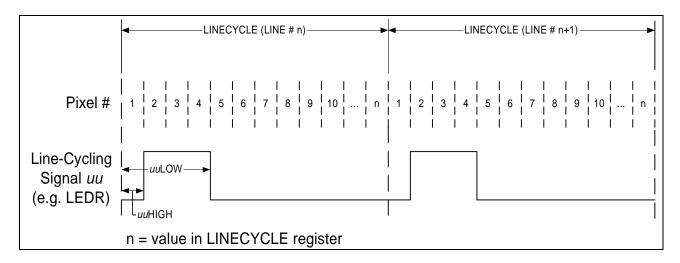

|   | 9.1.2     | Line-Based Signal Timing.                                |      |

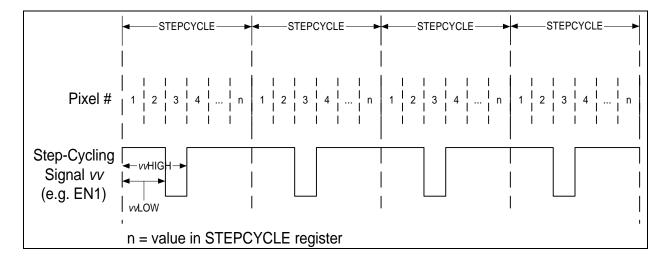

|   | 9.1.3     | Stepper-Based Signal Timing                              |      |

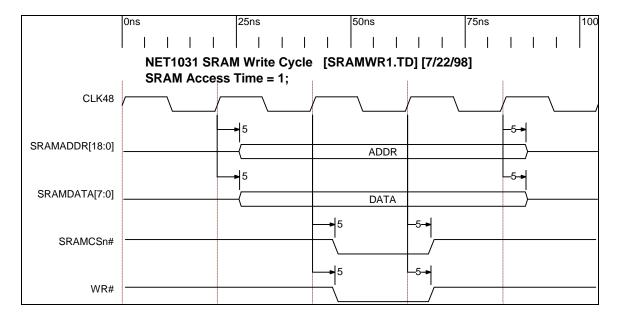

|   |           | M Write Timing                                           |      |

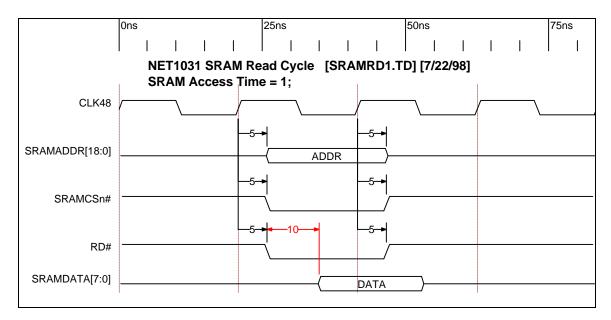

|   |           | M Read Timing                                            |      |

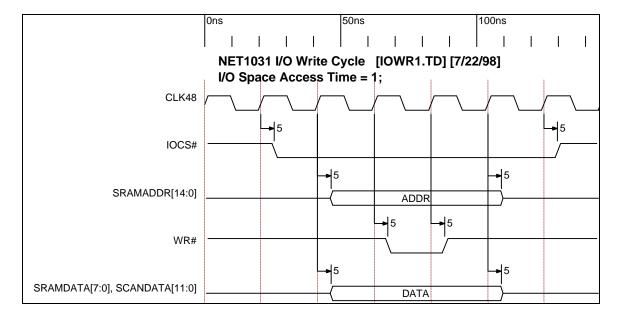

|   |           | Write Timing                                             |      |

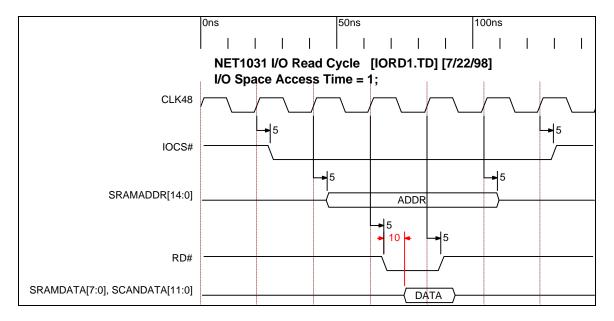

|   | 9.5 I/O I | Read Timing                                              | . 60 |

| Elect  | rical Specifications                                                                 | 61                                   |

|--------|--------------------------------------------------------------------------------------|--------------------------------------|

|        |                                                                                      |                                      |

| 0.2    | Recommended Operating Conditions                                                     | 61                                   |

|        |                                                                                      |                                      |

|        |                                                                                      |                                      |

| 10.3.2 | 2 USB Port DC Specifications                                                         | 62                                   |

| 10.3.3 | 3 Local Bus (+3.3V) DC Specifications                                                | 62                                   |

| 10.3.4 | 4 Local Bus (+5.0V) DC Specifications                                                | 63                                   |

|        |                                                                                      |                                      |

|        |                                                                                      |                                      |

|        |                                                                                      |                                      |

|        |                                                                                      |                                      |

|        |                                                                                      |                                      |

|        | 0.1<br>0.2<br>0.3<br>10.3.1<br>10.3.2<br>10.3.2<br>10.3.4<br>0.4<br>10.4.2<br>10.4.2 | 0.2 Recommended Operating Conditions |

# 1 Highlights

# 1.1 Introduction

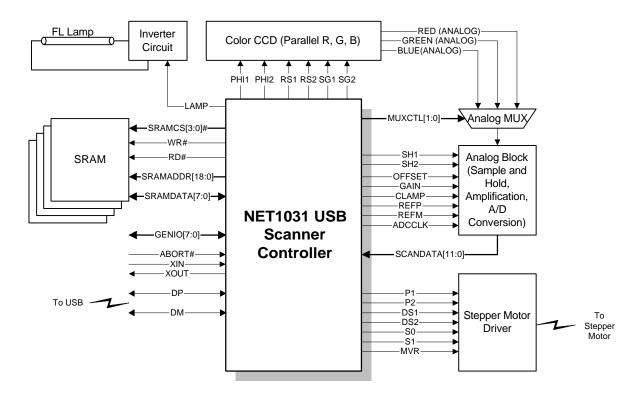

The NetChip USB scanner engine provides a single chip solution providing a USB core and scanner imaging control in a single chip. No external microprocessor is needed in the scanner. The NET1031 replaces multiple ICs in a typical scanner design, and is fully programmable to ensure support with a wide range of scanning hardware. The NET1031 provides the necessary signaling for both color and gray scale charge-coupled devices (CCD) or contact image sensors (CIS), and contains a fully-functional USB core to control the scanner and perform image transfers across USB.

# 1.2 Features

#### 1.2.1 General Features

- Single-Chip USB Scanner Controller Solution

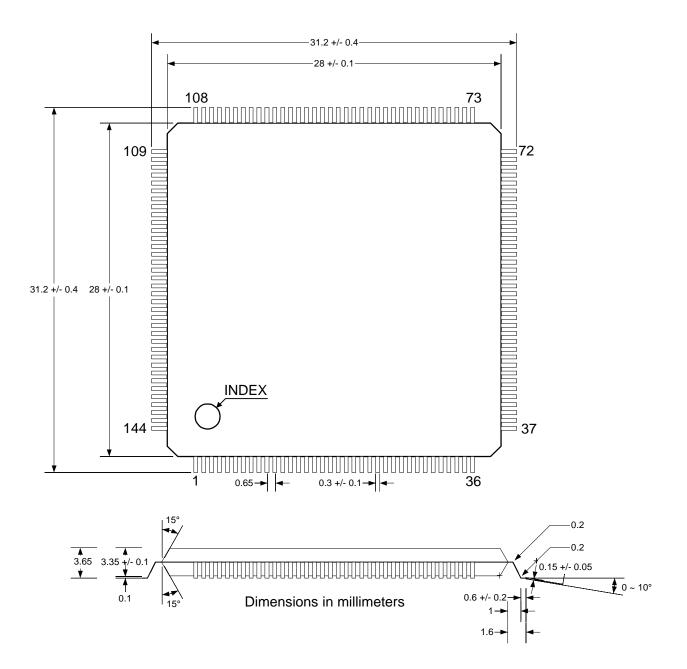

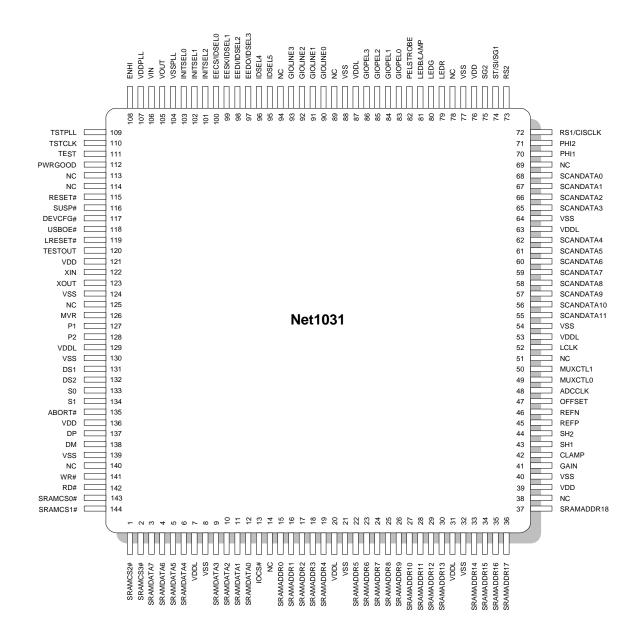

- Low Power CMOS in 144-pin PQFP Package

- Core operates at 3.3V, dual-voltage (3.3V/5.0V) Scanner-Side Interface

- Supports 500 µA suspend current requirement of USB

- 6 MHz crystal oscillator with internal PLL.

- Generic I/O-Space Read and Write Access for programmable external components

# 1.2.2 Scanner Features

- Supports CIS and CCD Sensors in Hardware

- Stepper Motor Controller Interface

- Up to 2 MB SRAM Interface for Image Data Buffer

- Up to 36-bit Color, 12-bit Grayscale

# 1.2.3 USB Features

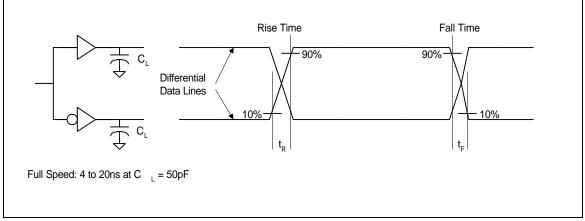

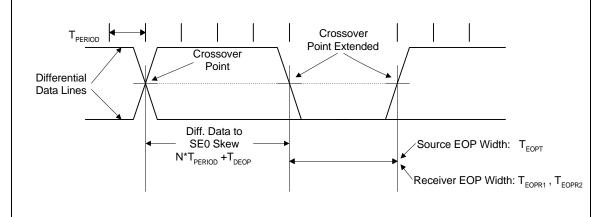

- USB Specification Version 1.1 Compliant

- Supports Full-Speed USB Bandwidth of 12 Mbps

- Status Reporting through USB Interrupt Endpoint

# 1.3 Overview

The NetChip NET1031 USB scanner engine is designed to work with most CCDs and CISs. Sensor, analog acquisition subsystem, and stepper motor control signals are provided directly from the NET1031. The NET1031 is designed to work both in a pull model (such as TWAIN) and a push model. It can signal to a host driver to initiate a scan when a target has been loaded and is ready to be scanned in. The NET1031 will enter a low-power suspend mode when required by the USB, and can wake up in response to activity on either the host or the scanner. The NET1031 can also perform a "device remote wake-up" (as defined by the USB specification) to wake a host that has suspended its USB.

The NET1031 can address up to 2 Mbytes of external SRAM. This memory is used as a FIFO for a partially scanned image prior to sending it to the host. The NET1031 can be programmed to slow the scan rate to one-half speed, and stop if the FIFO becomes nearly full. This may occur when the data rate from the scanner to the host slows due to other devices on the USB or other limitations of the host.

#### **Preliminary Specification**

The NET1031 interfaces directly to a stepper motor driver. Once programmed it will send the appropriate signals to energize the various coils and step the motor forward or backward.

An interface to an optional external serial memory device is provided to initialize the NET1031 with parameters necessary for enumeration of the device. Parameters loaded from the serial device include the Vendor ID, Product ID, Revision Number, Maximum Power fields, and USB control bits, as well as optional string descriptors.

The NET1031 has 8 programmable general input/output pins. These signals may be configured as digital inputs, Pulse-Width Modulation (PWM) outputs, or digital outputs. The outputs themselves may be configured totem-pole or open-drain. The chip can be driven with a 6 MHz crystal or clock oscillator.

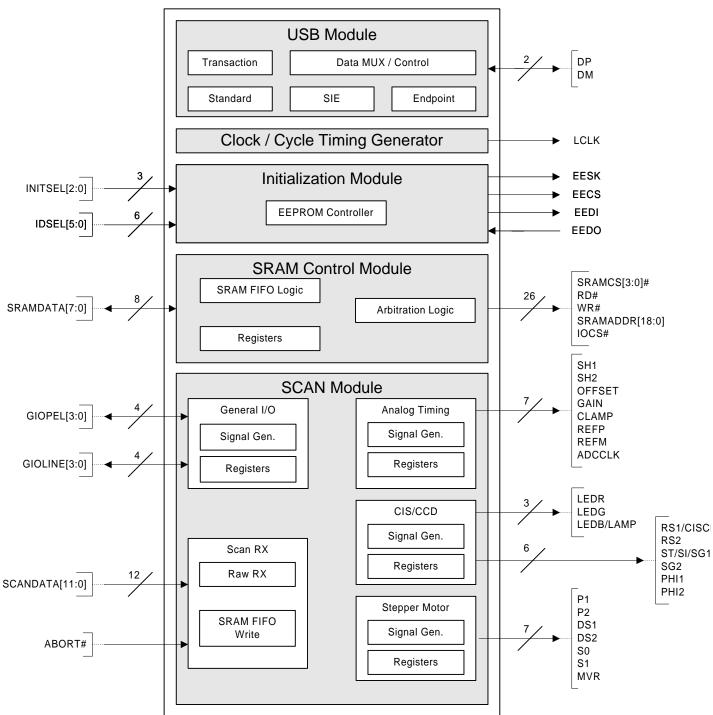

# 1.4 NET1031 Block Diagram

Figure 1-1: NET1031 Block Diagram

# 1.6 NET1031 CCD Scanner System Block Diagram

©NetChip Technology, Inc., 1999 335 Pioneer Way, Mountain View, California 94041 TEL (650) 526-1490 FAX (650) 526-1494 http://www.netchip.com Revision 1.0, Mar 19, 1999

# 2 Pin Connection Diagram

# 3 Pin Description

**NOTE:** "Pin Numbers" are just being assigned sequentially to get a pin count for now.

Table 3-1: Pin Types

| Pin Type | Description                            |

|----------|----------------------------------------|

| Ι        | Input                                  |

| 0        | Output                                 |

| I/O      | Bi-Directional (with Tri-State)        |

| S        | Schmitt Trigger                        |

| TS       | Tri-State                              |

| TP       | Totem Pole                             |

| OD       | Open Drain                             |

| PD       | 50KΩ Internal Pull-Down Resistor       |

| PU       | 50K $\Omega$ Internal Pull-Up Resistor |

| #        | Active Low                             |

**NOTE:** When the NET1031 is in the suspended state, input pins that do not have an internal pull-up or pull-down resistor (designated by PU or PD in the "Type" column) must be driven externally.

| Signal Name | Pin | Туре           | Description                                                  |

|-------------|-----|----------------|--------------------------------------------------------------|

| 5           |     |                |                                                              |

| SCANDATA0   | 68  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     |                | writes                                                       |

| SCANDATA1   | 67  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     |                | writes                                                       |

| SCANDATA2   | 66  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     |                | writes                                                       |

| SCANDATA3   | 65  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     |                | writes                                                       |

| SCANDATA4   | 62  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     | , ,            | writes                                                       |

| SCANDATA5   | 61  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     |                | writes                                                       |

| SCANDATA6   | 60  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     |                | writes                                                       |

| SCANDATA7   | 59  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     | , ,            | writes                                                       |

| SCANDATA8   | 58  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     |                | writes                                                       |

| SCANDATA9   | 57  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     | , ,            | writes                                                       |

| SCANDATA10  | 56  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     | , ,            | writes                                                       |

| SCANDATA11  | 55  | I/O, 6mA, PU   | Scan Data Bit. Scan Data Input from A/D; Data Output for I/O |

|             |     | , ,            | writes                                                       |

| MUXCTL0     | 49  | O, 6mA, TS, PD | MUX Control Bit. Analog scan data input MUX selector         |

| MUXCTL1     | 50  | O, 6mA, TS, PD | MUX Control Bit. Analog scan data input MUX selector         |

#### **Table 3-2: Pin Descriptions**

| ADCCLK               | 48  | O, 6mA, TS, PD     | A/D Clock. Provides the analog-to-digital converter clock              |

|----------------------|-----|--------------------|------------------------------------------------------------------------|

| CLAMP                | 42  | O, 6mA, TS, PD     | <b>Programmable Clamp.</b> Provides a Programmable Clamping Signal     |

| SH1                  | 43  | O, 6mA, TS, PD     | Sample/Hold 1. Programmable Sample and Hold Signal                     |

| SH2                  | 44  | O, 6mA, TS, PD     | Sample/Hold 2. Programmable Sample and Hold Signal                     |

| REFP                 | 45  | O, 6mA, TS, PD     | A/D Positive Ref. Adjustable PWM Ref + for the A/D                     |

| REFN                 | 46  | O, 6mA, TS, PD     | A/D Negative Ref. Adjustable PWM Ref – for the A/D                     |

| OFFSET               | 47  | O, 6mA, TS, PD     | A/D Offset. Adjustable PWM offset control                              |

| GAIN                 | 41  | O, 6mA, TS, PD     | A/D Gain. Adjustable PWM gain control                                  |

| PHI1                 | 70  | O, 6mA, TS, PD     | <b>CCD Clock Phase 1.</b> Output Phase 1 Clock for CCD usage           |

| PHI2                 | 71  | 0, 6mA, TS, PD     | <b>CCD Clock Phase 2.</b> Output Phase 2 Clock for CCD usage           |

| RS1 / CISCLK         | 72  | 0, 6mA, TS, PD     | <b>Reset 1 Clock.</b> Output Reset 1 Clock for CCD or Clk for CIS      |

| RS2                  | 73  | 0, 6mA, TS, PD     | Reset 2 Clock. Output Reset 2 Clock for CCD                            |

| ST/SI/SG1            | 74  | O, 6mA, TS, PD     | Shift Gate 1. Output Shift Gate Signal or end of line Clk              |

| SG2                  | 75  | O, 6mA, TS, PD     | Shift Gate 2. Output Shift Gate 2 Signal                               |

| LEDR                 | 79  | O, 6mA, TS, PD     | <b>Red LED Control.</b> Output Signal to control the Red Led           |

| LEDG                 | 80  | O, 6mA, TS, PD     | Green LED Control. Output Signal to control the Green Led              |

| LEDB / LAMP          | 81  | O, 6mA, TS, PD     | Blue LED Control. Output Signal to control the Blue Led or             |

| LEDD / LAMI          | 01  | 0, 011A, 15, 1D    | Lamp                                                                   |

| PELSTROBE            | 82  | O, 6mA, TS, PD     | <b>Pixel Strobe.</b> This output pulses after each pixel cycle. Rising |

| TELSTRODE            | 02  | 0, 011A, 15, 1D    | edge captures pixel data for NET1031.                                  |

| GIOPEL0              | 83  | I/O, 12mA, PU      | General Pixel-based I/O bit. Programmable I/O, PWM or                  |

| OIOI ELO             | 85  | 1/0, 1207, 10      | Digital.                                                               |

| GIOPEL1              | 84  | I/O, 12mA, PU      | General Pixel-based I/O bit. Programmable I/O, PWM or                  |

| OIOI LEI             | 04  | 1/0, 12/11/1, 10   | Digital                                                                |

| GIOPEL2              | 85  | I/O, 12mA, PU      | <b>General Pixel-based I/O bit.</b> Programmable I/O, PWM or           |

| GIGI EE2             | 00  | 1,0,121111,10      | Digital                                                                |

| GIOPEL3              | 86  | I/O, 12mA, PU      | General Pixel-based I/O bit. Programmable I/O, PWM or                  |

|                      |     | ,                  | Digital                                                                |

| GIOLINE0             | 90  | I/O, 12mA, PU      | General Line-based I/O bit. Programmable I/O, PWM or                   |

|                      |     | ,                  | Digital                                                                |

| GIOLINE1             | 91  | I/O, 12mA, PU      | General Line-based I/O bit. Programmable I/O, PWM or                   |

|                      |     | , ,                | Digital                                                                |

| GIOLINE2             | 92  | I/O, 12mA, PU      | General Line-based I/O bit. Programmable I/O, PWM or                   |

|                      |     | · · ·              | Digital                                                                |

| GIOLINE3             | 93  | I/O, 12mA, PU      | General Line-based I/O bit. Programmable I/O, PWM or                   |

|                      |     |                    | Digital                                                                |

| ABORT#               | 135 | I, PU              | Abort Scan. Abort Scan control                                         |

| WR#                  | 141 | O, 12mA, TS,       | Write Strobe. Write strobe for external SRAM and I/O writes            |

|                      |     | PU                 |                                                                        |

| RD#                  | 142 | O, 12mA, TS,<br>PU | Read Strobe. Read strobe for external SRAM and I/O reads               |

| SRAMCS0#             | 143 | O, 6mA, TS, PU     | SRAM Chip Select. Chip Select 0 for the external SRAM                  |

| SRAMCS1#             | 144 | O, 6mA, TS, PU     | SRAM Chip Select. Chip Select 0 for the external SRAM                  |

| SRAMCS1#<br>SRAMCS2# | 1   | O, 6mA, TS, PU     | SRAM Chip Select. Chip Select 1 for the external SRAM                  |

| SIGNIC S2T           |     | 0, 0117, 15, 10    |                                                                        |

| SRAMCS3#             | 2   | O, 6mA, TS, PU     | <b>SRAM Chip Select.</b> Chip Select 3 for the external SRAM           |

| rieminary spe |    | 1                  | 1                                                                             |

|---------------|----|--------------------|-------------------------------------------------------------------------------|

| SRAMADDR0     | 15 | O, 12mA, TS,<br>PU | <b>SRAM Address Bus Bit.</b> Address Bus to external image SRAM or I/O device |

| SRAMADDR1     | 16 | O, 12mA, TS,<br>PU | <b>SRAM Address Bus Bit.</b> Address Bus to external image SRAM or I/O device |

| SRAMADDR2     | 17 | O, 12mA, TS,<br>PU | <b>SRAM Address Bus Bit.</b> Address Bus to external image SRAM or I/O device |

| SRAMADDR3     | 18 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM or I/O device        |

| SRAMADDR4     | 19 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR5     | 22 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR6     | 23 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR7     | 24 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR8     | 25 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR9     | 26 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR10    | 27 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR11    | 28 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR12    | 29 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR13    | 30 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR14    | 33 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM<br>or I/O device     |

| SRAMADDR15    | 34 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM                      |

| SRAMADDR16    | 35 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM                      |

| SRAMADDR17    | 36 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM                      |

| SRAMADDR18    | 37 | O, 12mA, TS,<br>PU | SRAM Address Bus Bit. Address Bus to external image SRAM                      |

| SRAMDATA0     | 12 | I/O, 12mA, PU      | SRAM Data Bus Bit. Data Bus to / from external SRAM or I/O device             |

| SRAMDATA1     | 11 | I/O, 12mA, PU      | SRAM Data Bus Bit. Data Bus to / from external SRAM or I/O device             |

| SRAMDATA2     | 10 | I/O, 12mA, PU      | SRAM Data Bus Bit. Data Bus to / from external SRAM or I/O device             |

| SRAMDATA3     | 9  | I/O, 12mA, PU      | SRAM Data Bus Bit. Data Bus to / from external SRAM or I/O device             |

| SRAMDATA4     | 6  | I/O, 12mA, PU      | SRAM Data Bus Bit. Data Bus to / from external SRAM or I/O device             |

| SRAMDATA5   | 5   | I/O, 12mA, PU  | <b>SRAM Data Bus Bit.</b> Data Bus to / from external SRAM or I/O device                                                                                                                                                                                                                                                                       |

|-------------|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRAMDATA6   | 4   | I/O, 12mA, PU  | SRAM Data Bus Bit. Data Bus to / from external SRAM or I/O device                                                                                                                                                                                                                                                                              |

| SRAMDATA7   | 3   | I/O, 12mA, PU  | SRAM Data Bus Bit. Data Bus to / from external SRAM or I/O device                                                                                                                                                                                                                                                                              |

| MVR         | 126 | O, 6mA, TS, PD | Throttle. Stepper motor throttle control                                                                                                                                                                                                                                                                                                       |

| P1          | 127 | O, 6mA, TS, PD | Energize Phase 1. Energize Phase 1 of Stepper Motor                                                                                                                                                                                                                                                                                            |

| P2          | 128 | O, 6mA, TS, PD | Energize Phase 2. Energize Phase 2 of Stepper Motor                                                                                                                                                                                                                                                                                            |

| DS1         | 131 | O, 6mA, TS, PU | <b>Disable Phase 1.</b> Disable Phase 1 of Stepper Motor                                                                                                                                                                                                                                                                                       |

| DS2         | 132 | O, 6mA, TS, PU | <b>Disable Phase 2.</b> Disable Phase 2 of Stepper Motor                                                                                                                                                                                                                                                                                       |

| S0          | 133 | O, 6mA, TS, PD | Voltage Reference Selector. Select one of four voltage references for Stepper Motor.                                                                                                                                                                                                                                                           |

| S1          | 134 | O, 6mA, TS, PD | Voltage Reference Selector. Select one of four voltage references for Stepper Motor.                                                                                                                                                                                                                                                           |

| INITSEL0    | 103 | I, PU          | <b>Initialization Select Bit 0.</b> Select source of register initialization data.                                                                                                                                                                                                                                                             |

| INITSEL1    | 102 | I, PU          | <b>Initialization Select Bit 1.</b> Select source of register initialization data.                                                                                                                                                                                                                                                             |

| INITSEL2    | 101 | I, PU          | Initialization Select Bit 2. Select source of registerinitialization data.Bit $2 1 0$ Source $0 0 0$ $E^2$ PROM (93CS46, 93CS06) $0 0 1$ $E^2$ PROM (93CS56, 93CS66) $0 1 0$ Serial ROM 1 (TBD) $0 1 1$ Serial ROM 2 (TBD) $1 0$ IDSEL pins determine lower 6 bits of Product ID. $1 0 1$ Reserved $1 1 0$ Reserved $1 1 1$ Use default values |

| EECS/IDSEL0 | 100 | I/O, 6mA, PD   | E <sup>2</sup> PROM Chip Select/ID Select bit 0.                                                                                                                                                                                                                                                                                               |

| EESK/IDSEL1 | 99  | I/O, 6mA, PD   | E <sup>2</sup> PROM Clock/ID Select bit 1.                                                                                                                                                                                                                                                                                                     |

| EEDI/IDSEL2 | 98  | I/O, 6mA, PD   | E <sup>2</sup> PROM Write Data/ID Select bit 2.                                                                                                                                                                                                                                                                                                |

| EEDO/IDSEL3 | 97  | I, PU          | E <sup>2</sup> PROM Read Data/ID Select bit 3.                                                                                                                                                                                                                                                                                                 |

| IDSEL4      | 96  | I, PU          | ID Select bit 4.                                                                                                                                                                                                                                                                                                                               |

| IDSEL5      | 95  | I, PU          | ID Select bit 5.                                                                                                                                                                                                                                                                                                                               |

| RESET#      | 115 | I, S, PU       | <b>Reset.</b> Connect to local or power-on reset. To reset when the oscillator is stopped (initial power-up or in suspend state), assert for at least 2 ms. When oscillator is running, assert for at least five 48-MHz clock periods.                                                                                                         |

| LRESET#     | 119 | O, 6mA, TS, PU | <b>Local Reset.</b> This active low output is asserted when either the RESET# pin is asserted, or a USB upstream port reset is detected. This signal is not driven while the device is suspended, but will be pulled high by the internal pull-up resistor.                                                                                    |

| DM                | 138                              | I/O            | <b>USB Data Port.</b> DP and DM are differential data signals of the USB data port.                                                                                                                                                                                                                                                                  |

|-------------------|----------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DP                | 137                              | I/O            | <b>USB Data Port.</b> DP and DM are differential data signals of the USB data port. An external 1.5 K $\Omega$ resistor must be connected from DP to +3.3V. This pull-up resistor indicates to the host or upstream hub that a full-speed device is connected to the USB.                                                                            |

| DEVCFG#           | 117                              | O, 6mA, TS, PD | <b>Device Configured.</b> This active low output is true when the USB host has configured the NET1031. This bit is initialized to inactive (high) during reset and is set true when the host issues a Set Configuration request. This signal is not driven while the device is suspended, but will be pulled low by the internal pull-down resistor. |

| USBOE#            | 118                              | O, 6mA, TS, PU | <b>USB Port Output Enable.</b> This is an active low output that is asserted when the NET1031 is driving the USB port data lines. This signal is not driven while the device is suspended, but will be pulled high by the internal pull-up resistor.                                                                                                 |

| PWRGOOD           | 112                              | I, S, PD       | <b>Power Good.</b> This active high input indicates that an external power supply used for self-powered mode is operational.                                                                                                                                                                                                                         |

| SUSP#             | 116                              | O, 6mA, TS, PD | <b>Device Suspended.</b> This active low output is true when the USB host has suspended the NET1031. This signal is not driven while the device is suspended, but will be pulled low by the internal pull-down resistor.                                                                                                                             |

| LCLK              | 52                               | O, 6mA, TS, PD | <b>Local Clock.</b> This clock is derived from the 6-MHz crystal or oscillator connected to CLKIN. This signal is not driven while the device is suspended, but will be pulled low by the internal pull-down resistor. The USB Control Register selects the frequency of this pin (0, 6, 12, 24, 48 MHz).                                            |

| TESTOUT           | 120                              | 0              | Test Output. Leave as No Connect                                                                                                                                                                                                                                                                                                                     |

| TEST              | 111                              | I, PD          | <b>Test Mode.</b> Set to 0 for normal operation.                                                                                                                                                                                                                                                                                                     |

| XIN               | 122                              | I              | <b>6 MHz Oscillator Input.</b> Connect to 6 MHz crystal or external oscillator module.                                                                                                                                                                                                                                                               |

| XOUT              | 123                              | 0              | <b>6 MHz Oscillator Output.</b> Connect to 6 MHz crystal, or leave unconnected if using an external oscillator module. The oscillator stops when the USB Host suspends the device.                                                                                                                                                                   |

| TSTCLK            | 110                              | I, PD          | <b>PLL Test Clock</b> . Clock input for PLL testing. Set to 0 or leave as no connect.                                                                                                                                                                                                                                                                |

| TSTPLL            | 109                              | I, PD          | PLL Test Enable. Set to 0 or leave as no connect.                                                                                                                                                                                                                                                                                                    |

| ENHI              | 108                              | I, PU          | <b>PLL Enable</b> . Set to 0 to bypass the PLL. In this case, an external 48 MHz signal must be applied to the XIN input.                                                                                                                                                                                                                            |

| VDDPLL            | 107                              | Pwr            | PLL Supply Voltage. VDDPLL = 3.3V                                                                                                                                                                                                                                                                                                                    |

| VSSPLL            | 104                              | Gnd            | PLL Supply Voltage. VSSPLL = GND                                                                                                                                                                                                                                                                                                                     |

| VIN               | 106                              | Ι              | <b>PLL Filter Input</b> Connect to VOUT with an RC ( $46K\Omega$ , $64pF$ ) to ground.                                                                                                                                                                                                                                                               |

| VOUT              | 105                              | 0              | PLL Filter Output                                                                                                                                                                                                                                                                                                                                    |

| VDD<br>(VDDCORE)  | 39, 76, 121,<br>136              | Pwr            | <b>Core Supply Voltage.</b> VDD = 3.3V                                                                                                                                                                                                                                                                                                               |

| VDDL<br>(VDDSCAN) | 7, 20, 31,<br>53, 63, 87,<br>129 | Pwr            | Scanner-side Supply Voltage. Dual voltage, VDDL = 3.3V or 5.0V                                                                                                                                                                                                                                                                                       |

#### **Preliminary Specification**

#### NET1031 USB Scanner Controller

| VSS | 8, 21, 32,<br>40, 54, 64,<br>77, 88, 124,<br>130, 139       | Gnd | Device Ground.                         |

|-----|-------------------------------------------------------------|-----|----------------------------------------|

| NC  | 14, 38, 51,<br>69, 78, 89,<br>94, 113,<br>114, 125,<br>140, |     | No Connect. Do not connect these pins. |

Note: All TS and I/O pins are tri-stated during the Suspend state.

# 4 Functional Description

# 4.1 Start-Up

Before the NET1031 is ready to perform scanning functions, a sequence of operations must occur, involving the NET1031, the USB driver stack, and the host Scanner driver. First, the NET1031 reads required USB parameters from the external serial memory device. Next, the USB driver stack must enumerate the NET1031. Finally the host scanner driver configures the NET1031 with the correct parameters for the scanner.

# 4.1.1 Reading from Initialization Device

When the NET1031 first comes out of a reset applied at its RESET# input pin or provided by the USB host, it reads various parameters required by the USB host from an external serial memory. The INITSEL[2:0] pins determine the source of the initialization parameters. The NET1031 generates all signals necessary to read the data from the serial memory, so no interaction is required from the scanner hardware. Until this data is read, the NET1031 will respond to host requests for a configuration descriptor or device descriptor with a NAK. If no valid serial memory device is installed, then either the default values are used, or the lower six bits of the product ID can be modified using the IDSEL input pins. These options are selected using the INITSEL[2:0] pins.

# 4.1.2 Enumeration by the Host PC

USB defines a set of descriptor requests and calls that are part of the enumeration process. The NET1031 responds to these requests. When enumeration is complete, the USB host will perform a "Set Configuration" request, which signals the end of the enumeration process. The NET1031's DEVCFG# output pin will activate. At that point, control over the NET1031 is passed to the host scanner driver.

As part of the enumeration process, the USB host issues a Get Device Descriptor request, which the NET1031 answers with various parameters, including the Vendor ID and Product ID read from the external serial memory. This Vendor ID and Product ID allow the host to associate the vendor-supplied scanner driver with the NET1031.

# 4.1.3 Configuration by the Scanner Driver

Before a scan may be performed, the host PC's scanner driver must configure the NET1031. The registers programming the PWM signals and other parameters must be initialized. Any register for which the default values are not appropriate should be set.

# 4.1.4 Global Calibration

An optional step is to perform Global Calibration. Global Calibration should be performed once when the scanner is plugged into a PC for the first time. Subsequent calibrations are optional, since the calibration data may be stored in the Host PC after the first time, and downloaded to the scanner on subsequent plug-ins.

#### 4.2 Initialization Interface

The NET1031 can be initialized at reset time from several sources, selected by the INITSEL[2:0] bits. The initialization must be completed before the NET1031 will respond to Device Descriptor requests from the host.

| INITSEL[2:0] | Source                               |

|--------------|--------------------------------------|

| 0            | E <sup>2</sup> PROM (93CS06, 93CS46) |

| 1            | E <sup>2</sup> PROM(93CS56, 93CS66)  |

| 2            | Reserved                             |

| 3            | Reserved                             |

| 4            | IDSEL Pins                           |

| 5            | Reserved                             |

| 6            | Reserved                             |

| 7            | Default                              |

# 4.2.1 E<sup>2</sup>PROMs (93CS06, 93CS46, 93CS56, 93CS66)

The 93CS06 (32 bytes), 93CS46 (128 bytes), 93CS56 (256 bytes), or the 93CS66 (512 bytes), can be used to initialize registers in the NET1031. Each of these devices has a 4-wire MicroWire<sup>TM</sup> serial interface. After reset is negated, the INITSEL bits are sampled to determine the source of the initialization information. If INITSEL[2:0] = 0 or 1, then the NET1031 will determine if a non-blank E<sup>2</sup>PROM is connected. If no E<sup>2</sup>PROM is detected, or the device is blank (first word is FFFF), then the default register values will be reported to the Host PC. Otherwise the following required fields are loaded into the NET1031 from the E<sup>2</sup>PROM. These required fields are reported in the Device and Configuration descriptors during USB device enumeration. Information is stored in the EEPROM as 16-bit words. For string descriptors, bits 7:0 of an EEPROM word are returned to the host first, followed by bits 15:8.

| Word          | Contents                                                                      | Default Value                  |

|---------------|-------------------------------------------------------------------------------|--------------------------------|

| Index         |                                                                               |                                |

| 0             | Vendor ID. This field is reported to the Host PC in the USB device            | 0x0525                         |

|               | descriptor's "Vendor ID" field during enumeration.                            |                                |

| 1             | Product ID. This field is reported to the Host PC in the USB device           | 0x1031                         |

|               | descriptor's "Product ID" field during enumeration.                           |                                |

| 2             | <b>Revision ID.</b> This field is reported to the Host PC in the USB device   | 0x <i>rrrr</i> , <i>rrrr</i> = |

|               | descriptor's "Revision ID" field during enumeration.                          | Silicon Rev #                  |

| 3             | Max Power. This field is reported to the Host PC in the USB configuration     | 0x0032                         |

|               | descriptor's "Max Power" field during enumeration. It is reported in units of |                                |

|               | 2mA. This field should reflect the maximum current drawn by the scanner       |                                |

|               | from the USB power pins.                                                      |                                |

| 4             | USB Features 1. This field breaks down into several control bits that are     | 0x0103                         |

|               | reported to the Host PC in the USB device descriptor and configuration        |                                |

|               | descriptor. See USB Control Register 1 for details.                           |                                |

| 5             | USB Features 2. This field breaks down into several control bits that are     | 0x0001                         |

|               | reported to the Host PC in the USB device descriptor and configuration        |                                |

|               | descriptor. See USB Control Register 2 for details.                           |                                |

| 6 (bits 15:8) | Language ID String Start Index.                                               | 0x0000                         |

| 6 (bits 7:0)  | Manufacturer String Start Index.                                              | 0x0000                         |

| 7 (bits 15:8) | Product String Start Index.                                                   | 0x0000                         |

| 7 (bits 7:0)  | Serial Number String Start Index.                                             | 0x0000                         |

| Table 4-1: Required | Serial E <sup>2</sup> PROM Fields |

|---------------------|-----------------------------------|

|---------------------|-----------------------------------|

In addition, if any "String Enable" fields are set in **USB Control Register 2**, the fields in Table 4-2 must be defined.

| Word Index | Contents                                                                                |

|------------|-----------------------------------------------------------------------------------------|

| 8-9        | <b>Reserved.</b> Write these words as a zero.                                           |

| 0Ah-FFh    | Available. This range of the serial EPROM is available for defining string descriptors. |

#### Table 4-2: Additional Serial E<sup>2</sup>PROM Fields for String Descriptors

If no string descriptors are used, the  $E^2$ PROM image may be as short as 8 words (to provide the required fields to the Host PC). With string descriptors, the  $E^2$ PROM can end at the end of the last string descriptor's definition.

The MicroWire EEPROMs can be accessed from host using the EEADDR and EEDATA registers. For an EEPROM write, the host first writes the data to the EEDATA register. Then the write is initiated by writing the EEPROM address, Read/Write bit, and Start bit to the EEADDR register. The host may then poll the Start bit until it is cleared, indicating that the write operation is complete.

An EEPROM read is initiated by writing the EEPROM address, Read/Write bit, and Start bit to the EEADDR register. The host may then poll the Start bit until it is cleared, indicating that the read operation is complete. The data is then read from the EEDATA register.

For EEPROMs that are not MicroWire compatible, the host can directly manipulate the EEPROM control signals using the EECTL register. Note that the EEPROM control signals are enabled only if the INITSEL pins are not set to 4.

#### 4.2.2 IDSEL Pin Initialization

If INITSEL[2:0] = 4, then the least significant 6 bits of the idProduct field in the device descriptor are determined by the IDSEL[5:0] pins. All other initialization values are left in the default state.

# 4.3 Scanner Functions

#### 4.3.1 CCD/CIS Control

The NET1031 can control a wide variety of CIS and CCD sensors. The CIS and CCD control signals are programmable pulse width modulated (PWM) signals. See Section 9 for a description of the PWM signals.

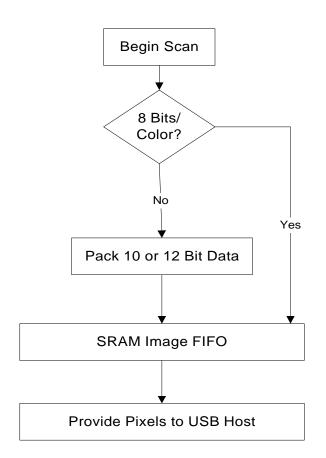

#### 4.3.2 General Data Flow

#### **Figure 4-1: General Image Data Flow**

# 4.3.3 Analog Block Interface

Analog image acquisition support signals are also generated using pulse-width modulation (PWM) techniques. PWM signals, in conjunction with an external RC circuit, provide a mechanism for generating digital control signals and analog voltages to control the analog block. Signals such as Gain and Offset can therefore be specified at analog voltage levels. See Section 9 for a description of the PWM signals.

#### 4.3.4 Stepper Motor Control

The NET1031 can control a variety of stepper motors. The enable, disable, and voltage reference selector signals for two phases are present and fully programmable as PWM signals.

#### 4.3.5 Image Buffering in SRAM

Image data, once it is scanned, is placed in the external SRAM by the NET1031 to be queued for transmission over USB. The SRAM allows the scanner to continue a scan in progress if a host PC temporarily slows in reading data from the NET1031. The NET1031 supports the following memory configurations:

| SRAM<br>Type | Max Number<br>of Rams | Total Max<br>Memory | Buffering* |

|--------------|-----------------------|---------------------|------------|

| 32Kx8        | 4                     | 128K                | 116 msec   |

| 128Kx8       | 4                     | 512K                | 509 msec   |

| 512Kx8       | 4                     | 2M                  | 2.08 sec   |

• Assume a typical scenario of 24 bits per pixel at a rate of 3 usec per pixel. The SRAM buffer is able to store pixel data for the time period shown in the chart, and is calculated as follows:

Buffering time = (Max Memory) \* (8/bits per pixel) \* (pixel time) = (83K) \* (8/24) \* (3usec) = 83 msec

- At 36 bits per pixel, the buffering time is:

- Buffering time = (Max Memory) \* (8/bits per pixel) \* (pixel time) = (83K) \* (8/36) \* (3usec) = 55 msec

The SRAM buffer generally does not contain enough memory to store an entire image, so on average the Host PC must accept data at a rate greater than or equal to the scan rate. If this condition is not met, the SRAM buffer may fill. At that point, the NET1031 will have to slow and/or stop the scan operation while waiting for room to become available in the SRAM. The NET1031 can adjust the scanning speed to half speed, or stop as it approaches multiple threshold levels of memory filled in the SRAM.

# 4.3.6 General I/O Pins

The NET1031 includes 8 general input/output pins. Each of these eight pins may be independently configured as digital inputs, digital outputs, or PWM outputs. Outputs may be totem-pole or open-drain. When configured as PWM outputs, four General I/O pins (GIOLINE0-GIOLINE3) can have transitions programmed in units of scanlines, while four pins (GIOPEL0-GIOPEL3) can have transitions programmed in units of pixel timing. When configured as inputs, the value of the eight pins may be read from the General I/O registers. Some potential uses of these pins are:

- Paper Out: input asserted when a sheet of paper has moved out of the scanner (from auto-feed system).

- Paper In: input asserted when a sheet of paper is in the scanner.

- Restore Sensor: input asserted when the scanhead of a flatbed scanner has restored to the home position.

- Page Feed: output to cause an auto-feeder to feed the next page into the scanner.

- Serial A/D Controls: outputs that allow analog-to-digital converter control registers to be written using a serial protocol.

- Start Scan: In a push model, this input from a front panel pushbutton could cause a scanning application to start.

#### Preliminary Specification

• Front Panel LED: Output to cause an LED to be illuminated when USB communications are established.

#### 4.3.7 Abort# Pin

When this active low input is asserted, a status bit is set which indicates to the host that it should stop the scan. Also, the **Enable Stepper and Enable Pixel Processing** bits in the MASTERCTL register are cleared. When **Enable Stepper** is cleared, the stepper control output pins are returned to their default state.

# 4.4 USB Interface

The interface from the NET1031 to USB allows the Host PC to accept scanned data, access registers, read and write SRAM data, perform I/O operations, and control the scanner operation.

#### 4.4.1 Default Control Pipe (Endpoint 0x00)

Endpoint 0 is a bi-directional USB control endpoint which processes 8-byte packets to/from the Host PC. Each packet is decoded and USB control read and write 'requests' are handled automatically. Endpoint 0 supports the required USB protocol read and write requests (e.g. descriptor reads), as well as vendor-specific extensions. The vendor-specific extensions provide the capability to read and write registers and perform external I/O read and write operations.

# 4.4.2 SRAM Write Pipe (Endpoint 0x01)

Endpoint 0x01 is a USB bulk OUT endpoint that accepts packets up to 64 bytes in length. The SRAM Write Endpoint will write data received to this endpoint to the SRAM beginning at the address specified by the **SRAMADDR** register. The **SRAMADDR** register is auto-incremented as the data is written.

# 4.4.3 SRAM/Image Data Read Pipe (Endpoint 0x81)

Endpoint 0x81 is a USB bulk IN endpoint which will transmit packets of 64 bytes. A bit in the MASTERCTL configuration register, EP81 Mode, determines the source of data for this endpoint. When the EP81 Mode bit is low, this endpoint responds to an IN token with scanned image data from the external SRAM FIFO, as it becomes available. When the EP81 Mode bit is high, this endpoint responds to an IN token with 64 bytes of SRAM data, beginning at the address specified by the **SRAMADDR** register. The **SRAMADDR** register is auto-incremented as the data is read.

#### 4.4.4 Status Input Pipe (Endpoint 0x82)

Endpoint 0x82 is a USB interrupt IN endpoint that transmits status information each time it is polled by the USB host. The transmitted information is:

Byte 0 : SCANCHG register (LSB) Byte 1 : SCANCHG register (MSB) Byte 2 : IOCHG register (LSB) Byte 3 : IOCHG register (MSB)

# 4.5 I/O Space Access

To support external programmable components, the NET1031 can write and read data by providing generic I/O bus signaling. RD# and WR# strobes are also provided, as well as an IOCS# signal to indicate that we are currently operating in I/O space. When the Host PC issues a request to write to an I/O address, the NET1031 issues a 15-bit address from the SRAMADDR[14:0] pins. Bit 15 of the address is used to select between internal register accesses and external I/O accesses. If **IO Space Data Bus Select** in the **MEMIOCTL** register is low, the upper 12 bits of data are driven out on the SCANDATA[11:0] pins. For read cycles, if **IO Space Data Bus Select** is high, the lower bits of data are driven out on the SRAMDATA[7:0] pins. For read cycles, if **IO Space Data Bus Select** is low, the data is read in from the SRAMDATA[7:0] pins and returned in the most significant 12 bits. If **IO Space Data Bus Select** is high, the data is read in from the SRAMDATA[7:0] pins and returned in the least significant 8 bits.

# 4.6 Suspend Mode

When there is a three-millisecond period of inactivity on the USB, the USB specification requires a device to enter into a low-power suspended state. While in this state the device may not draw more than 500  $\mu$ A of current from the USB connector's power pins. To facilitate this, the NET1031 automatically enters the suspend state after detecting the three millisecond period of inactivity. Additionally, the NET1031 allows local bus hardware to initiate a "device remote wake-up" to the USB. When a suspend state is detected, a scan in progress will be aborted at the end of the current line.

# 4.6.1 The Suspend Sequence

The typical sequence of a suspend operation is as follows:

- During device configuration, a bit is set in the USB Control register which enables the suspend feature. (Devices which are self-powered may not need the NET1031 to enter the suspend state)

- When the USB is idle for three milliseconds, the NET1031 enters the suspend state, if enabled.

In the suspended state, the NET1031's oscillator shuts down, and most output pins are tri-stated to conserve power (see section 3, **Pin Description**). As the NET1031 enters the suspend state, the SUSP# output pin will be driven low for 20 nsec and then floated. It has an internal pull-down resistor to keep it low during suspend. Note that input pins on the NET1031 which do not have an internal pull-up or pull-down resistors should not be allowed to float during suspend mode. The NET1031 will leave suspend mode by detecting a host initiated wake-up or by a device remote wake-up.

#### 4.6.2 Host-Initiated Wake-Up

The host may wake up the NET1031 by driving any non-idle state on the USB. The NET1031 will detect the host's wake-up request, and re-starts its internal oscillator. Two milliseconds later, the SUSP# output signal is driven high to indicate that the NET1031 has completed its wake-up.

#### 4.6.3 Device-Remote Wake-Up

The device hardware signals a device remote wake-up by driving one of the GIOPEL or GIOLINE pins to the active state. The GIO pin and polarity are set in the USB Control Register. If the **Device Remote Wake-up Enable** bit is set, the NET1031 will send a 10-ms wake-up signal to the USB host, and concurrently re-start its local oscillator. Two milliseconds after the wakeup pin is asserted, the SUSP# line is driven high to indicate that the NET1031 has completed its wake-up.

# 4.7 Root Port Reset

If the SIE in the NET1031 detects a single-ended zero on the root port for greater than 2.5 microseconds, it is interpreted as a root port reset. The LRESET# output pin is asserted, and the following resources are reset:

- SIE

- USB state machines

- Scanner state machines

- **Device Configured** output pin, DEVCFG#

- All configuration registers

## 4.8 NET1031 Power Configuration

The USB specification defines both bus-powered and self-powered devices. A *bus-powered* device is a peripheral that derives all of its power from the upstream USB connector, while a *self-powered* device has an external power supply. The NET1031 is well suited for both types of applications.

The most significant consideration when deciding whether to build a bus-powered or a self-powered device is power consumption. The USB specification specifies the following requirements for maximum current draw:

- A peripheral not configured by the host may draw only 100 mA from the USB power pins.

- A device may not draw more than 500 mA from the USB connector's power pins.

- In suspend mode, the peripheral may not draw more than 500 µA from the USB connector's power pins

If these power considerations can be met without the use of an external power supply, the peripheral can be buspowered; otherwise a self-powered design should be implemented.

#### 4.8.1 Bus-Powered Device

If the scanner signals are powered at 3.3 Volts, the  $V_{DD}$  and  $V_{DDL}$  pins of the device are connected to a 3.3 Volt regulated source derived from the USB 5.0 volt power pin. For 5.0 volt scanner signals, the  $V_{DDL}$  pin may be connected directly to the USB 5.0 Volt power pin, while the  $V_{DD}$  pins must still be connected to 3.3 Volts through a regulator. The rest of the scanner-side circuitry is also connected to the USB power pin, either through a regulator or directly. Therefore, the peripheral's scanner circuitry and the NET1031 will all power up simultaneously, and initialization can occur normally with a power-on reset.

# 4.8.2 Self-Powered Device

Generally, a peripheral with higher power requirements will be self-powered. In a self-powered device, the NET1031  $V_{DD}$  and  $V_{DDL}$  pins are powered by the device power supply. The USB connector's power pin is connected only to the 1.5 K $\Omega$  pull-up resistor on DP.

# 5 Register Descriptions

The NET1031 contains a 256 x 16-bit local register space that can be accessed by the Host over USB using Endpoint 0. When the NET1031 receives a RESET signal from the RESET# pin or from a USB RESET command, the registers are set to their default values.

Writes to reserved registers are ignored, and reads from reserved registers return a value of 0. For compatibility with future revisions, unused bits within a register should always be written with a zero.

| Address<br>Range | Register Set                                                                                   | Register Set Description                                     |

|------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 00 h - 2F h      | Control                                                                                        | Control, Configuration, and Status Registers.                |

| 30 h - 3F h      | (Reserved)                                                                                     | Reserved for future use                                      |

| 40 h - 8F h      | Pixel-based waveforms                                                                          | Configuration registers for pixel-based programmable signals |

| 90 h - CF h      | Line-based waveforms                                                                           | Configuration registers for line-based programmable signals  |

| D0 h - EF h      | D0 h - EF h Stepper-based waveforms Configuration registers for stepper-based programmable sig |                                                              |

| F0 h - FF h      | USB                                                                                            | USB Descriptor registers                                     |

Registers are organized in the address space according to function, as shown below:

# 5.1 Control Registers Description

#### 5.1.1 Control Registers Summary

| Address     | Register Name | Register Description           |

|-------------|---------------|--------------------------------|

|             |               |                                |